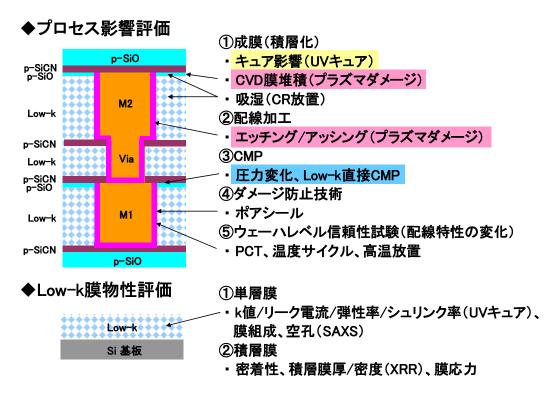

## Ⅲ. 2.14 UV キュアによる積層膜への応力影響の評価

従来の成膜技術である熱キュアプロセスに比べて、UV キュアはキュアの温度や時間の変化に伴って膜シュリンク率が大きく増加する。膜シュリンク率の増加により引張り応力が増加して、膜の剥離やクラックが発生したり、チップの信頼性が低下することが懸念される為、膜応力や反り量に及ぼす UV キュアの影響を評価する。材料としては、UV キュアに対する感度が高く、UV キュア時間によって大きく膜物性が変化するE11105(ポーラス MSQ、k=2.4)とE11097(ポーラス MSQ、k=2.3)を使用した。

·E11105 の UV キュア条件

・光源(バルブ): RC-08 (波長はブロードバンド)

·ステージ温度(キュア温度):400℃

・キュア時間:50 秒、2 分 50 秒、8 分

以降、E11105 に関しては、50 秒を「短時間キュア」、2 分 50 秒を「基準条件」、8 分を「長時間キュア」と記載する。

·E11097 の UV キュア条件

・光源(バルブ): RC-08 (波長はブロードバンド)

·ステージ温度(キュア温度):400℃

•キュア時間:1分、6分、30分

以降、E11097に関しては、1分を「短時間キュア」、6分を「基準条件」、30分を「長時間キュア」と記載する。 Low-k 膜物性の UV キュア時間依存性を表 III.2.1.4.1に示す。

表Ⅲ.2.1.4.1 Low-k 材料の UV キュア時間と膜物性

| 提案材料(膜厚:100nm) ur  |               | unit     | 評価方法         | E11105<br>(ポーラスMSQ) |      |            | E11097<br>(ポーラスMSQ) |      |            |

|--------------------|---------------|----------|--------------|---------------------|------|------------|---------------------|------|------------|

|                    |               |          |              | 1min                | 3min | 10min      | 1min                | 6min | 30min      |

| UVキュア時間(400℃_XXmin |               | )        |              | 短時間<br>キュア          | 基準条件 | 長時間<br>キュア | 短時間<br>キュア          | 基準条件 | 長時間<br>キュア |

| 膜シュリンク率 %          |               | %        | エリプソメトリー     | 4                   | 10   | 20         | 2                   | 5    | 11         |

| 電気特性               | 誘電率           |          | 水銀プローブ法      | 2.40                | 2.42 | 2.57       | 2.47                | 2.33 | 2.33       |

|                    | リーク電流(3MV/cm) | e-9A/cm2 | 水銀プローブ法      | 21.0                | 4.1  | 1.2        | 4.0                 | 1.8  | 1.2        |

| 機械特性               | 弾性率           | GPa      | ナノインデンテーション法 | 6.2                 | 9.4  | 13.8       | 6.6                 | 8.3  | 13.1       |

|                    | 応力            | MPa      | 室温、反り測定      | 96                  | _    | 88         | 25                  | 42   | 69         |

青字: 膜厚150nm(E11102)での物性値。 黒字: 膜厚100nm(E11105)での物性値。

※なお、E11105 は膜シュリンク率が大きいため、膜厚仕様が 150nm の E11102 と 100nm の E11105 で UV キュア時間を変更した。表中の UV キュア時間は E11102(膜厚 150nm)用の条件であり、E11105 (膜厚 100nm)では同じ膜シュリンク率を得るキュア時間は 50 秒、2 分 40 秒、8 分となる。

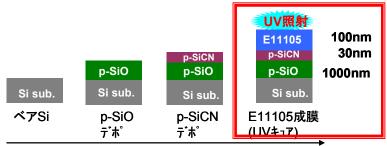

#### 皿. 2.14.1 評価サンプル構造

<積層膜のサンプル構造>

実配線での影響を把握するため、実際に2層配線を試作する際の膜厚で積層膜サンプルを作成する。

# プロセスの流れ(M1のE11105成膜まで)

図皿.2.1.4..1 評価サンプルの構造 <積層膜>

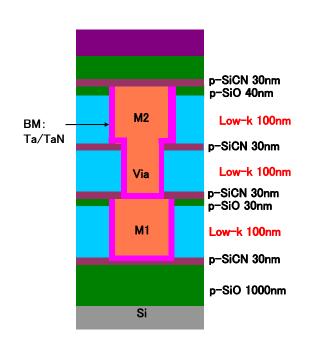

## <2 層配線の配線構造>

基準プロセスに従って配線を試作する。

| 層間0    | p-SiOデポ                                                                               |

|--------|---------------------------------------------------------------------------------------|

| M1(Cu) | p-SiCNデポ  Low-k成膜(UVキュア) Cap_p-SiOデポ パターン形成 バリアンタル・Cuシードデポ Cuメッキ CMP                  |

| via    | p-SiCNデポ<br><i>Low-k成膜(UVキュア)</i>                                                     |

| M2(Cu) | p-SiCNデポ<br>Low-k成膜(UVキュア)<br>Cap_p-SiOデポ<br>パターン形成<br>バリアンタル・Cuシードデポ<br>Cuメッキ<br>CMP |

| Pro    | p-SiCNデポ<br>p-SiOデポ<br>パターン形成                                                         |

| M3(AL) | PVD(Ti/AL)デポ<br>パターン形成                                                                |

| PV     | p-SiCNデポ<br>p-SiNデポ<br>パターン形成                                                         |

図Ⅲ.2.1.4.2 評価サンプルの配線構造と配線試作のプロセスフロー <2 層配線>

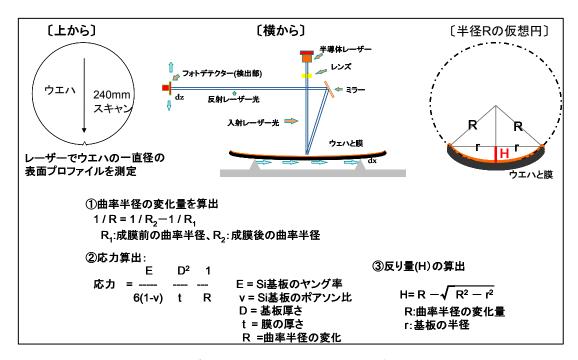

## Ⅲ. 2.14.2 応力およびウェーハ反り量の測定方法

## (1)測定装置

薄膜応力測定装置:FSM900TC-vac(FSM 社製)

## (2)測定条件

測定波長:750nm

スキャンサイズ:240mm 測定温度:室温(25℃)

## [測定手順]

- ① Low-k 材の成膜前/後で曲率半径を測定する。

- ② 図III.2.1.4.3 のストーニーの式により、応力(σ)を算出する。

③ 同様に、図Ⅲ.2.1.4.3 に記載の通り、反り量(H)を算出する。

### 〔測定上の注意〕

2 層配線試作時の応力・反り量を評価する場合、配線加工面で測定するとレーザーが散乱するため、ウェーハを裏返して鏡面加工された裏面を使って評価する。

図皿.2.1.4.3 レーザースキャン方式による応力及びウェーハ反り量測定概要

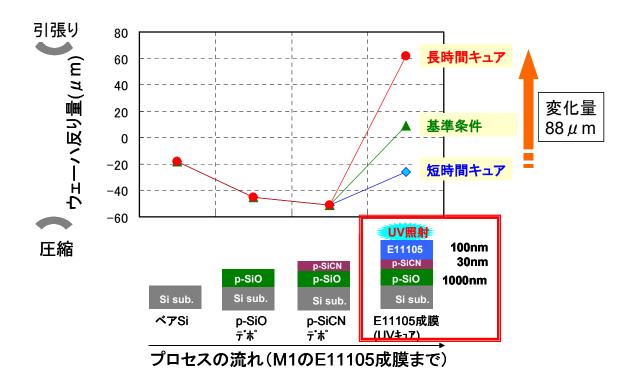

(3)ウェーハ反り量の UV キュア時間依存性

キュア時間の検討幅は評価対象材料により異なるが、30min 程度までキュア時間を振って、UV キュア時間と積層膜でのウェーハ反り量の関係を把握し単層膜での反り量から考察する。

(4)2 層配線試作において、工程(プロセス)毎にウェーハ反り量を測定することにより、応力変化の大きな プロセスとプロセス上の問題点を抽出する。

## Ⅲ. 2.14.3 測定結果

(1)積層膜を用いた UV キュアによる応力および反り量変化

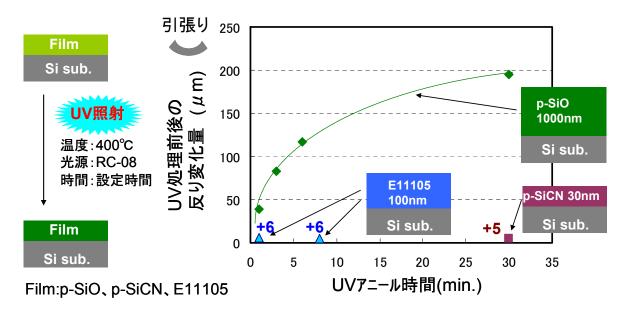

図Ⅲ.2.1.4.4 に、E11105を用いて積層膜を作製し、UV キュアによるウェーハ反り量の変化を調べた結果を示す。p-SiO や p-SiCN 膜の膜応力は圧縮方向なので、Si 基板上に p-SiO 膜および p-SiCN を成膜することでウェーハは圧縮方向に反る。次に E11105を塗布し UV キュアすると反り量が引張方向に大きく変化することがわかる。UV キュア時間に伴って変化量は増大し、3min 以上の UV キュアによりウェーハの反りは引張方向に変化している。

表 II.2.1.4.1 によると UV キュア時間を長くしても E11105 の膜応力に大きな差が見られないことから、 E11105 の UV キュアにより p-SiCN や p-SiO が変化していると考えられる。

図Ⅲ.2.1.4.4 積層膜を用いた UV キュア時間とウェーハ反り量の関係

そこで Low-k 周辺膜である p-SiO と p-SiCN を UV キュアしてウェーハ反り量を調べた。その結果を図 II.2.1.4.5 に示す。 P-SiO や p-SiCN も E11105 と同様、 UV キュアによってウェーハは引張方向に反ることがわかる。 そして P-SiO のウェーハ反りの変化量は膜厚が厚いこともあり E11105 や p-SiCN に比べて非常に大きいことから、 積層膜での UV キュア時のウェーハ反り量が変化した主要因は p-SiO の引張応力によるものであり、 E11105 を UV キュアする際に UV が下層の p-SiO まで透過していることが示唆される。

図Ⅲ.2.1.4.5 p-SiO および p-SiCN の UV キュア時間とウェーハ反り量の関係

## (2)2 層配線構造を用いた UV キュアによる応力および反り量変化

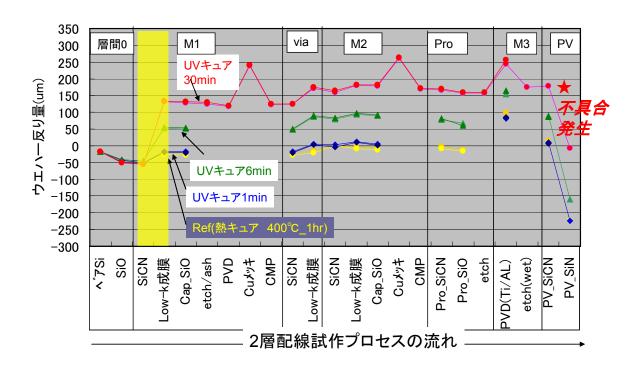

図皿.2.1.4.6 に E11097 を用いて 2 層配線を試作し、工程(プロセス)毎にウェーハ反り量を調べた結果を示す。2 層配線を試作する際、Low-k 成膜、Cu メッキ、AL デポ、パッシベーション膜である p-SiN デポの4 プロセスでウェーハ反り量が大きく変化する。ただし、Cu メッキは CMP で、AL デポは etch(wet)で反りが戻るので、Low-k 成膜と p-SiN デポのプロセスが反り量変化の支配要因である。

Low-k 成膜プロセスでは、UV キュアの時間による影響が非常に大きい。また、同じキュア時間で M1 層、Via 層、M2 層の Low-k 成膜プロセスを比較すると、反り量の変化は M1 層 > Via 層 > M2 層であることから、M1 層の Low-k 成膜プロセスで 2 層配線試作時のウェーハ反り量はほぼ決まっていることがわかる。UV キュアプロセスで反り量が大きく変化する理由は Low-k 膜の下に存在する p-SiO や p-SiCN などの絶縁膜がUV 透過光によってシュリンクした為と考えられる。

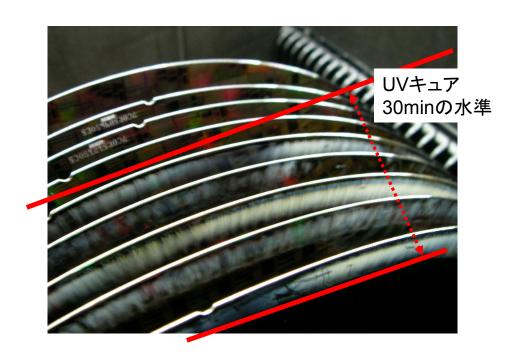

図皿.2.1.4.7 に UV キュア時間が 30min の水準で見られたプロセス上の問題を示す。CVD のステージとウェーハ裏面に隙間ができて、パッシベーション膜の p-SiN デポの原料(ガス)が裏面に回りこんだ現象であり、反り量増大により生じた不具合(課題)である。

図Ⅲ.2.1.4.6 2 層配線の工程(プロセス)とウェーハ反り量の関係

図Ⅲ.2.1.4.7 長時間キュアで見られたウェーハ裏面への回り込み

#### くまとめ>

#### ・UV キュアと膜応力の評価手法について

図皿.2.1.4.4 の積層膜での反り量変化から、UV キュア時間が長くなるとウェーハの反り量が引張り方向に大きく変化することがわかった。また、表皿.2.1.4.1 に示す Low-k 膜単体のウェーハの反り量ではこの大きな変化を説明できないこと、及び、図皿.2.1.4.5 に示す Low-k 膜の下層に存在する p-SiO や p-SiCN がUV 照射により大きく反ることから、本評価によってUV 透過というプロセス上の課題が抽出された。そこで、p-SiO 膜への UV 透過光の影響度を図皿.2.1.4.4 および図皿.2.1.4.5 の結果から試算する。まず、図4からUV キュア前後の反り量変化を抽出し、図皿.2.1.4.5 のp-SiO のチャートから、抽出した反り量変化に相当する UV 照射時間を見積もる。その結果、p-SiO での相当照射時間は、UV 短時間キュア(50 秒)では 38 秒、基準条件(2 分 40 秒)では 1 分 24 秒、長時間キュア(8 分)では 4 分となり、Low-kを UV キュアする際に、ほぼ半分相当の UV が下層の p-SiO に透過していることが試算された。このようにウェーハ反り量測定は、下層膜への UV 透過の影響の確認や、UV 透過を抑制するための材料開発、プロセスの改善などに有用な評価手法と思われる。

## ・多層配線形成への影響に関して

2 層配線試作での反り量変化から、ウェーハ反り量変化の経緯と UV キュアの影響度を把握し、CVD デポでの裏面への回りこみという多層配線試作でのプロセス不良(課題)を抽出した。

今回の結果では CVD デポ時の裏面への回りこみはウェーハ反り量が 170  $\mu$  m 程度で発生しており、多層配線形成での反り量(応力)コントロールにおける指標の一つと考える。ただし、CVD での裏面への回り込み不良は UV 透過光による p-SiO の膜シュリンクが最大要因であることから、下層 p-SiO の薄膜化により回避可能と思われる。

## Ⅲ. 2.15 Low-k 膜の空孔率、ポア径評価

Low-k 材料のさらなる低誘電率化のためには材料組成のみの研究開発では限界があるとみられており、 Micro Pore を導入した Porous 構造によって低誘電率化を実現する方法が提案されている。 Low-k 膜の 空孔(ポア)は膜強度、誘電率、プロセス耐性に相関がある事が知られている。空孔の有無、サイズ、分布 を高精度に測定する評価基準を作成する。

# (1)評価項目

SAXS 法(Small Angle X-ray Scattering)による Low-k 膜ポア径の測定。

測定データの比較のためポア径の測定には陽電子消滅・空孔計測法(以下 PALS Positron Annihilation Lifetime Spectroscoy と略す)も用いるほうが望ましい。

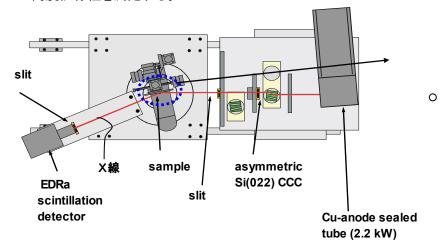

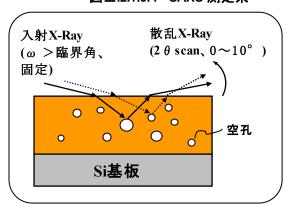

## SAXS スペクトルの測定

図皿.2.15.1に SAXS 測定系を示す。 試料に図皿.2.15.2 に示したように低角度で X 線を入射させる。この場合の入射角度は Low-k 膜の臨界角 < 入射角 < Si ウェーハの臨界角とする。 Low-k 膜で散漫散乱された X 線強度の2 $\theta$  角度依存性を測定する。

図Ⅲ.2.1.5.1 SAXS 測定系

図皿.2.15.2 散漫散乱測定

## 測定用 Script

装置 Alignment 用 Metrixl alignment V3.3 SAXS 測定用 Porosity center with chi

測定は試料とともに Bare-Si ウェーハ(Low-k 膜なし)での SAXS スペクトルを測定する。これは試料 SAXS スペクトルに混入している Si ウェーハからの SAXS スペクトル成分を差し引くためである。

## (2)PALS 法でのポア径測定結果の比較

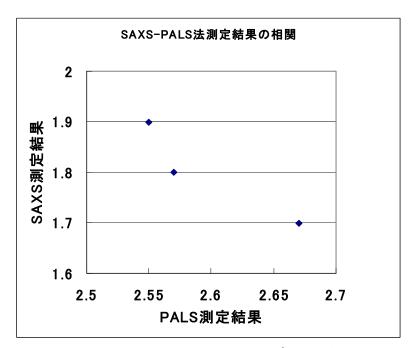

数種類のLow-k膜を用いてSAXS法とPALS法によるポア径測定結果の相関を調べた結果を図皿.2.15.3 に示す。 SAXS 法で測定したポア径は PALS 法測定結果に比べ 30%程度小さいことが分かった。評価点が少ないが SAXS 法測定結果と PALS 法の測定結果には正の相関が認められない。この原因としては両測定法間で検出対象のポア形態がことなることも考えられる。 この点に関しては今後検討していきたい。

図Ⅲ.2.15.3 SAXS 法と PALS 法によるポア径測定結果の相関

## Ⅲ. 2.1.6 単層膜を用いたポアシール効果

Low-k 材は比誘電率低下のため膜中に空孔を持たせ膜密度を低下させている。 空孔(以下ポアとも記す)を有する Low-k 材を用いた Cu 配線プロセスにおいては膜表面とともにトレンチ、ビア側壁に空孔が露出するため、Cu 配線下層のバリアメタルの浸透や大気中の水分、Cu メッキ工程のウェット洗浄液、エッチング時のプラズマガスの浸透などによる比誘電率の増加、TDDB 寿命などの配線信頼度低下が懸念される。 これらの問題回避のため Low-k 膜表面の空孔を埋めるポアシール技術が広く評価されている。各種ポアシール法の効果評価には BEOL(Back End of Line)プロセスから受ける種々の影響を含んだ Cu2層配線構造試料での電気特性への影響、配線信頼度への影響評価を行う必要がある。各種 Low-k 単層膜における各種ポアシール法の評価法を確立することを目的として実験をおこなった。平成18年度にプラズマCVD 装置をクリーンルームに設置した。この装置は、本助成事業推進のため、NEDO より借用したものである。この装置を用いて各種 Si 系絶縁膜の薄膜形成条件の設定し、独立行政法人、産業技術総合研究所との技術協力を得てPALS 法(陽電子寿命測定法)による porous Low-k 材料の空孔率、ポア径分布、空孔の連結性の測定をおこなった。

#### 皿. 2.1.6.1 評価項目

Low-k 膜への外部からのガス、水分などの侵入を阻止することを目的とし,本基準書では以下の2方式のポアシール法を取り上げる。

- (1)Low-k 膜表面を緻密な薄膜で覆い外部からのガス、水分などを阻止する方法

- (2)Low-k 膜表面のスパッタエッチング処理による Low-k 膜表面の緻密化およびスパッタエッチングされた物質を Low-k 膜表面に再付着させる方法

上記2方法のポアシール効果に関し本基準書で評価する項目は以下のとおりである。

- (1)Low-k 膜ポアサイズが外部からの金属浸透阻止能力を評価するための方法評価

- (2)ポアシール膜のポアシール基本性能評価(ポアシール膜のポア径評価)

- (3)ポアシール膜の膜種、膜厚のポアシール効果依存性の評価

## 皿. 2.1.6.2 試料作成手順

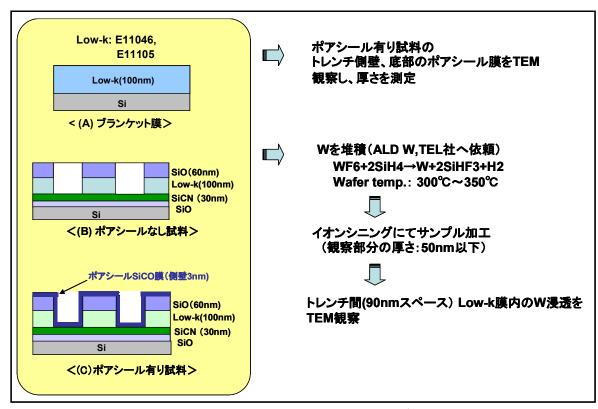

#### (1)試料構造

図皿.2.16.1 ポアシール評価用試料の構造(断面構造)

## (2)ポアシール評価試料の作成手順

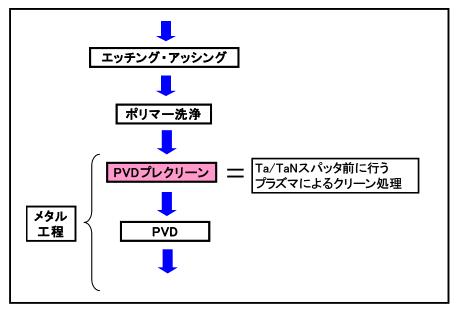

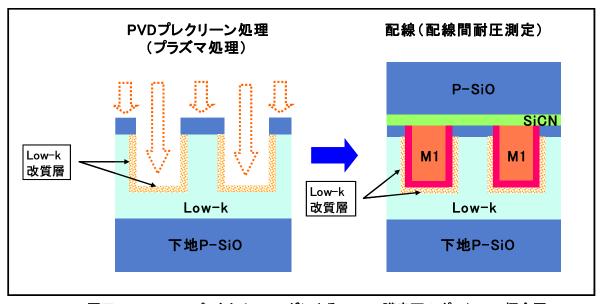

図Ⅲ.2.16.2 CASMAT基準プロセスでのCu配線層形成プロセス

図Ⅲ.2.16.3 に Ar スパッタクリーニングによる Low-k 膜表面のポアシール概念図を示す。

図皿.2.16.3 Ar スパッタクリーニングによる Low-k 膜表面のポアシール概念図

## Ⅲ. 2.1.6.3 測定方法

(1) Atomic Layer Deposition 法(以下 ALD と略す) W, TaN を用いた Low-k 膜ポアサイズが外部からの金属 浸透阻止能力に及ぼす影響測定

図皿.2.16.4 ALD W 膜を用いた Low-k 膜自身のポアシール評価手順

Low-k 膜内に浸透した W, TaN の検出には下記の3種類の測定法を用いる。

- ・明視野走査透過電子顕微鏡(以下 BG-STEM bright-field scanning transmission electron microscope と略す)

- ・ 高角度散乱暗視野走査透過電子顕微鏡(以下 HAADF-STEM high-angle annular dark-field scanning transmission electron microscope と略す)

- ・エネルギー分散型X線分光法(以下 EDX energy dispersive X-ray spectrometry と略す)

## (2)ポアシール膜のポア径の測定

ポア径の測定には陽電子消滅・空孔計測法(以下 PALS Positron Annihilation Lifetime Spectroscoy と略す)を用いる。本評価に記載している PALS 法でのポア径測定データは産業技術総合研究所フロンティア研究部門・極微欠陥評価研究グループ 大平氏から提供を受けたものである。 PALS 法の測定原理、測定法などに関しては評価基準書「Low-k 膜の空孔解析(SAXS 法、PALS 法)」に記載されている。

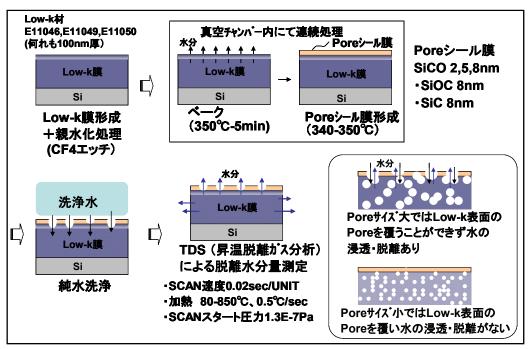

## (3)ポアシール膜の膜種、膜厚のポアシール効果依存性の評価

昇温脱離ガス分析(以下 TDS と略す)による Low-k 膜試料からの脱離ガス量の測定行う。 ポアシール 効果の測定手順としては試料外部から水分、金属を浸透させ、その浸透量を測定する方法を用いる。測定手順を図Ⅲ.2.16.5 に示す。

図III.2.16.5 TDS 分析用試料の作成方法と測定条件

#### Ⅲ. 2.1.6.4 測定結果

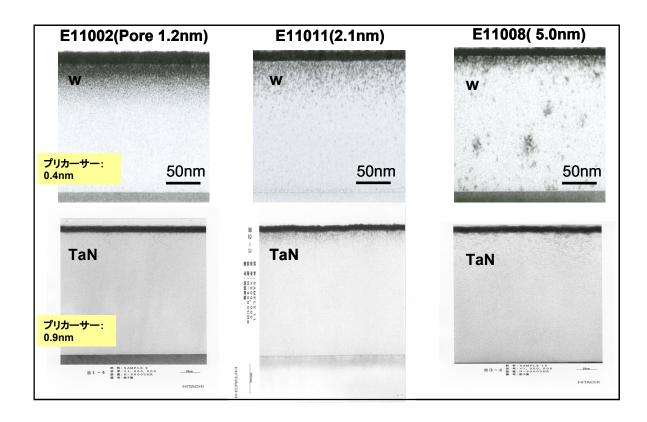

(1) Atomic Layer Deposition 法(以下 ALD と略す)W,TaN を用いた Low-k 膜ポアサイズが外部からの金属浸透阻止能力に及ぼす影響測定結果

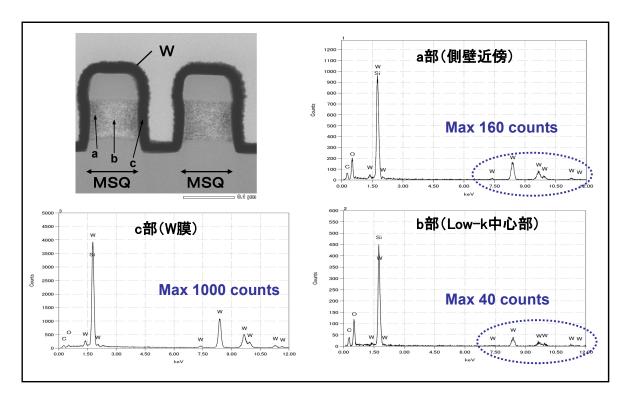

ポアサイズが異なる3種類の MSQ 単層膜表面に ALD 法で W,TaN 膜を成膜したときに MSQ 膜中に侵入した W,TaN の明視野走査透過電子顕微鏡観測結果を図Ⅲ.2.16.6 に示す。 図Ⅲ.2.16.6 において黒い部分が W,TaN である。 図Ⅲ.2.16.4 から以下のことが分かる。

①W,TaN 膜のどちらにおいても MSQ 膜のポアサイズが増加するに従って MSQ 膜中への W,TaN 浸透量が増加する。

②同一 MSQ 膜の場合、MSQ 膜中への W,TaN 浸透量はプレカーササイズが小さい W のほうが多い。 上記(1)(2)の測定結果は MSQ 膜中への W,TaN の浸透はポアを介して起こっており、その程度は浸透物質に対するポアの相対サイズが大きいほど促進されることを示している。

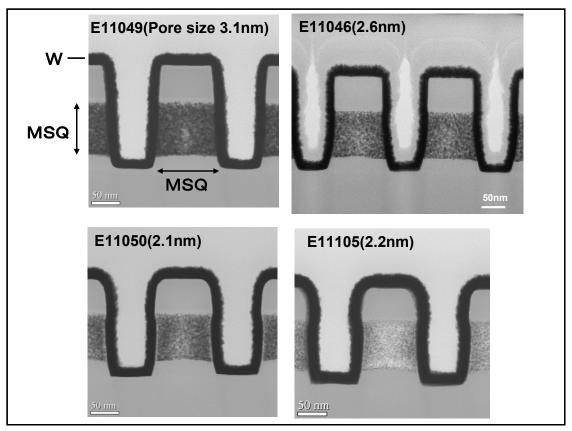

図Ⅲ.2.16.6 各種 MSQ 単層膜中への W,TaN の浸透

ポアサイズが異なる3種類の MSQ 単層膜トレンチ側壁部に ALD 法で W,TaN 膜を3nm成膜したときに MSQ 膜中に侵入したW,TaN の明視野走査透過電子顕微鏡観測結果を図皿.2.16.7 に示す。トレンチ部のM SQ層幅は90nmである。 図皿.2.16.7 において黒い部分が W である。MSQ膜のポアサイズが大きくなる に従いトレンチ部MSQ膜中へのWの浸透量が増加しており、これは図皿.2.16.6 の単層膜での測定結果と同じ傾向である。

図Ⅲ.2.16.7 MSQトレンチ側壁部へのWの浸透

図Ⅲ.2.16.6,7 の測定結果で観測されたMSQ膜中の黒く見える部分がWであることを確認するためには、図Ⅲ.2.16.8 に示したようにWを浸透させたMSQトレンチ部各部位に存在する元素分析をEDX法で行うことで確認できる。 分析部位は

- a:トレンチ部に成膜したW膜部分

- b: MSQトレンチ部の表面に近い部分(明視野走査透過電子顕微鏡観測で黒く見えるためWが存在すると考えられる部分)

- c: MSQトレンチ部の中央部分(明視野走査透過電子顕微鏡観測で白く見えるためWの存在が少ないと考えられる部分)

- の3か所を測定することが望ましい。

図Ⅲ.2.16.8 MSQトレンチ部のエネルギー分散型X線分光法(EDX)分析結果

図皿.2.16.8 に示したMSQ膜のEDX分析ではMSQ骨格を形成する主成分であるSiの特性X線( $K_\alpha$ : 1.740keV、 $K_\beta$ :1.836keV)とともに 7~10keV 領域に弱い特性X線が観測される。 これらのピークはWの特性X線ピークと同定できる( $L_\alpha$ :7.388keV、 $L_\alpha$ :8.398keV、 $L_{\beta_1}$ :9.673keV、 $L_{\beta_2}$ :9.962keV)。

Wからの特性X線強度は部位aのほうが部位bより高いことが分かる。 このことより図Ⅲ.2.16.6,7 の明視 野走査透過電子顕微鏡で観察されたMSQ膜中の黒く見える部分がWであることを確認できる。

## (2) TDS 法によるポアシール効果測定結果

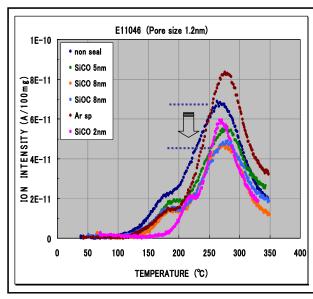

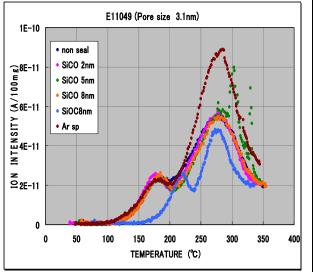

図皿.2.16.9にArスパッタクリーニング処理によるポアシール効果、及び CVD 膜(SIOC、SiCO)によるポアシール効果を TDS 法により測定した結果を示す。 図皿.2.16.5 に示したようにポアシール処理を行った試料を水に浸漬し、ポアシール膜を透過し MSQ 膜に浸透した水分量を TDS 法により測定する。 図皿.2.16.9 に示したように TDS 法測定ではポアサイズの異なる2種類以上の MSQ に対し TDS 分析を行い各種ポアシール膜のポアシール効果に MSQ 膜ポアサイズが及ぼす影響が評価できるようにすることが望ましい。

ポアサイズが小さい MSQ である E11046 ではポアシールを行っていない試料(図皿.2.16.9 で non seal と表示)にくらべ、ポアシール用 CVD 膜の膜厚増加により離脱水分量が減少しておりポアシール膜が厚いほどポアシール効果が高いことがわかる。

一方、ポアサイズが大きい MSQ である E11049 ではポアシールを行っていない試料(図皿.2.16.9 で non seal と表示)に比べポアシール用 CVD 膜厚増加による離脱水分量の減少が少ない。 このことからポアサイズが大きな MSQ ではポアシール用 CVD 膜によるポアシール効果が小さいことがわかる。

ポアシール法として Ar スパッタクリーニング処理を用いた試料での水分離脱量は測定に用いた2種類の MSQ において、non seal 試料より多いという測定結果が得られた。

図皿.2.16.9 TDS 法による各種ポアシール方法の評価

## 皿.2.16.5 考察

#### (1)MSQ 膜の金属、水分阻止能力

ある物質中への原子の拡散のしやすさは物質構成原子の周期的ポテンシャルを侵入原子がジャンプして乗り越えられる確率で特徴づけられ、フィックの第1法則、第2法則として知られている <sup>1)</sup>。比誘電率の低減のため MSQ 膜には分子骨格に起因した空間とともにこれより1桁以上大きなポアと呼ばれる空間(空洞)が存在している。 このため分子骨格により形成される周期的ポテンシャルを介しての一般的な拡散現象とは別にこのポアを経由して MSQ 膜中に外部からの原子、分子が侵入できる。 ここで考えられる外部からの原子、分子とは MSQ 膜表面に堆積した金属膜原子、あるいは BEOL プロセスによる水分、薬剤、ガス、あるいは保管中の環境雰囲気(大気)である。 これらポアは一部ポア同士がつながって存在している。このためポアを介しての MSQ 膜外部の金属原子、各種分子侵入は促進されると考えられる。

図Ⅲ.2.16.6~8 でポアサイズが大きな MSQ 膜ほど金属原子の侵入量が多いことは上記機構で理解できる。 またプレカーザサイズがTaNに比べ小さい W のほうが MSQ 膜への侵入量が多いこともMSQ膜への金属原子、分子の侵入はポアを介していることを示している。

## (2)ポアシール効果

ポアシール法は Low-k 膜表面を MSQ 膜より緻密な膜(ポアシール膜)で被覆したり、あるいは Ar スパッタクリーニング時の高エネルギーAr イオンの衝突により MSQ 膜表面を緻密化し、外部からの金属原子、分子の侵入を阻止する方法である。 外部の金属原子、分子はこのポアシール膜を通過しないと MSQ 膜には侵入できない。 これらポアシール膜は MSQ 膜のようなポアは存在したいため、ポアシール膜への金属原子、分子の侵入機構では述べたポアを介しての侵入ではなく、通常の拡散機構に近いものと考えられる。

拡散により膜中に侵入する深さ及び侵入量は(拡散定数×拡散時間)<sup>1/2</sup> の関数で特徴づけられる。 このためポアシール膜による外部の金属原子、分子の阻止能力はポアシール膜の膜厚に比例すると考えられる。 図皿.2.16.9の測定は試料を水に浸漬しポアシール膜を介してMSQ膜に水分を侵入させ、その侵入水

分量を TDS 分析で離脱水分量として測定した結果である。 測定結果をみるとポアシール膜の膜厚が増加するに従い離脱水分量が減少しており、このことは上述のメカニズムで説明できると考える。

## (3)ポアシール効果の MSQ 膜ポアサイズ依存性

BEOL で用いられる Low-k 膜は配線系での時定数による信号遅延を低減するため低比誘電率材料を用いている。 ポアシールに用いる CVD 膜は MSQ 膜に比べ緻密な膜でなければならないが、このことはポアシール膜の比誘電率は MSQ 膜に比べ高いことを意味する。 このためポアシール膜を用いることによるポアシール膜/MSQ 膜の比誘電率増加を抑えるためポアシール膜の膜厚は薄い方が望ましい。 このため図 皿.2.16.9 に示した評価ではポアシール CVD 膜の膜厚は8nm以下と薄膜としている。

このような薄いポアシール膜でMSQ膜表面を被覆する場合、その被覆性はMSQ膜のポアサイズの影響を受けることが予想される。 図Ⅲ.2.16.9 においてポアサイズが E11046 に比べ大きな E11049 でのポアシール効果の膜厚依存性がすくないのはこの推測の妥当性を示している。

#### (4) Ar スパッタによるポアシール効果

図皿.2.16.9 の測定結果では Ar スパッタでポアシールを行った試料からの水分離脱量がポアシールを行っていない試料よりも多くなっている。 Ar スパッタによるポアシール法では Ar イオンでスパッタエッチされたトレンチ底部の下地膜分子が MSQ 膜側壁に再付着するが、再付着膜の表面は再付着膜内部に比べ粗であるため試料を水に浸漬した時にこの部分に水分を吸着しやすい。 この水分が TDS 分析での水分離脱量に含まれるため Ar スパッタ法での水分離脱量がポアシールを行っていない試料からの水分離脱量より多く観測されたと思われる。

「配線 TEG を用いたポアシール効果の評価」では各種ポアシール法を用いて作成した多層配線 TEG での配線間絶縁耐圧を記載している。 多層配線 TEG での配線間絶縁耐圧では Ar スパッタ法を用いてポアシールを行った試料の配線間絶縁耐圧はポアシールを行っていない試料よりも高い結果が得られており Ar スパッタによるポアシール法の有効性が確認できる。

#### くまとめ>

PALS 法(陽電子寿命測定法)による porous Low-k 材料の空孔率、ポア径分布、空孔の連結性の測定をおこなった。その結果、多くの porous Low-k 材料は空孔の連結性が確認された。配線中への Cu イオン拡散防止のためプラズマ CVD 装置を用いて側壁に Si 系絶縁膜の薄膜を形成し、Low-k 材料配線層の空孔シールに成功した。

## Ⅲ. 2.17 CVD 膜堆積によるプラズマダメージの評価

多層配線を形成するプロセスにおいて、Low-k 材料はいろいろな影響を受ける。その結果、配線中に組み込まれた Low-k 材料の膜特性は、単独膜とは大幅に異なる事が考えられる。特にプラズマ CVD 膜を堆積するプロセスでは、Low-k 膜の表面がダメージを受けることによって、比誘電率k値の上昇が起こる事が知られている。

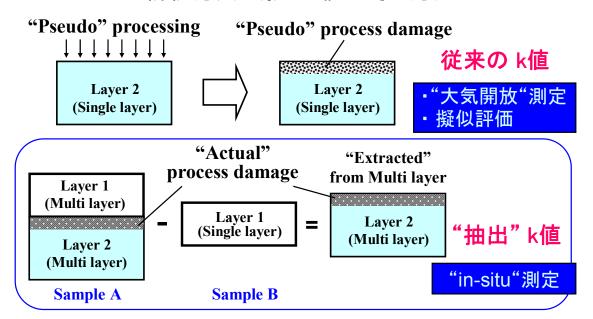

# Low-k膜のダメージ評価方法

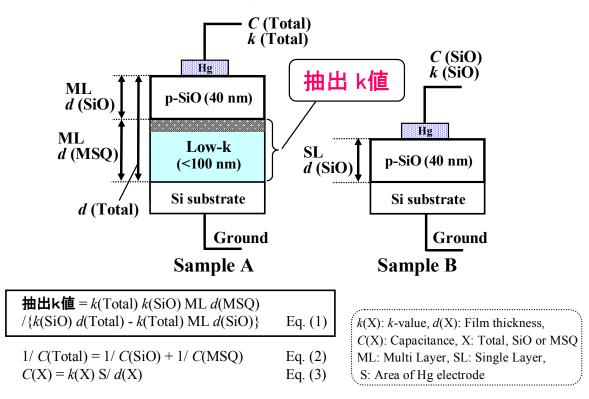

配線に組み込まれた Low-k 材料のk値を抽出するには、単膜でのプラズマダメージを測定する方法では不十分で、実際のプロセスを経た構造の容量を測定することによって、Low-k 膜部分のk値を求める必要がある。我々は、実際のプロセスステップに対応した配線の容量を測定して、その差を求めることによって、プロセスダメージを受けた Low-k 膜のk値を抽出することに成功した。しかし、Low-k 膜のk値の変動は膜厚方向に分布を持つため、組成変動に対応した膜厚を精度良く把握する必要がある。従来おこなわれてきた屈折率による分光エリプソ測定では、組成変動した Low-k 膜の膜厚を性格に把握することはできない。

我々は X 線反射率測定法(XRR 測定)を用いることによって密度分布による膜厚を精度良く測定することに成功した。

# 評価方法(抽出k値の考え方)

◆抽出k値の特長 より実際の工程に即したプロセスダメージを見積もることができる

# 評価方法 (抽出k値の測定方法)

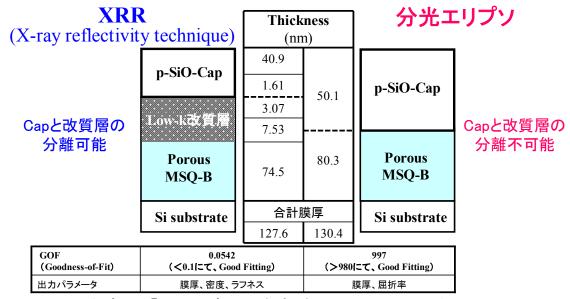

Low-k 膜の上に堆積したプラズマ CVDCap 膜を含む配線構造の膜厚分布を分光エリプソ測定した結果と XRR 測定した結果の比較を下図に示す。

XRR測定の場合、膜密度の違いからCap膜とLow-k変質層を分離でき、積層膜の各膜厚を正確に測定できるので、容量測定から比誘電率k値を正確に抽出することができる。

# 評価方法 (膜厚の分離決定)

- ◆XRRを適用。「5層モデル」で解析することで、Low-k改質層の 深さ解析が可能

- ⇒ 各層の膜厚を精度良く決定することでk値抽出の精度が向上

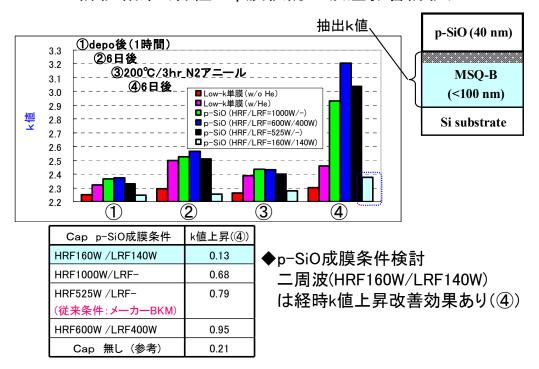

このように、Low-k 膜の膜厚とk値を抽出することによって、プラズマ CVDCap 膜堆積によ るダメージを正確に把握する事ができる。したがって Cap 膜堆積のプロセス条件によるダメージの差も把握する事が可能である。各種プラズマ CVD プロセス条件によってダメージを受けた Low-k 膜の経時変化を下図に示す。 プラズマ CVD 堆積によるk値の上昇は 10%以下であるが、大気中(CR内)放置によるk値の上昇は大きい。アニール処理によってk値は減少するが、その後の吸湿によるk値の上昇はプラズマ CVD のプロセス条件によって大きな差がある事がわかる。

k値上昇が最も少ないプラズマ CVD 堆積のプロセス条件は、低パワーの 2 周波である。

# 評価結果(各種Cap膜検討一吸湿影響評価)

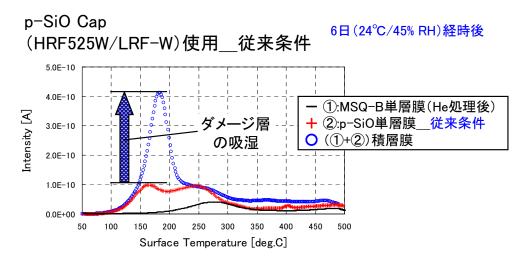

アニール後、大気中(CR 24°C、45%RH)に6日間放置した単周波(525W)積層膜と CVD、Low-k 単層膜を TDS にかけて脱ガスを測定した。結果を下図に示す。

Low-k 膜のダメージ層は吸湿している事がわかる。

# 積層膜吸湿性調査\_TDS

- ◆TDSによる M/z 18 (H,O)の検出(CR6日間放置後)

- ・吸湿するCap膜(単周波p-SiO\_従来条件)を使用した場合、 ダメージ層に水が吸蔵されている(非常に多い)

# くまとめ>

実際のプロセスステップに対応した配線の容量を測定して、その差を求めることによって、プロセスダメージを受けた Low-k 膜のk値を抽出することに成功した。さらに X 線反射率測定法(XRR 測定)を用いることによって改質層の深さ解析が可能となり、抽出k値の精度が大幅に向上した。吸湿の影響を追跡することによって、Low-k 材料間の差、Cap 膜 CVD 堆積プロセス条件によるダメージ影響が明確になった。

## Ⅲ. 2.1.8 ポリマー系の新規 Low-k 材料のソリューション開発

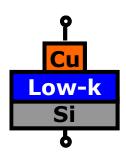

現在、Low-k 材には CVD 系の SiOC 膜が主に使用されているが、SiOC 膜中を配線材料の Cu が拡散 するため、Ta 系のバリアメタルを Cu と Low-k の間に挿入している。しかし、バリアメタルを用いると配線の 実効断面積が小さくなることや、Cu に比べて抵抗が高いために、配線抵抗の大きな増加を招く。ここで Cu 拡散バリア機能(Cu 拡散耐性)を有する Low-k 材を使用すると、バリアメタルの薄膜化が可能となり、配線抵抗の上昇を抑制することができる。Low-k 材の Cu 拡散耐性を評価し、拡散防止性を持たせた Low-k 材料を用いることによって配線の電気特性を調べた。

- ・単層膜での TDDB 寿命による Cu 拡散耐性評価

- •1 層配線での TDDB 寿命による Cu 拡散耐性評価

図Ⅲ.2.18.1 評価試料構造(単層膜)

図皿.2.18.2. 配線評価構造

## Ⅲ. 2.1.8.1 単層膜での TDDB 寿命評価に関する TDDB 測定方法と測定装置

測定装置:マニュアルプローバー

測定温度:140℃(N2 雰囲気下)

測定電界強度:~7MV/cm

(評価方法)

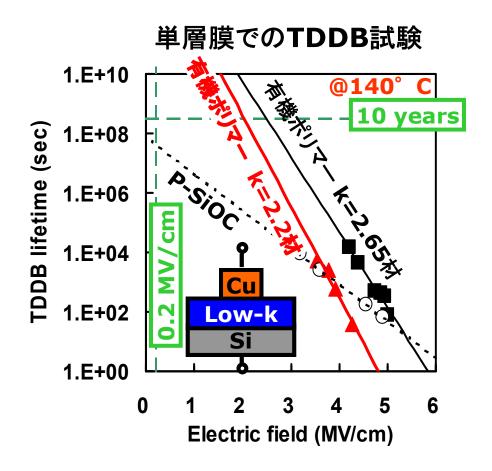

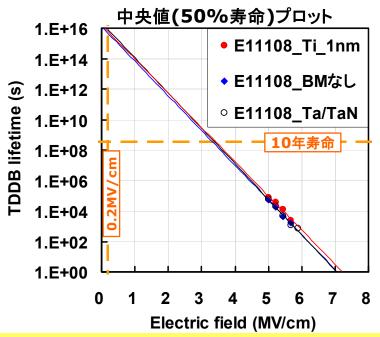

実用電界(0.2MV/cm)での TDDB 寿命を Low-k 材の Cu に対する絶縁信頼性と考え、その絶縁信頼性を p-SiOC と比較することにより Low-k 材の Cu 拡散耐性を評価する。

## Ⅲ. 2.1.8.2 1 層配線での TDDB 寿命評価に関する TDDB 測定方法と測定装置

(評価方法)

- (1) バリアメタルを省いた 1 層配線における実用電界(0.2MV/cm)での TDDB 寿命を測定し、配線試作でのプロセスダメージを加味した Low-k 材料の Cu 拡散耐性を評価する。

- (2) バリアメタルの有/無で TDDB 寿命を比較し、バリアメタルの TDDB 寿命への影響を確認し、配線抵抗低減を目的としたバリアメタル薄膜化のプロセスマージンを評価する。

## Ⅲ. 2.1.8.3 測定結果

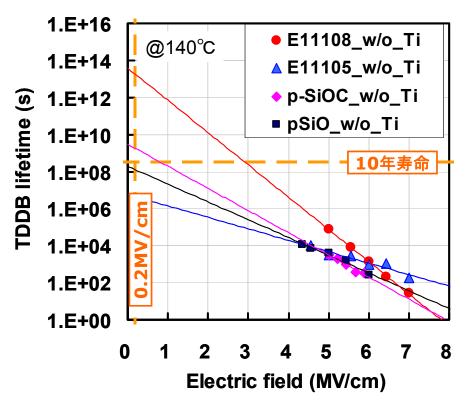

## (1)単層膜による TDDB 寿命評価結果

図Ⅲ.2.18.3 に単層膜による TDDB 寿命評価結果を示す。p-SiOC では実用電界での TDDB 寿命が 1.0E+7 オーダーであり絶縁信頼性の目標値である10年に満たないが、有機ポリマー系材料では、ノンポーラス材料の E11033 とポーラス材料の E11106 の両材料で10年を超える TDDB 寿命が確認された。図Ⅲ.2.18.3 の結果から、有機ポリマーの Cu に対する絶縁信頼性は p-SiOC より高いことがわかる。

図Ⅲ.2.18.3 単層膜による TDDB 寿命評価結果(■:E11033、▲:E11106、〇:p-SiOC)

## (2)1 層配線での TDDB 寿命評価結果

## バリアメタルを省いた 1 層配線を用いた TDDB 寿命評価結果

図皿.2.18.4 に TDDB 寿命評価結果を示す。Low-k 材料間で実用電界(0.2MV/cm)での TDDB 寿命に有意差がみられ、TDDB 寿命は、E11108>>p-SiOC>p-SiO>E11105 の順となった。高密度膜である p-SiO や比誘電率がほぼ同じでポーラス MSQ 材料である E11105 に比べてポーラスポリマーE11108 の TDDB 寿命は非常に長いことから、E11108 は Cu に対する絶縁信頼性が高い材料であることが示唆された。

図 Ⅲ.2.18.4 1 層配線での TDDB 寿命評価結果(パリアメタル無し\_1 層配線構造、●: E11108、▲: E11105、◆: p-SiOC、■: p-SiOC)

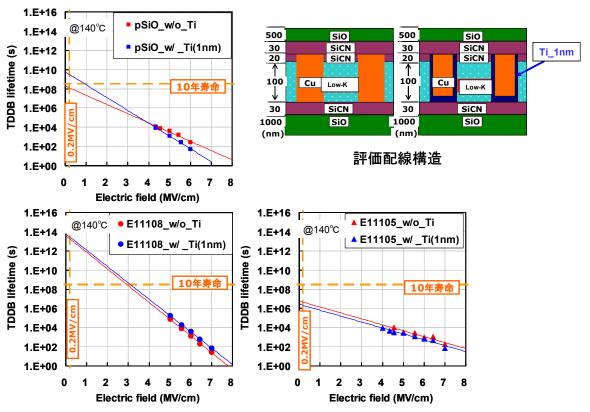

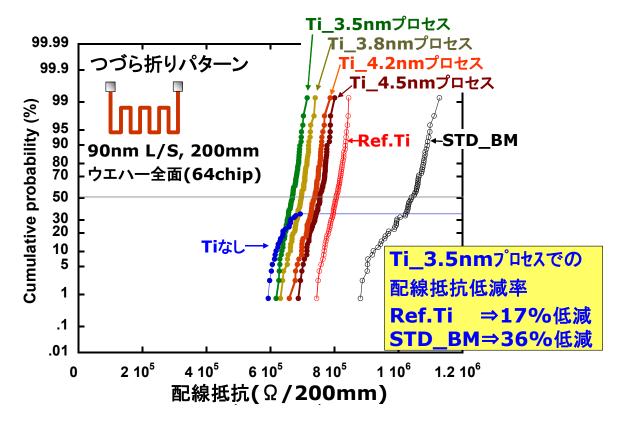

## Ti 薄膜を Cu 配線と配線間絶縁層の間に挿入した 1 層配線での TDDB 寿命評価結果

## [Ti の膜厚]

Ti 薄膜のノミナル膜厚: 3.4nm(p-SiO ブランケット膜上に成膜した際の膜厚)

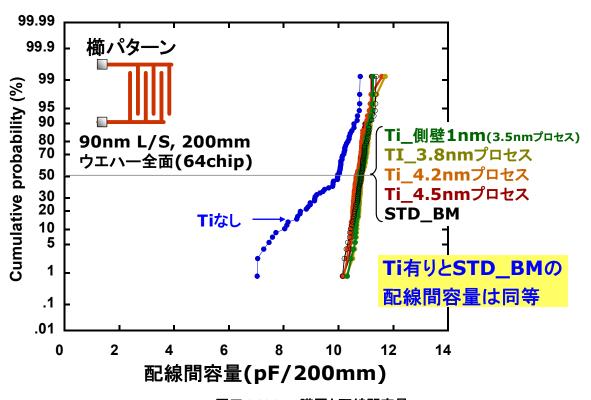

配線側壁(90nm L/S)での Ti 膜厚:1nm(E11108 を使用した場合の配線抵抗から算出)

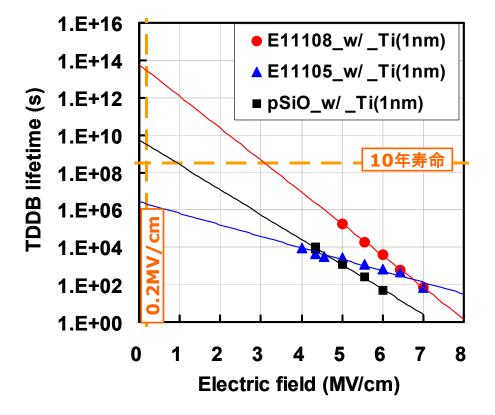

図Ⅲ.2.18.5 に TDDB 寿命への Ti 薄膜有無の影響に関して、図Ⅲ.2.18.6 に Ti 有りに関して、Low-k 材料間で比較した結果を示す。E11108とE11105ではTi 挿入によるTDDB 寿命への影響は見られないが、p-SiO では Ti 挿入により長寿命化する結果が得られた。

なお、ノンポーラス膜である p-SiO では Ti 挿入で長寿命化するが、ポーラス膜の E11108 と E11105 では寿命が特に変化していないことから、ポーラス膜の側壁では Ti が膜状ではなく島状についているため、Ti の被覆性の低下により Ti の Cu に対するバリア機能が低下した状態になっているのではないかと考えている。

図Ⅲ.2.18.5 TDDB 寿命への Ti 薄膜有無の影響(凡例 赤; Ti なし、青: Ti あり)

図Ⅲ.2.18.6 Low-k 材料間の TDDB 寿命比較(Ti 薄膜有り))

図皿.2.18.7 Ti 膜厚と配線抵抗

図Ⅲ.2.18.8 Ti 膜厚と配線間容量

**櫛パターン、90nm L/S、総対向長10mm**

Ti\_1nmにおいて、実用電界おいて10年寿命を確認 ⇒信頼性の劣化なし

図Ⅲ.2.18.9 実用電界寿命への Ti 有無の影響

# くまとめ>

多層配線の構造では、Cu の配線内部への拡散を防止するために、Ta/TaN などをバリアメタルとして使用している。Low-k 材料に Cu 拡散防止性を持たせることによってバリアメタルの膜厚を薄くし、配線全体の RC 積を低減、信頼性向上を実現する事ができる。ポリマー系の新規 Low-k 材料と約 2nm 膜厚の Ti ライナーを用いて、RC 積低減、TDDB 寿命の長期化を実現する配線構造とその製造プロセスを確立し、トータルソルーションとして学会で報告した。

## Ⅲ. 2.1.9 低圧 CMP プロセス

弾性率の低下した Low-k 材料の半導体製造プロセスでのダメージ耐性を直接的に評価するため、従来 1psi 以上の研磨圧力で行っていた CMP 研磨を、平成18年度に導入した低圧CMP装置を用いて、1psi から 0.1 psi までの範囲にわたって膜剥れや表面傷(スクラッチ)などを評価する。

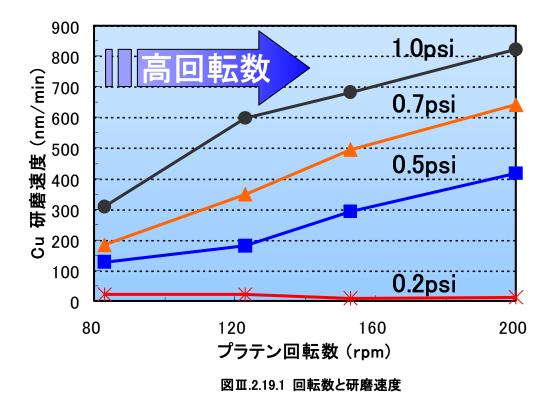

高回転数にすることで0.5psi以上の研磨圧力で、研磨速度を増加させることが可能。

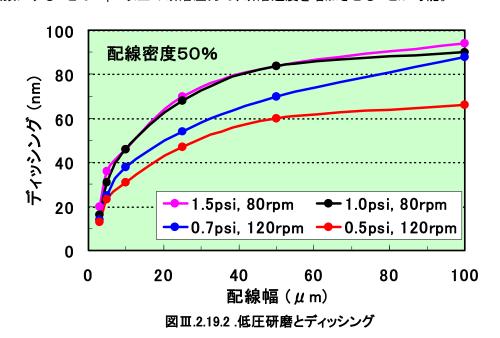

0.7psi以下の低圧CMPにより各配線幅において圧力に依存して平坦性を向上させることが可能。

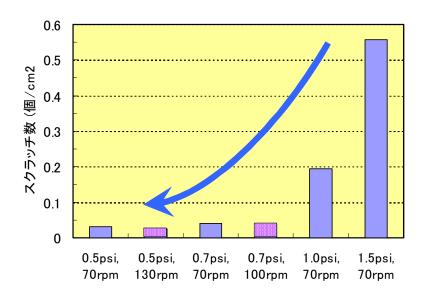

図Ⅲ.2.19.3 スクラッチ-研磨圧力依存性

研磨圧を低圧化することでスクラッチ数を減少させることが可能。

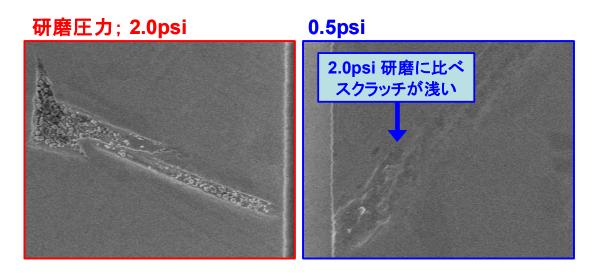

図Ⅲ.2.19.4 スクラッチの CD-SEM 画像例

低圧化により数の減少だけでなく、スクラッチの程度も低減可能。

## くまとめ>

低圧 CMP プロセスにおいて懸念される研磨速度の低下に対して、回転数を上げることで研磨速度を増加させることを可能にした。また 0.7psi 以下の低圧 CMP において平坦性が向上することを明らかにした。 CMP 起因の欠陥として重要な膜剥れやスクラッチに対して、CMP を低圧化させるほど低減させることができた。

## Ⅲ.2.2 統合部材開発支援ツール(TEG)の開発

Low-k 材料のダメージ耐性評価方法の開発で得られる半導体プロセスでの使用条件並びに影響を受ける製造プロセスに関する技術的知見をベースに、Low-k 材料とプロセス条件によって影響を受けるその他の材料を TEG で評価するべき項目を決定する。これらの項目について半導体デバイス製造プロセスを経た後に評価可能な計測回路の設計を行い、45nm ノードにも対応できる半導体材料評価 TEG の開発を行う。

計測回路の設計に当っては、材料評価手法の開発で得られる材料基本物性の情報と半導体集積回路で使用される条件での信頼性を含む統合化された部材性能との対応が評価可能なものとするとともに、半導体製造プロセスを経た後の TEG から得られる情報が、対象となる半導体材料の設計技術にフィードバックできる TEG を開発する。

#### Ⅲ.2.2.1 多層配線評価用 TEG

TEG を用いた評価方法は、半導体メーカーでは一般的であるが、半導体メーカー以外が有する場合は希有である。それも微細化に対応できる程の設計能力を有し、評価材料によって多層構造を有するTEGまで製造可能なのは本組合だけである。本組合では、既に 65nm ノードの多層配線 TEG を開発しているが、45nm ノードに対応できる材料評価用 TEG を開発する。

開発した TEG マスクは、Cu/Low-kデュアルダマシン2層配線の配線初期特性(配線抵抗、ビア抵抗、配線間容量、層間容量、配線間絶縁性、層間絶縁性)および配線信頼度(TDDB、エレクトロマイグレーション、ストレスマイグレーション)、加工形状評価(配線およびビアの形状)を可能とするものである。

## Ⅲ.2.2.1.1 マスク構成と各マスクの仕様

- ・マスクセット名称: CAST-4

- ・レチクル内のデータ描画領域:横 25.8mm、縦 32.4mm(ウェーハ上)

- ・レチクル上の値は上記の4倍(レチクル上のパターンはウェーハ上に1/4で縮小投影される)

表皿.2.2.1.1 マスクまとめ

| 適用層名            | (gdsレイヤー番号, | マスク仕様  |          |          |  |

|-----------------|-------------|--------|----------|----------|--|

| <b>巡用借</b> 有    | データタイプ)     | レチクル材  | ウェハ上寸法公差 | ウェハ上位置精度 |  |

| M1配線(M1)        | (2, 0)      |        | 4nm以下    |          |  |

| Via12(Via)      | (3, 0)      | ハーフトーン |          | 4nm以下    |  |

| M2配線(M2)        | (4, 0)      |        |          |          |  |

| Via23(Pro)      | (5, 0)      |        |          |          |  |

| AI配線(AI) (6, 0) |             | バイナリ   | 35nm以下   | 35nm以下   |  |

| 保護層(PV)         | (7, 0)      |        |          |          |  |

※適用層名欄の()内は本材料評価基準書および関連報告内で用いる略称

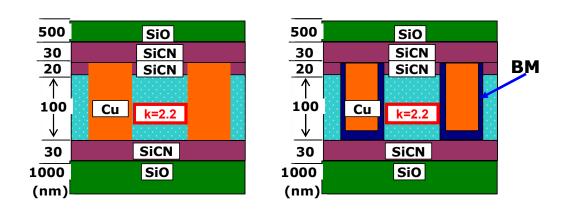

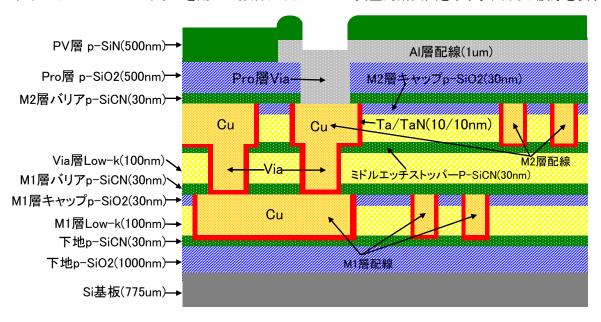

## Ⅲ.2.2.1.2 本マスクによる基本的断面構造

以下では M1~PV マスクまでを用いて作成したサンプルの典型的断面図を示す。()内は膜厚を表す。

図皿.2.2.1.1Cu/Low-k 2層配線断面図

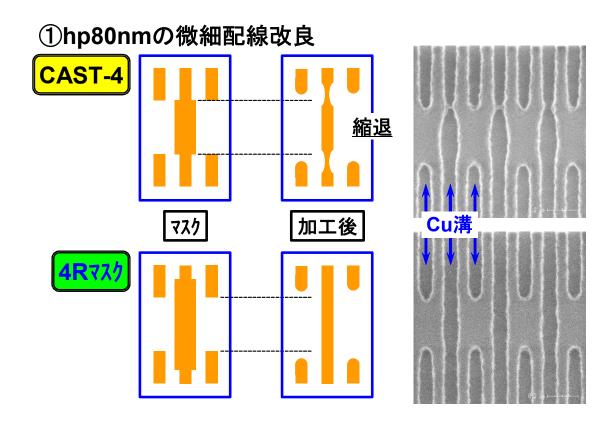

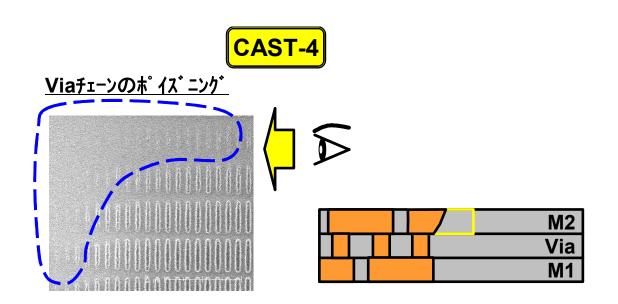

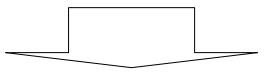

本 TEG のパターンレイアウトと改良ポイントを図Ⅲ.2.2.1.2 に示す。

図Ⅲ.2.2.1.2 多層配線評価用 TEG 外観図

縮退を考慮したマスクパターンの改良で微細配線改良を行った。

ポイズニング: 下地膜からのアルカリ性物質(アミン系等)によりレジストの 現像不良が起こり、適正なパターンができなくなる現象

ダミーパターン配置によりポイズニングを防止した。

#### くまとめ>

65nmノード対応多層配線 TEG マスク(最小寸法 90nm)を用いて、45nmノードで想定される Low-k 膜を含む各種絶縁膜の膜厚に設定して TEG 試作を行ない、配線の電気特性の測定を行なって材料ー材料間、材料ープロセス間の相互影響を評価した。その結果をもとに、45nm ノードの材料を評価するために重要となる測定項目、回路パターン、パターン配置などを検討し、第一次改良マスクを設計した。この TEG マスクを用いて配線幅あるいは配線間隔が 80nm の2層配線を試作し、配線寸法や形状を観察した。その検証結果から、微細配線形成のマスクパターンを改良した TEG マスクを導入することによって、Via チェーンのポイズニングを防止し hp80nm 配線を高歩留まりで形成する基準プロセスを確立した。この基準プロセスに基き各種 Low-k 材料を用いた8層配線を試作して、その電気特性を測定することによって、多層配線における Low-k 材料の評価基準を確立した。

この TEG は、材料評価用に開発されたものであるが、45 nm ノード微細配線における配線構造の評価をはじめ各種電気特性の測定が可能であり、デバイスメーカへのデータ提供にも供する事ができる。この TEG を使用することによって、材料開発の抜本的な効率向上が期待できる。

## Ⅲ.2.2.2 Low-k 膜 CMP プロセスダメージ耐性評価

CMP 圧力変化や Low-k 直接研磨が Low-k 膜物性/配線特性に与える影響を把握し、プロセスや材料の課題を抽出するために、Low-k 単層膜や p-SiO/Low-k 積層膜を用い、CMP 圧力や研磨量の違いが Low-k 膜物性にどの様な影響(ダメージ)を与えるか評価する。

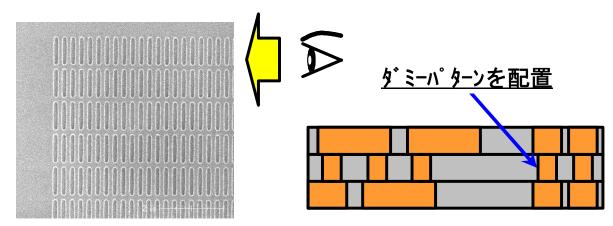

## Ⅲ.2.2.2.1 測定手順

CMP 後に X 線反射率測定法(XRR)にて積層膜厚を、水銀プローブを用いて静電容量を測定し、Low-k 膜抽出 k 値を求めた。

1) CMP 条件

スラリ K03003

パッド IC1400 (XY-k)

研磨圧力 0.5 ~ 4psi

回転数 70rpm

2) Low-k 膜抽出 k 値の算出

- •d(p-SiO), d(Low-k)は、XRR にて測定する。

- ・リファレンスとして、各単層膜の k 値を求める。

CMP圧力(Barrier-CMP); 4.0pai, 2.0pai, 1.0pai, 0.5pai

図Ⅲ.2.2.2.1 測定方法の概念図

# Ⅲ.2.2.2.2 測定結果

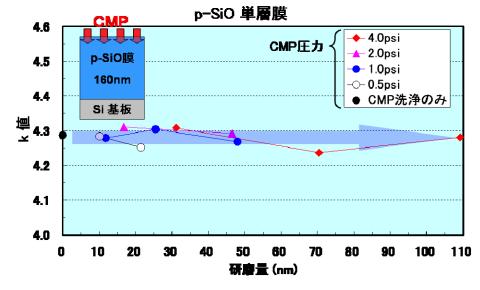

図Ⅲ.2.2.2.2 p-SiO 単層膜の CMP による k 値変動

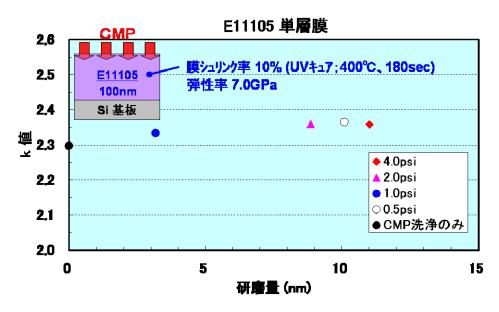

図Ⅲ.2.2.2.3 E11105 単層膜の CMP による k 値変動

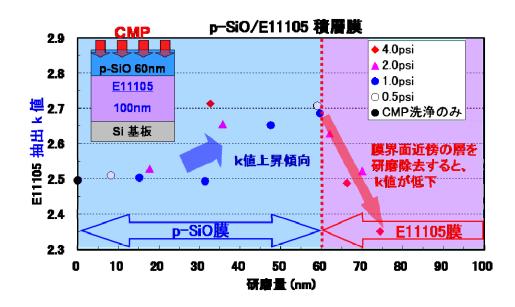

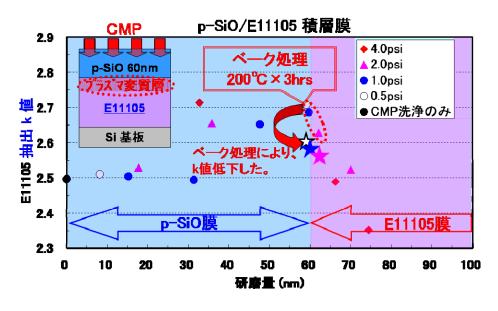

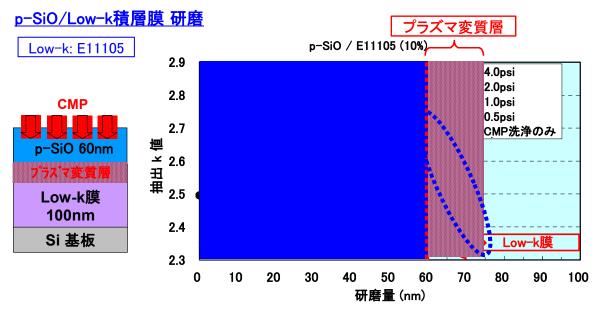

図Ⅲ.2.2.2.4 p-SiO / E11105 積層膜の CMP による k 値変動

p-SiO と E11105 それぞれの単層膜では、CMP による k 値変動は小さく、p-SiO / E11105 積層膜の場合に k 値変動が大きくなることから、p-SiO 成膜による E11105 のプラズマ変質層が寄与していると推察される。

プラズマ変質層の吸湿影響を調べるために、CMP 後のウェーハを 200°C、3 時間ベーク処理し、k 値を求めたところ、k 値の低下が認められた(図Ⅲ.2.2.2.5.)。

これによって、プラズマ変質層の吸湿が、k値上昇に寄与していることが示唆された。

本評価例では、単層膜、積層膜共に、CMP 圧力の違いによる k 値変化の有意差は見られなかった。

図Ⅲ.2.2.2.5 k 値変動に対する考察;ベーク処理結果

図Ⅲ.2.2.2.6 プラズマ変質層

### くまとめ>

半導体製造プロセスでのダメージ耐性を直接的に評価するために、p-SiO/Low-k 積層膜の直接研磨によって p-SiO 界面付近の Low-k を研磨していくと、Low-k 膜の抽出k値が低下(回復)し、CVD 膜堆積による Low-k 膜のダメージ層が除去される事がわかった。

### Ⅲ.2.2.3 Low-k 膜への CMP ダメージ評価

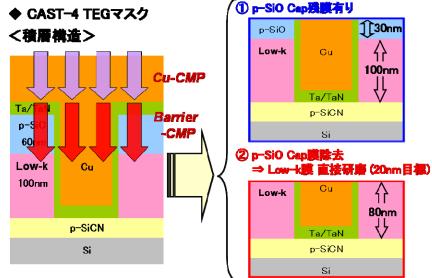

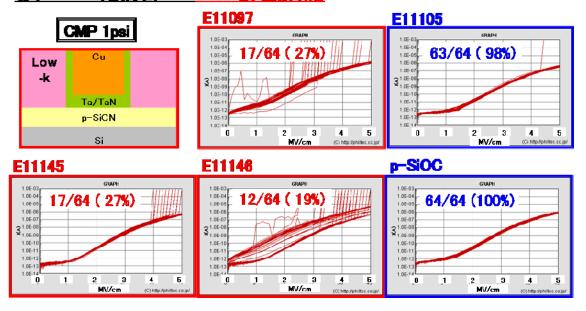

CMP プロセスにおいて、キャップ膜上で CMP を止める場合と Low-k 膜上で CMP を止める場合とを作製し、絶縁破壊耐圧の歩留まりを評価する。

#### 1) CMP 条件

- ・Cu-CMP スラリ K03002 パッド IC1400 (XY-k) 研磨圧力 1psi 回転数 80rpm

- Barrier-CMP スラリ K03003 パッド IC1400 (XY-k) 研磨圧力 0.5 ~ 2psi 回転数 70rpm

図Ⅲ.2.2.3.1 評価方法の概略図

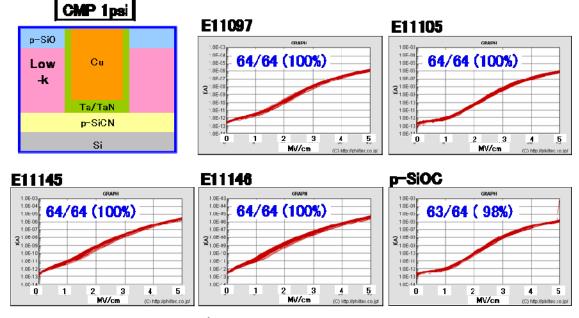

#### 2) 配線間耐圧評価

測定線幅 L/S=90/90nm 測定チップ数 ウェーハ全面 64 チップ

•測定結果

## ① p-SiO Cap残職有り

図Ⅲ.2.2.3.2 キャップ膜上で CMP を止めた場合(CMP 1psi)

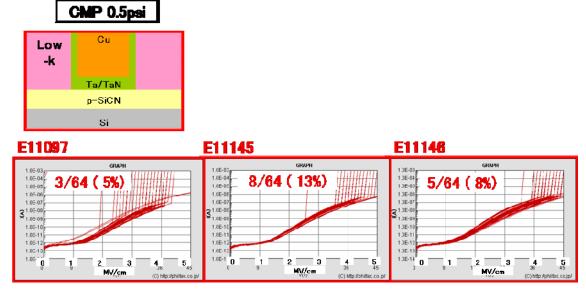

## ② p-SiO Cap膜除去 ⇒ Low-k膜 直接研磨

図III.2.2.3.3 Low-k 膜上で CMP を止めた場合 (CMP 1psi)

## ② p-SiO Cap膜除去 ⇒ Low-k膜 直接研磨

図III.2.2.3.4 Low-k 膜上で CMP を止めた場合 (CMP 0.5psi)

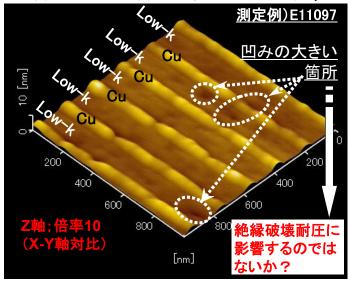

Low-k 膜を直接 CMP した場合に、絶縁耐圧の歩留まり評価で Low-k 材料間の差が明確となった。 E11097, E11145, E11146 については、CMP 圧力を 0.5psi まで下げても、絶縁破壊耐圧の向上は見られなかった。圧力を下げると研磨速度が低下し、研磨時間が長くなることから、長時間研磨により、Low-k 膜の劣化が進行するという側面も考慮する必要がある。しかしながら、圧力と時間の影響を切り分けることは困難である。

絶縁耐圧低下の要因については、Low-k 材料と CMP スラリ材料との相性など材料組成に踏み込んだ考察が必要である。

また、AFM による CMP 後の Low-k 表面粗さを次に示す。

### CMP後 表面粗さ解析

凹部; Low-k 凸部; Cu配線 研磨圧力; 2psi

Low-k部分のみを測定して、 表面粗さを解析し、Ra, Rzそ れぞれ5ライン分の平均値を 計算。

Ra : 平均面粗さ

Rz : 10点平均面粗さ

P-V: 最大高低差

| ا میں۔اد | Ra   | Rz   | P-V  |

|----------|------|------|------|

| Low-k    | (nm) | (nm) | (nm) |

| E11097   | 0.08 | 0.45 | 1.31 |

| E11105   | 0.06 | 0.31 | 0.66 |

| E11145   | 0.08 | 0.37 | 0.85 |

| E11146   | 0.08 | 0.42 | 0.96 |

| p-SiOC   | 0.04 | 0.23 | 0.54 |

図II.2.2.3.5 AFMによる表面粗さ分析

Low-k 膜表面粗さ : p-SiOC < E11105 < E11145 < E11146 < E11097

最大高低差 P-V や 10 点平均面粗さ Rz で材料間差を評価できた。

表面粗さが大きい程、耐圧歩留まりが低い事がわかった。

評価した Low-k 材料の膜物性と絶縁耐圧歩留まりと表面粗さを図Ⅲ.2.2.3.6、図Ⅲ.2.2.3.7 に示す。

### 評価Low-k材料の成膜条件と膜物性

| Low-k材料コードNo. | E11097                                    | E11105 | E11145 | E11146  | p-SiOC |

|---------------|-------------------------------------------|--------|--------|---------|--------|

| UVキュア条件       |                                           |        |        |         |        |

| 温度(℃)         | 400                                       |        |        |         | 1      |

| 時間(min)       | 6                                         | 3      | 4      | 4       | 1      |

| 膜物性@150nm     |                                           |        |        |         |        |

| 膜シュリンク率(%)    | 5.0                                       | 10.0   | 9.2    | 12.0    | -      |

| 比誘電率          | 2.33                                      | 2.37   | 2.05   | 2.07    | 3.01   |

| 弾性率(GPa)      | 8.3                                       | 7.0    | 4.0    | 5.9     | 8.6    |

| 硬度(GPa)       | 0.91                                      | 0.81   | 0.43   | 0.60    | 0.96   |

|               | Porous MSQ<br>k値; 2.3 - 2.4 k値; 2.0 - 2.1 |        |        | CVD系    |        |

| 材料選定の着目点      |                                           |        |        | 0 - 2.1 | リファレンス |

|               | 弾性率; 7 − 9 GPa   弾性率; 4 − 6 GPa           |        |        |         |        |

▶各種Low-k材料について、UVキュア条件を上表の通り決定し、配線試作を実施。

## 配線試作評価 結果まとめ

| 項目       | Low-k                              | E11097 | E11105 | E11145 | E11146 | p-SiOC |

|----------|------------------------------------|--------|--------|--------|--------|--------|

| 마井 바~ 사사 | 比誘電率                               | 2.33   | 2.37   | 2.05   | 2.07   | 3.01   |

| 膜物性      | 弾性率(GPa)                           | 8.3    | 7.0    | 4.0    | 5.9    | 8.6    |

| Low-k    | 表面粗さ(nm) Rz                        | 0.45   | 0.31   | 0.37   | 0.42   | 0.23   |

| 直接研磨     | <u>P-V</u>                         | 1.31   | 0.66   | 0.85   | 0.96   | 0.54   |

| *2psiデータ | 絶縁耐圧歩留り(%)                         | 5      | 100    | 22     | 36     | 100    |

| CMP圧力の   | CMP圧力の影響 1psi と 2psi とで明確な差は見られなか・ |        |        | かった。   |        |        |

▶Low-k膜の表面粗さ(Rz, P-V)が大きいほど、歩留りが低い傾向が見えた。

#### 図III.2.2.3.7 CMP 後の配線の絶縁耐圧歩留まりと表面粗さ

### くまとめ>

研磨後の配線の絶縁耐圧特性は Low-k 膜の種類によって異なり、配線間 Low-k 膜の表面粗さが大きいほど耐圧歩留まりが低い事がわかった。このことは、low-k 膜の脆弱性が絶縁破壊耐圧低下の原因であり、Low-k 膜の直接 CMP 研磨プロセスの適用可能性を示している。

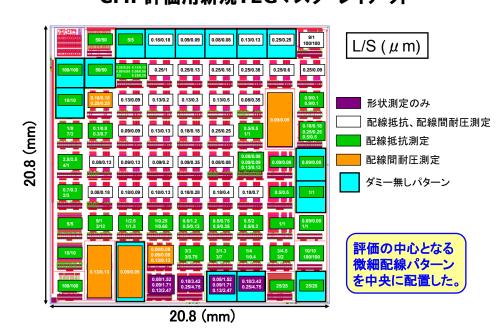

#### **Ⅲ.2.2.4** CMP評価用 TEG の開発

CMPプロセス評価用の TEG は SEMATECH などから市販されている。

しかし、これらの TEG はデバイスメーカでの半導体製造プロセス品質管理用として用いることを目的として 設計されたものであって、CMPスラリや Low-k 膜などの材料評価には必ずしも適しているとは言えない。 本組合は、多層配線に用いられる材料評価用として 65nm ノード対応 CMP TEG

を開発した。45nmノード対応へ改良するにあたっては、TEGを用いた材料に関する技術データが デバイスメーカで直接利用できるよう、TEGマスク設計に当り以下の改良点を組み込んだ

#### (1)配線密度依存性パターンの拡充

パターンバリエーションを充実させることで、各種 CMP プロセス条件に対応した表面形状や電気特性に対して、系統的にデータ整理が可能。(図Ⅲ.2.2.4.1)

(2)素子サイズ依存性パターンの導入

評価の中心となる平坦性評価を精度良くおこなうため、配線密度パターンについては、配線幅を固定してスペース幅をふることを中心にしてレイアウトを設計した。(図Ⅲ.2.2.4.2、図Ⅲ.2.2.4.3)

(3)ダミーパターン有無のパターン導入

平坦性に関し、CMP ダミーパターン有り、無しの 2 つの場合を調べることで、材料性能の加速的な評価および実際のデバイスに近い状態での評価が可能になる。(図皿.2.2.4.1、図皿.2.2.4.2)

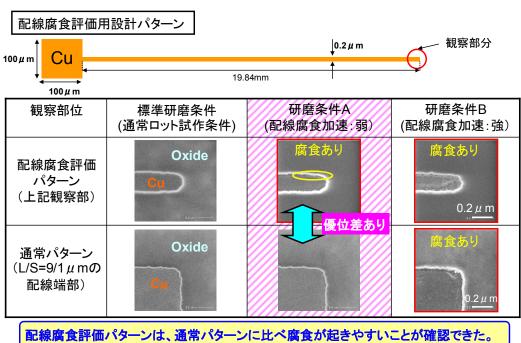

(4)配線腐食評価パターンの導入

電荷の局在化を利用して、微細配線の根元に相対面積の大きいパッドを設置し、配線の角や先端で Cuの溶解・析出を加速的に評価できるように、配線腐食評価用パターンを導入した。(図皿.2.2.4.4)

本組合の設計した TEG と市販 TEG の比較を表Ⅲ.2.2.4.1に示す。

この TEG を用いて Cu 用、バリア用の CMP スラリーについて、ディッシング、エロージョンなどの平坦性評価を極めて精度良くおこなう事ができる。また、CMP 研磨工程での電気特性を系統的に把握する事ができる事がわかった。

# CMP評価用新規TEGマスクのL/Sパターンマッピング

(凡例) ●:配線抵抗 ▲:配線間耐圧 ■:配線のみ

:ダミーパターン有り無し

微細配線、セミグローバル配線を重視し、配線密度は実用的な50 % ±30 % をメインとしつつも、材料特性をより明確に評価できるパターンも配置した。

図皿.2.2.4.1 TEG マスクのパターンMap

## CMP評価用新規TEGマスク レイアウト

図III.2.2.4.2 TEG マスクレイアウト

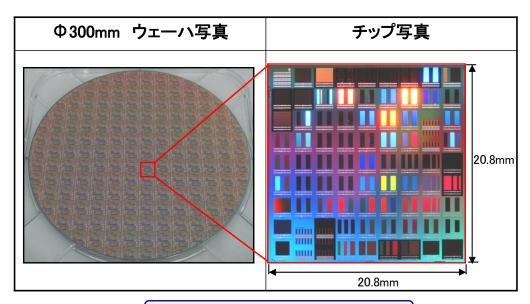

# ウェーハ外観写真とチップ写真

ウェーハ全面で132チップの評価が可能。

図Ⅲ.2.2.4.3 ウェーハ外観

# 配線腐食評価

図Ⅲ.2.2.4.4 腐食評価用パターン

#### 表Ⅲ.2.2.4.1 市販 CMP TEG との比較

## 市販CMP-TEGとの比較

| 項目                                                             | CASMAT CMP-TEG                                    | 市販 CMP-TEG                                         |  |

|----------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|--|

| 最小線幅                                                           | 80nm                                              | 100nm                                              |  |

| 配線密度依存性<br>(各配線幅の平坦性、電特)<br>*右記は、4種類以上の配線密度を有する<br>配線幅と配線密度種類数 | 最小線幅:80nm<br><b>8種類</b><br>最大線幅:3μm<br>配線密度:4~8種類 | 最小線幅:100nm<br><b>3種類</b><br>最大線幅:5μm<br>配線密度:4~6種類 |  |

| ダミーパターン有無<br>(同一ウェーハにおける比較)                                    | 有り                                                | 無し                                                 |  |

| パターン内位置依存性<br>(配線抵抗)                                           | 有り                                                | 一部有り                                               |  |

| パターンサイズ依存性                                                     | 有り                                                | 無し                                                 |  |

| 配線腐食評価パターン                                                     | 有り                                                | 無し                                                 |  |

## まとめ

- 1. 微細配線からセミグローバル配線まで、配線密度依存性を効率的に把握できる。

- 2. 素子サイズ依存性について、微細配線・セミグローバル配線で系統的に評価できる。

- 3. 素子内位置依存性の電気特性評価が可能になることで、従来の形状評価とともに 局所的な部分での電気特性・形状の相関関係の把握が可能になった。

- 4. ダミーパターン有無の検証に関して、段差量と配線抵抗測定を併せて行うことで、 L/Sパターン周辺部の絶縁膜研磨量の違いを明確化できた。 ⇒段差量と配線抵抗測定からL/Sパターン周辺部を含む形状の全体像が把握できる。

- 5. 配線腐食評価パターンが、通常パターンよりも配線腐食に対して感度が高いことを 確認した。

設計したパターンが正しく機能し、各評価において目的を果たしていることが確認できた。

材料評価(スラリ、パッド、CMP後洗浄液)への展開

#### くまとめ>

CMP 研磨条件とディッシング、エロージョンなどの配線平坦性を詳細に評価するために、配線幅や密度の異なるパターンを配置した CMP 専用の TEG マスクを設計した。この TEG マスクを用いた配線抵抗測定による配線厚みと段差測定によって、各種スラリ間の CMP 研磨特性能の差を明確に評価できることを確認した。また市販 TEG と比較して、CMPプロセスにおける材料評価ツールとしての優位性が確認された。

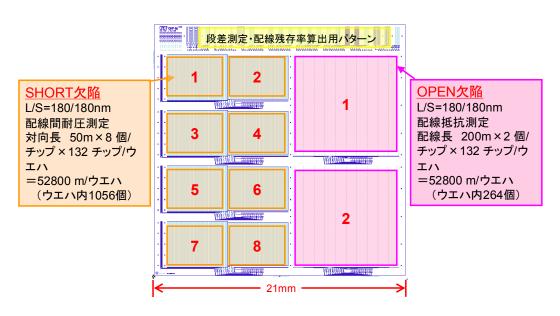

#### **Ⅲ.2.2.5 CMP 欠陥評価用 TEG マスク**

CMP プロセスにおける歩留まりを高精度に評価するために、比較的大規模パターンをウェーハ内に多数配置する必要がある。

300mm Φ ウエハ中132チップ配置 21mm 角

図II.2.2.5.1 CMP マスクレイアウト

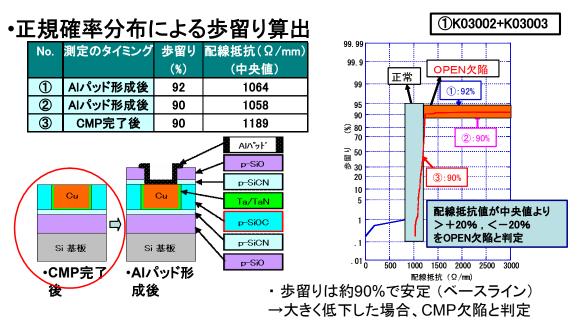

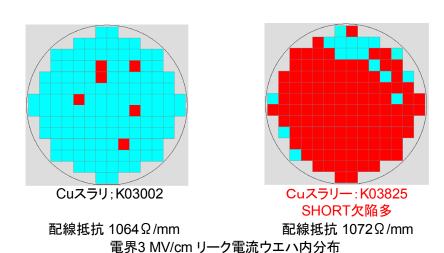

配線抵抗測定による Short/Open 欠陥が測定できる CMP 欠陥評価用 TEG を上図のように作製した。上記 TEG により評価した結果を次に示す。

III- 69

CMP 完了後での電気測定が可能となり、評価の迅速化、研磨状態の観察が可能となった。

OPEN欠陥(青チップ)にはパターン不良、ボイド、CMP欠陥が混在

正常チップ上の欠陥例

致命欠陥/全欠陥

= 14/296(個)

図III.2.2.5.2Open 欠陥の SEM 観察(標準研磨条件)

配線抵抗は同じであるので研磨量は同じであるが SHORT欠陥はK03825の方が多い

極微少の研磨残の有無を検知しているものと推察 ⇒オーバー研磨量の増加が必要と示唆している

図皿.2.2.5.3 Short 欠陥評価

## くまとめ>

CMP 研磨によるウェーハ上の欠陥を電気的に検出する TEG マスクを設計し、配線を大規模にすることによって、欠陥を高歩留まりで検出することに成功した。また電気測定によって致命的欠陥の検出が可能となった。

### Ⅲ.2.2.6 パッケージエ程評価用 TEG

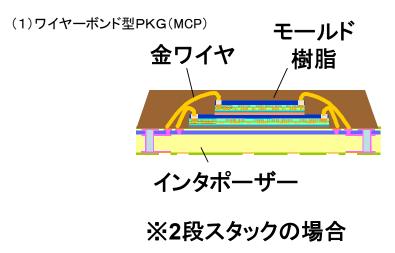

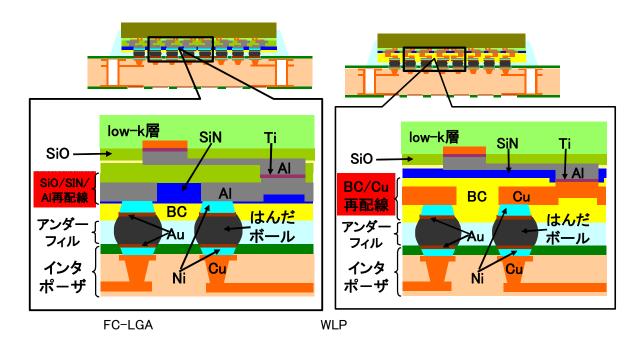

評価の対象とする PKG は、以下の図に示すワイヤーボンド型 (MCP:Multi-chip Package)を含む WBBGA(Wire-bond Ball Grid Array)および FCBGA(Flip Chip Ball Grid Array)型である。 配線工程を終了したウェーハを用いてパッケージを組立てる。

(2)ワイヤーボンドレス(フリップチップ)型PKG

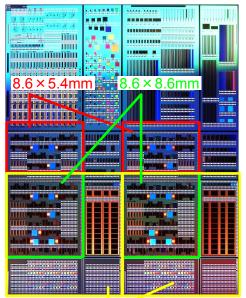

PKG 評価用 TEG チップのレイアウトは次の図の通り。

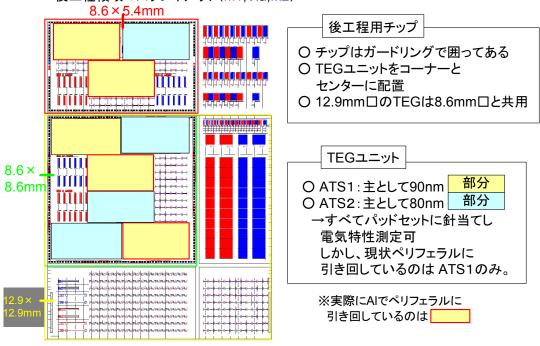

## 1ショットのレイアウト

$(25.8 \times 32.4 \text{mm})$

チップサイズと適用PKGの関係

| チップサイズ<br>(mm)   | МСР | FC-LGA<br>個別 一括<br>外注 外注 |   | WLP<br>個別<br>外注 |

|------------------|-----|--------------------------|---|-----------------|

| 8.6 × 5.4        | 0   |                          | - |                 |

| $8.6 \times 8.6$ | 0   | _                        | - | -               |

| 12.9 × 12.9      | _   | _                        | 0 | -               |

各PKGに対応したチップサイズを選択

## 12.9 × 12.9mm

1ショットで同じサイズのチップを2個取れる

後工程領域マスクレイアウト(M1,Via,M2)

(147、187、149マスク)

#### くまとめ>

パッケージエ程の材料評価方法の検討にあたり、対象パッケージを MCP(Multi-chip Package)を含む WBBGA(Wire-bond Ball Grid Array)および FCBGA(Flip Chip Ball Grid Array)等とし、配線工程を終了したウェーハを用いてパッケージを試作して、プロセス条件の検討を開始した。得られた知見をもとにパッケージ 工程専用の TEG マスクを設計し、この TEG マスクを用いて再配線工程から封止に至るパッケージ化各工程でのひずみや電気特性の変化を検証した。