# 発表内容

公開

- 1. 事業の位置づけ・必要性

- 2. 研究開発マネジメント

- 3. 研究開発成果

- 4. 実用化、事業化の見通し

1/25

3. 研究開発成果について (1)(中間)目標の達成度

公開

## ①多機能高密度三次元集積化技術の目標と達成状況

(1)次世代三次元集積化設計技術の研究開発研究開発

| 研究開発<br>テーマ                                    | 中間目標<br>(平成22年度)                                                                                                                                                               | 成果                                                                                                                     | 達成度      | 今後の課題                                                                                                                                                                      |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1)電気系シミュレー<br>ション技術の研究開<br>発                   | ・電気系三次元シミュレータにおいて、現状に比較し2桁多いメッシュ数及び8倍の信号幅の解析対象を、現状と同等の計算時間で解析するシミュレーションエンジンを開発する。  最終目標(平成24年度): ・現状に比較し2桁多いメッシュ数および8倍の信号幅の解析対象を、現状と同等の計算時間で解析することができる電気系三次元シミュレータの開発と評価を完了する。 | ・平成22年度末で最終目標を達成見込みであり、本年度で研究開発を終了する。次年度以降は、参加各企業において実用化レベルまでブラッシュアップする。 ・本成果は、市販ツールの1000倍の高速化を達成しており、現時点では世界最高レベルである。 | <b>©</b> | 平成23年度以降、参加各所第25年度以降、<br>参加各開発シミュレータを表示を開発した。<br>三次おける場合をでは、<br>三次おける場合を<br>計にの短は、<br>計にの短い、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、<br>が、 |

| 2)信号品質安定化<br>技術(SI) - 電源安定<br>化技術(PI)の研究<br>開発 | ・三次元集積化における信号品<br>質安定化技術、電源安定化技術<br>を開発する。                                                                                                                                     | ・次世代三次元集積SiPの安定動作で必要となるインターポーザにおける信号品質安定化技術(SI)・電源安定化技術(PI)の基本的技術・評価技術を開発した。                                           | 0        | ・SI、PIの設計指針確立を推進する。<br>・実証デパイス用インターポーザの設計および作製                                                                                                                             |

## ①多機能高密度三次元集積化技術の目標と達成状況

#### (2)次世代三次元集積化のための評価解析技術の研究開発

| 研究開発<br>テーマ                             | 中間目標<br>(平成22年度)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 成果                                                                                                                                                                                                                                                                                                                                                        | 達成度      | 今後の課題 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|

| 1)300mmウェハ<br>一括プロ <b>ーブ方式</b><br>の研究開発 | ・全体で30万端子を有し、そのうち高速デジタル信号テスト端子においては15Gbps 以上の信号に対応可能な300mmウェハに対応するプロープ方式の基本技術を開発する。 ・多端子プローブカードに関して非接触接続方式の実現可能性を検証する。 ・一つのプローブカードにおいて、10kW以上の安定した電力供給技術を開発する。・プローブカードにおいるチップテスト時、温度範囲-40°C~+125°Cにおいてパーンイン試験及びパーンイン試験を可能とする温度制御技術を開発する。 最終目標(平成24年度): ・300mmウェハに対応するプローブとして30万端子以上の被テスト端子への一括アクセスが可能であることを確認する。また、高速デジタル信号テスト端子においては、15Gbps以上の信号を用いた検査が可能であることを確認する。・平成22年度末までに開発したプローブをテスターと接続して評価を行い、プローブカードとテスト装置間において500Mbps以上の高速テスト信号を含む4万系統のテスト信号伝送が可能であることを実証する。 | ・全体で30万端子を有し、そのうち高速デジタル信号テスト端子においては15Gbps以上の信号に対応可能な300mmウェハに対応するプローブ方式の基本技術の最終目標を前倒しで達成した。 ・200チャンネル/伝送速度500Mbps以上動作の非接触コネクタ(容量結合)を開発し、非接触コネクタを用いたプローブカードとテスト装置間において4万系統のテスト信号伝送が可能であることを実証した。 ・10kW以上の安定した電力供給技術を開発した。 ・温度範囲−40℃~+150℃において、チップテストおよびチップパーンイン試験を可能とし、温度範囲70℃~+150℃においては、ウェハー括バーンイン試験を可能とする温度制御技術を開発した。 ・本成果は世界に類を見ず、インテル、三星等からも、注目されている。 | <b>©</b> |       |

事業原簿 I-2~41

3/25

3. 研究開発成果について (1)(中間)目標の達成度

公開

## ①多機能高密度三次元集積化技術の目標と達成状況

#### (2)次世代三次元集積化のための評価解析技術の研究開発

| 研究開発<br>テーマ                            | 中間目標<br>(平成22年度)                                 | 成果                                                                                        | 達成度 | 今後の課題                                               |

|----------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|

| 2)三次元集積化<br>の熱・積層接合<br>評価解析技術の<br>研究開発 | - 次世代三次元集積化のための熱<br>評価解析技術及び積層接合評価<br>解析技術を開発する。 | -20W、10,000パンプを超える次世代三次元積<br>層SiP実現のための、熱・積層接合技術の基<br>本的評価解析技術を開発した。                      | 0   | ・熱TEGによる<br>測定とシミュレ<br>ーションの整合<br>・10umのパンプ<br>接合観測 |

| 3)薄化ウェハ<br>評価解析技術の<br>研究開発             | ・10μmに薄化した300mmウェハ<br>の評価解析技術を開発する。              | <ul><li>・10±1µm極薄ウェハ加エ・ハンドリングが可能となった。</li><li>・ゲッタリング効果や残留ひずみが定量的に評価できることを検証した。</li></ul> | 0   | デパイス及びTSV<br>付き実ウエハでの<br>検証。                        |

## (3)次世代三次元集積化設計技術及び次世代三次元集積化のための評価解析技術の有効性実証

| 研究開発<br>テーマ                 | 中間目標<br>(平成22年度)                                                                                                                                                                        | 成果                                                                                  | 達成度 | 今後の課題            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|------------------|

| 1)次世代三次元<br>積層SiPの有効性<br>実証 | ・実用的なアプリケーションを想定した実証用三次元積層SiPの候補と、その機能検証を行う仕様を策定する。 (平成21年度実施方針)・実用的なアプリケーションを想定した実証用三次元積層SiP(実証デバイス)の第一ステップとして、ロジックと超ワイドパスメモリの2チップ構成(ビット幅2k本以上、伝送能力100GB/sec以上)とした実証デバイス#1を試作し機能を検証する。 | ・実証デバイス#1として、超ワイドバスメモリの基本検討を完了した。 ・実証デバイス#2として、10,000fpsの高速画像処理を実現する要素回路の基礎検討を終了した。 | 0   | -TSV積層構造<br>への展開 |

## ②複数周波数対応通信三次元デバイス技術の目標と達成状況

#### (1)複数周波数対応可変RF MEMSデバイスの研究開発

| 研究開発<br>テーマ                                   | 中間目標<br>(平成22年度)                                                                                                                                                                                                                                                                                        | 成果                                                                                                                                                                                                                                  | 達成度 | 今後の課題                            |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|

| 1)複数周波<br>数対応可変<br>RE MEMS研<br>パイスの研<br>究開発   | ・700MHz〜6GHzに含まれる周波数帯域において、MEMSデバイスのスイッチ、キャパシタ、インダクタを組み合わせ、可変アンテナ、可変インピーダンス回路、可変フィルタの動作を実証する。さらに低損失及び小型化のための指針を示す。・MEMSデバイスにおいて、挿入損失5dB以下、通過帯域幅10%の可変フィルタを開発する。・MEMSデバイスにおいて、デジタル動作の可変フィルタを開発し、専用ドライバにの設計を行う。・MEMSデバイスにおいて、挿入損失2dBのインピーダンスマッチング回路を開発する。・MEMSデバイスにおいて可変インダクタとCMOS制御回路融合に向けた環境構築、設計試作を行う。 | ・MEMSスイッチを用いた可変アンテナ、MEMSキャパシタを用いたインピーダンス回路の動作を検証し目標を達成した。特に可変アンテナは世界トップレベルの可変範囲を得た。 ・MEMS可変フィルタは動作周波数数2.95~4.12 GHz、挿入損失4dB以下と目標を達成し、世界トップレベルの性能を得た。 ・MEMS可変インダクタは高可変率を可能とする構成を見出した。CMOS回路との融合にむけたて昇圧回路を考案、試作により3.3Vから24Vへの昇圧を確認した。 | 0   | - 可変アンテ<br>ナの小形化<br>を狙う三次<br>元化。 |

| 2) RF MEMS<br>デバイス三<br>次元集積化<br>実装技術の<br>研究開発 | <ul><li>・複数周波数対応通信三次元デバイスの三次元<br/>積層構造での高周波回路実装技術を開発する。</li><li>・可変フィルタの特性を補完する通過帯域制御技術を開発する。</li></ul>                                                                                                                                                                                                 | ・可変フィルタモジュールの三次元実装をウエハレベルで完結させる低コスト化を目指す高周波回路実装技術を検討を完了し、今後の開発課題を明らかにする見込みである。                                                                                                                                                      | 0   | ・可変フィル<br>タの三次元<br>積層IC化。        |

#### (2)複数周波数対応通信フロントエンド回路の研究開発

| 研究開発<br>テーマ                                   | 中間目標<br>(平成22年度)                                                                          | 成果                                                                                            | 達成度 | 今後の課題                             |

|-----------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|-----------------------------------|

| 1)複数周波数対<br>応通信フロントエン<br>ド回路MCMの研究<br>開発と動作実証 | ・RF MEMSデバイスを組み合わせ、複数の<br>周波数帯域において通信可能な試作回路<br>を作成しその動作を実証する。MCM化に<br>向けたパラメータと課題の抽出を行う。 | ・フロントエント・回路の制御部設計、インタフース設計と製作を行い、周波数可変制御、送・受信制御を実証した。<br>MEMSデバイスを用いてのフロントエンド動作検証<br>は世界初となる。 | 0   | 今後の予算<br>規模に合わ<br>せて可能な<br>対応となる。 |

事業原簿 I-42~70

5/25

3. 研究開発成果について (1)(中間)目標の達成度

公開

## ③三次元回路再構成可能デバイス技術の目標と達成状況

(1)三次元回路再構成可能デバイスに関する三次元集積化技術の研究開発

| 研究開発<br>テーマ                         | 中間目標<br>(平成22年度)                                                                                                                                                                                                     | 成果                                                                                                                                                                          | 達成度 | 今後の課題 |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

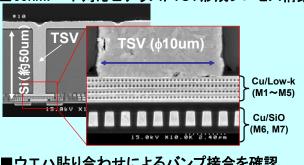

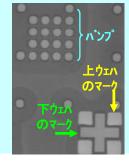

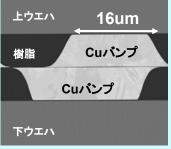

| 1)三次元回路再構成可能デバイス配線構造・ウェハ積層接合技術の研究開発 | ・三次元回路再構成可能デバイスを実現する三次元集積化技術のうちウェハ接合技術として、1mm2程度の面積を占める三次元集積化構造のコア間で、1000ピン以上の接続を可能とするシリコン貫通ビア、バンブ構造等を開発し、200mm径以上のウェハを用いて実証する。 ・三次元回路再構成可能デバイスを実現する三次元集積化技術のうち高精度位置合わせ技術を開発し、200mm径以上のウェハ貼り合わせで、5μm以下の位置合わせ精度を実証する。 | - 基本レイアウトルール案を策定し、TEGの設計試作を行い、1mm <sup>2</sup> 2あたり1000ピン以上(数万本以上/チップ)を実現する裏面ビアラスト型TSVプロセスを構築した。 - 埋込型Cuパンプを形成した200 mmウエハの貼り合わせを行い、パンプ位置あわせ精度3.4 μm±1.3 μm(1σ)が得られることを確認した。 | 0   |       |

#### (2)三次元回路再構成可能デバイスに関するアーキテクチャおよび設計技術の研究開発

| 研究開発<br>テーマ                                                | 中間目標<br>(平成22年度)                                                                                                                                                                                                         | 成果                                                                                                                                                                                                                                                           | 達成度 | 今後の課題 |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

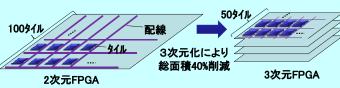

| 1)三次元回路再<br>構成可能デバイ<br>スアーキテクチャ<br>および設計技術<br>の研究開発と実<br>証 | ・三次元的な積層構造を利用した動的リコンフィギャラブルプロセッサのアーキテクチャを開発し、論理設計を完了する。このアーキテクチャを用いた4層積層において、二次元構成に比較して、消費電力当たりの性能が1.25倍以上となることを実証する。 ・三次元的な積層構造を利用したFPGAを開発し、論理設計を完了する。このアーキテクチャを用いた4層積層において、二次元構成に比較して、消費電力当たりのゲート数が1.25倍以上となることを実証する。 | ・三次元の特長を活かせる応用としてネットワーク分野およびロボット分野について、三次元回路再構成可能デバイスへの搭載機能を検討し、本年度中にハイブリッドアーキテクチャの設計を完了する見込みである。 ・FPGAタイル基本回路の検討・設計を行い本年度中にモジュール設計を完了する見込みである。・以上の検討からチップの4層積層において、二次元構成に比較して、消費電力を20%削減できる見込みである(消費電力当たりの性能が1.25倍以上)。・三次元回路再構成デバイスとしては、世界トップレベルの成果が得られている。 | 0   |       |

## ①多機能高密度三次元集積化技術の成果

## (1)次世代三次元集積化設計技術の研究開発

1)電気系三次元シミュレーション技術の研究開発

次世代三次元積層SiPの設計に必要となる 設計環境の構築の実現

- ・今まで時間が掛り過ぎて、解析を諦めていた 回路を解析可能に!

- ·従来市販ツールの、500-1,000倍程度の高速化

| シミュレータ          |     | 開発項目           | H21年度 | 中間目標<br>(H22年度) | 最終目標<br>(H24年度) |

|-----------------|-----|----------------|-------|-----------------|-----------------|

|                 | 線形  | 改良LIM法<br>十並列化 | x300  | x400            | X900<br>~1500   |

| 高速電気回路シミュレータ    |     | Multi-Rate法    | x1.0  | x2.0            |                 |

|                 |     | 小計             | x300  | (X800)          |                 |

|                 | 非線形 | 回路分割<br>十並列化   | x10   | x12             | x50             |

|                 | AD  | E-FDTD法        | x3    | х3              |                 |

| 高速電磁界<br>シミュレータ | グリ  | リッド数低減法        | x7    | x21             | (x500)          |

|                 |     | 並列化            | x10   | x10             |                 |

|                 |     | 小計             | X210  | (x630)          |                 |

2)信号品質安定化技術(SI)·電源安定化技術(PI) の研究開発

・次世代三次元集積SiPの安定動作で必要となるインターポーザ におけるSI・PI の基本的技術・評価技術を開発

#### 【信号品質安定化・電源安定化技術】

高速ドライバチップ用 インターホ゜ーサ・モシ・ュール TEG開発

TEG外観写真 電源ノイス・評価システム開発

チップキャパシタ 内蔵による 電源安定性 向上を実証

6Gbps駆動時の電源電圧変動

【素子内蔵インターポーザの評価・検査技術】

広帯域高精度電源インピーダンス

評価システムを開発

事業原簿Ⅲ-2~41

7/25

#### 3. 研究開発成果について (2)成果の意義

公開

## ①多機能高密度三次元集積化技術の成果

## (2)次世代三次元集積化のための評価解析技術の研究開発

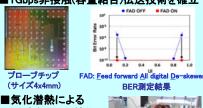

1)300mmウェハー括プローブ方式の 研究開発

三次元集積化に向けたKGD獲得を可能にした

■接触・非接触混在プローブ技術を開発 接触 パンプ 非接触 パッド プローブ チップ 18.6万端子接触・非接触 混在プローブカード ■1Gbps非接触(容量結合)伝送技術を確立

15kW冷却·温調技術 を開発

潜熱冷却技術

2)三次元集積化の熱・積層接合 評価解析技術の研究開発

三次元集積化に向けた基盤技術の開発

- 10umPitch 10,000接合/chipを実現 する3D接合技術を開発。

- 微細パンプの評価観測技術の確認

三次元積層構造の熱シミュレーション手 法の開発

20W/cm<sup>2</sup>に対応できる小型冷却シ

ステムを開発 3次元積層構造固有のの放熱問題

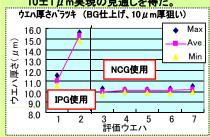

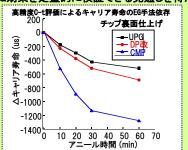

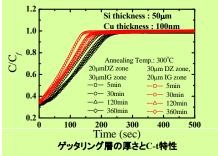

3) 薄化ウェハ評価解析技術の研究開発

NCGを適用したBGにより加工精度 10±1μm実現の見通しを得た。

種々のEG領域を有する極薄ウエハについて Cu強制汚染+高精度C-t 評価を実施し、 EG効果を定量的に検証できる見通しを得た。

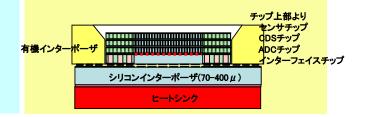

## ①多機能高密度三次元集積化技術の成果

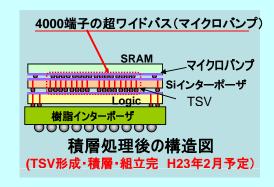

(3)次世代三次元集積化設計技術及び次世代三次元集積化のための評価解析技術の有効性実証

#### (a)実証デバイス#1

モバイル・携帯機器やデジタル家電・サーバー 等における画像処理応用に向け、

ロジック(画像処理プロセッサ等)と 超ワイドバスメモリ(DRAM)を

三次元積層した超多ピン(4000端子)相互接続構造の設計技術、ノイズ評価技術を開発中。

#### (a)実証デバイス#2

・将来の高速画像処理システム(10,000fp)の下記 要素回路基礎検討・チップ試作を行い、要素技術と して目標性能を達成した。

センサ回路 CDS回路(ノイズキラー) ADコンバータ 高速インタフェース回路 リコンフィギュアラブルメモリ

・平成22年度末に向け、TSVを含む積層ジュール のコンカーレント設計(TSV接続整合関係、信号タ イミング整合条件、電力配分、電極構成)を行う。

事業原簿Ⅲ-2~41

9/25

3. 研究開発成果について (2)成果の意義

公開

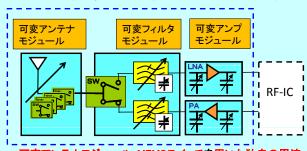

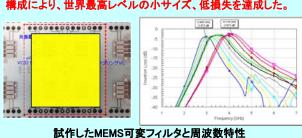

## ②複数周波数対応通信三次元デバイス技術

(1)複数周波数対応可変RF MEMSデバイスの研究開発

・目的: 周波数可変のRF通信フロントエンド回路の開発

・可変アンテナモジュール: MEMSスイッチを用いた独自の周波数可変機能を実現し、世界最高レベルの可変範囲700MHz~6GHzを達成した。 ・MEMS可変フィルタ: 新開発の高誘電率基板と新考案の回路

・MEMS可変フィルタ:新開発の高誘電率基板と新考案の回路 構成により、世界最高レベルの小サイズ、低損失を達成した。

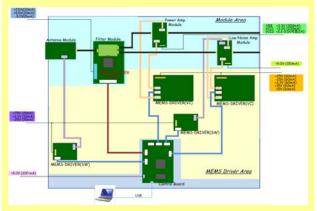

(2)複数周波数対応通信フロントエンド回路の研究開発

・フロントエンド回路を試作し、周波数可変制御、送信制御、受信制御を実証する見通し。MEMSデバイスを用いてのフロントエンド動作検証は世界初となる。

試作したフロントエンド回路は可変フィルタ、可変アンテナモジュール、可変PAモジュール、可変LNAモジュールと、モジュール内のMEMSデバイスを駆動するMEMS駆動用ドライバ、更にホストPCとのインタフェースを行う制御部から構成。

複数周波数対応通信フロントエンド回路の接続構成

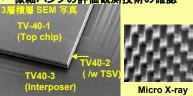

## ③三次元回路再構成可能デバイス技術

- (1)三次元回路再構成可能デバイスに関する 三次元集積化技術の研究開発

- (2)三次元回路再構成可能デバイスに関する アーキテクチャおよび設計技術の研究開発

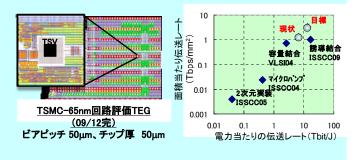

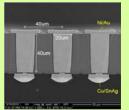

■65nmノード対応ビアラストTSV形成プロセス構築

■機能マッピングプログラムを開発し、定量的に三次元 FPGA構成を検討。総面積を40%削減。

■ウエハ貼り合わせによるバンプ接合を確認

(左:積層ウェハの赤外線写真,右:バンプ断面SEM)

■新規三次元通信回路の提案・試作により、面積 および電力当たりの伝送レートにおいて、世界最高水 準の成果が得られる見通し。

事業原簿 I-71~88

11/25

3. 研究開発成果について (3)知財と標準化 及び (4)成果の普及 公開

## (3)知的財産権、成果の普及

|       | H20 | H21 | H22 | H23 | H25 | H26 | 計   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| 論文投稿  | 0   | 1   | 1   |     |     |     | 2件  |

| 学会発表  | 1   | 56  | 10  |     |     |     | 67件 |

| その他発表 | 1   | 3   | 1   |     |     |     | 5件  |

| 受賞実績  | 0   | 0   | 0   |     |     |     | 0件  |

| 特許出願  | 4   | 19  | 4   |     |     |     | 27件 |

※ : 平成22年度7月31日現在

特許は、ASETの発明審議会で審議後、各組合員(企業)が出願する。

## 三次元学会(3D IC:3D-SIC)の設立・運営

## **IEEE 3DIC 2010**

## International 3D System Integration Conference November 16-18, Munich

The IEEE International 3D System Integration Conference (3DIC) will be held at the "Fraunhofer Haus" in Munich in November 16-18, 2010.

This conference combines the previous ASET and IEEE EDS Society sponsored International 3D System Integration Conference, held in Tokyo in 2007 & 2008 and the IEEE CPMT sponsored 3D System Integration Conference held in 2003 & 2007 in Munich. After the first combined conference in San Francisco 2009, the 2nd IEEE 3D System Integration Conference will be held in Munich in 2010, rotate to Tokyo in 2011 and then rotate back to San Francisco in 2012.

Deadline for papers and proposals is July 1<sup>st</sup>, 2010. Abstracts are to be 500 words in length. Accepted papers will be due September 15<sup>th</sup>, 2010. www.3dic-conf.org

事業原簿 別紙 特許、論文等

13/25

3. 研究開発成果について (5)成果の最終目標の達成可能性

公開

## ①多機能高密度三次元集積化技術の目標と達成状況

## (1)次世代三次元集積化設計技術の研究開発研究開発

| 研究開発<br>テーマ                        | 最終目標<br>(平成24年度)                                                                  | 達成見通し                                                                                        |

|------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 1)電気系シミュレ<br>ーション技術の<br>研究開発       | ・現状に比較し2桁多いメッシュ数および8倍の<br>信号幅の解析対象を、現状と同等の計算時間で解析することができる電気系三次元シミュレータの開発と評価を完了する。 | ・最終目標を平成22年度に前倒しで達成し、<br>平成23年度以降は、プロジェクト参加企業内<br>で、開発したシミュレータの評価を行うととも<br>に、実用化のための研究開発を行う。 |

| 2)三次元デバイス<br>相互接続インターフ<br>ェース仕様の設定 | ・CMOS半導体デバイス、機能デバイス等を、<br>相互に接続可能とする機械的・電気的インタ<br>ーフェースを設定し、技術仕様書を策定する。           | ・実証デバイスの開発を通して、機械的・電気<br>的インターフェース仕様書を策定する計画で<br>あり、最終目標は達成見込み。                              |

## ①多機能高密度三次元集積化技術の目標と達成状況

#### (2)次世代三次元集積化のための評価解析技術の研究開発

| 研究開発<br>テーマ                            | 最終目標<br>(平成24年度)                                                                                                                                                                                                                                                                                                                     | 達成見通し                                                                                         |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 1)300mmウェハー<br>括プローブ方式の<br>研究開発        | ・300mmウェハに対応するプローブとして30万端子以上の被テスト端子への一括アクセスが可能であることを確認する。また、高速デジタル信号テスト端子においては、15Gbps以上の信号を用いた検査が可能であることを確認する。・平成22年度末までに開発したプローブをテスターと接続して評価を行い、プローブカードとテスト信号を含む4万系統のテスト信号を含む4万系統のテスト信号を含む4万系統のテスト信号伝送が可能であることを実証する。・一つのプローブカードにおいて、10kW以上の安定した電力供給技術を開発する。・プローブカードにおけるチップテスト時、温度範囲-40℃~+125℃においてバーンイン試験及びバーンイン試験を可能とする温度制御技術を開発する。 | ・最終目標を平成22年度に前倒しで達成し、平成23年度より、開発した技術について、プロジェクト参加企業内で実用化のための研究開発を行う。                          |

| 2)三次元集積化の<br>熱・積層接合評価<br>解析技術の<br>研究開発 | ・ひとつの三次元積層SiPあたり20W以上の<br>発熱に対応する放熱構造の評価解析技術<br>を開発する。                                                                                                                                                                                                                                                                               | -10μピッチ、10,000パンプ以上、20Wの放熱<br>技術の研究開発成果は、三次元積層SiPとして<br>の実証デバイスを通して行う計画であり、最終<br>目標は達成見込みである。 |

事業原簿III-2~41

3. 研究開発成果について (5)成果の最終目標の達成可能性

公開

## ①多機能高密度三次元集積化技術の目標と達成状況

# (3)次世代三次元集積化設計技術及び次世代三次元集積化のための評価解析技術の有効性実証

| 研究開発<br>テーマ                 | 最終目標<br>(平成24年度)                                                                                                                                                                                                                    | 達成の見通し                                                                                             |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1)次世代三次元<br>積層SiPの有効性<br>実証 | ・実用的なアプリケーション仕様に準ずる、Si貫通ビアを用いた三次元積層SiPを試作し機能を検証する。 ・実用的なアプリケーションを想定した実証用三次元積層SiP(実証デバイス)の第二ステップとして、センサ、ADコンバータを含む実証デバイス#2を試作し機能を検証する。(平成21年度実施方針)・実証デバイスにおいて、次世代三次元積層SiP、インターポーザ、外部基板まで含めた領域において、電気的特性による次世代三次元積層集積化設計技術の設計精度検証を行う。 | ・実証デバイス#1、実証デバイス#2とも、<br>三次元積層SiPを試作し機能を検証することは<br>可能であるが、チップレベルとなるか、ウェハレ<br>ベルとなるかは、今後の研究開発予算による。 |

## ②複数周波数対応通信三次元デバイス技術の目標と達成状況

## (1)複数周波数対応可変RF MEMSデバイスの研究開発

| 研究開発<br>テーマ                          | 最終目標<br>(平成24年度)                                                                                                         | 達成の見通し                                                                                                                                                          |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1)複数周波数対応<br>可変RE MEMSデバイス<br>の研究開発  | ・MEMSデバイスのスイッチ、キャパシタ、インダクタを<br>組み合わせ、700MHz~6GHzの周波数帯に含まれる<br>複数の通信方式で使用可能な可変アンテナ、<br>可変インピーダンス回路、可変フィルタのモジュールを<br>開発する。 | 研究開発は順調に進行している。今後はMEMS可変フィルタに関してデジタル可変化等の試作評価を行う。可変アンテナは三次元構造など携帯電話への実装に向けた小型化を進める。この成果を下配2)と組み合わせて最終目標を達成できると考えている。可変キャパシタ、可変インピーダンス回路は研究予算に応じてて可能な範囲で開発を実施する。 |

| 2)RF MEMSデパイス<br>三次元集積化実装技術<br>の研究開発 | ・MEMS回路、制御・電源回路を三次元集積化し、機能を実証する。さらに、シリコンLSIの積層によるSiP化のために必要な実装技術を開発する。                                                   | 研究開発は順調に進行している。今後は制御用ICの試作、<br>MEMS可変フィルタの特性を補完する回路の試作を<br>進めていく。TSV等ASETの三次元IC化技術を導入して、可変<br>フィルタやMEMSスイッチと組み合わせて最終目標を達成でき<br>ると考えている。                         |

#### (2)複数周波数対応通信フロントエンド回路の研究開発

| 研究開発<br>テーマ                                    | 最終目標<br>(平成24年度)                                                                                                                                                               | 達成の見通し                 |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1) 複数周波数対応<br>通信フロントエンド回路<br>MCMの研究開発と動作<br>実証 | ・複数周波数対応デバイスとして、MEMSデバイスをデジタル制御あるいはアナログ制御する制御回路デバイスを可能な限りLSI化し、700MHz~6GHzの周波数帯域をMEMSデバイスの可変域に対応して分割したMCMを開発する。このMCMにおいて、通信方式ごとの個別回路をMCM構成にて実装した場合に比較し、実装面積で1/8に小型化可能なことを実証する。 | 研究予算に応じて可能な範囲で開発を実施する。 |

| 2)複数周波数対応<br>通信三次元デバイス基<br>盤技術研究開発             | ・複数周波数対応通信三次元デバイスをSIP形態で実現するために必要な構成を提案する。                                                                                                                                     | 研究予算に応じて可能な範囲で開発を実施する。 |

事業原簿 I -42~70

3. 研究開発成果について (5)成果の最終目標の達成可能性

公開

## ③三次元回路再構成可能デバイス技術の目標と達成状況

#### (1)三次元回路再構成可能デバイスに関する三次元集積化技術の研究開発

| 研究開発<br>テーマ                                     | 最終目標<br>(平成24年度)                                                                                                                                          | 達成の見通し                                                      |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1)三次元回路再構成<br>可能デバイス配線構造<br>・ウェハ積層接合技術<br>の研究開発 | ・ウェハ接合技術として、200mm径以上のウェハを4層<br>以上積層し、1mm2程度の面積を占める三次元集積化<br>構造のコア間で、1000ピン以上の接続を実証する。<br>・高精度位置合わせ技術として、200mm径以上のウェ<br>ハを4層以上積層し、5 μm以下の位置合わせ精度を実<br>証する。 | ・2層積層技術で実証された技術を発展させ、最終目標である4層以上積層で求められる技術スペックを達成できる見込みである。 |

## (2)三次元回路再構成可能デバイスに関するアーキテクチャおよび設計技術の研究開発

| 研究開発<br>テーマ                                        | 最終目標<br>(平成24年度)                                                                                                                                     | 達成の見通し                                                                                                                                                                                                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1)三次元回路再構成<br>可能デバイスアーキテ<br>クチャおよび設計技術<br>の研究開発と実証 | ・動的リコンフィギャラブルプロセッサ、FPGA、汎用<br>CPU、メモリ等の機能ブロックを柔軟に組み合わせた<br>ハイブリッドアーキテクチャを開発する。さらに、200m<br>m径以上のウェハ積層技術を用いて4層以上積層し、<br>三次元回路再構成可能デバイスとしての動作を実証<br>する。 | ・現在までに、研究開発は順調に進行している。今後は、ハイブリッドアーキテクチャの設計、三次元FPGAおよびスケーラブルリコンフィギャラブルIOプロセッサの設計を行い、4 層積層において、消費電力当たりの性能が従来比1.25 信以上となること実証する。また、TEG評価により通信回路の構築を行う。・基本回路は既に完了しており、今年度中にモジュール設計を完了することにより確実に最終目標達成が可能である。 |

事業原簿 I -71~88

# 発表内容

- 1. 事業の位置づけ・必要性

- 2. 研究開発マネージメント

- 3. 研究開発成果

- 4. 実用化、事業化の見通し

19/25

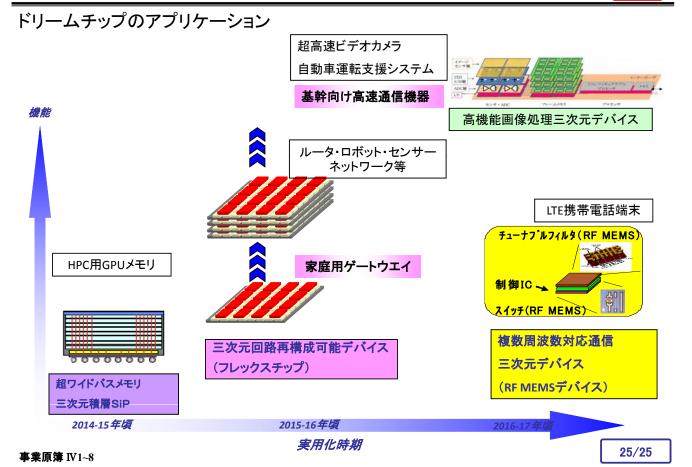

4. 実用化、事業化の見通しについて (1)成果の実用化可能性

公開

- ①多機能高密度三次元集積化技術の成果

- (1)次世代三次元集積化設計技術の研究開発

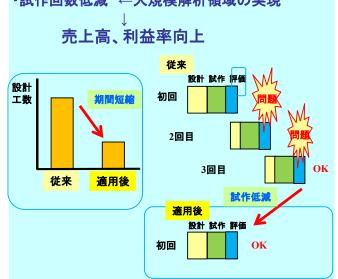

- 参加各企業にて実用化し、下記の成果を得る ・設計期間短縮 ←シミュレーション時間短縮

1)電気系三次元シミュレーション技術の研究開発

·試作回数低減 ←大規模解析領域の実現

2)信号品質安定化技術(SI)・電源安定化技術(PI) の研究開発

【プロジェクト成果】

高性能素子内蔵インターポーザ 設計ガイドライン

内蔵素子高精度評価 · 検査手法 基本技術\_\_\_ 製品や開発環 ・ 境に依存しな い工学的知見

【実用化課題】

- ・各社の開発環境への移植

- ・量産プロセス開発

- ・アプリケーション開発

【実用化·事業化可能性】

- ・従来型インターポーザへの適用 →三次元集積SiP用インターポーザ (PKG/基板メーカー)

- ・受託生産 (ファウンダリ)

企業にて開発

## ①多機能高密度三次元集積化技術の成果

#### (2)次世代三次元集積化のための評価解析技術の研究開発

#### 1)300mmウェハー括プローブ方式の 研究開発

- 1)次世代三次元積層SiPのみならず、現行デバイスにも使用できるKGDを低テストコストで提供することを目指す。

- 2)すでに一部技術を適用した 300mmウェハー括試験装置の実 用化検討が開始している。

#### 2)三次元集積化の熱·積層接合 評価解析技術の研究開発

- 設計時の熱シミュレーションによるチップ積層デザインの効率化

- 積層構造の機械ストレスや微細 金属物性、の新たな知見に基づ く、信頼性の高い三次元実装構 造と材料選択を可能とする設計 技術への寄与

- ・微細接合部解析技術の装置メーカー製品展開への寄与

#### 3)薄化ウェハ評価解析技術の研究開発

- ・極薄ウェハ加工、及び極薄チップピックアップ技術においては、一部の新規開発材料を除いて市販の材料、装置、プロセス技術をベースに研究開発を実施。・デバイスの特性評価技術についても、通常の、C-t測定法やレーザラマン顕微鏡を用いた解析技術により定量的に評価できることを検証した。

- ・本研究開発は世界最先端のレベルであるものの、コスト的にも量産化を強く意識 した開発であり、半導体事業分野での実 用化の可能性は高い。

21/25

#### 事業原簿 IV-1~4

#### 4. 実用化、事業化の見通しについて (1)成果の実用化可能性

公開

## ①多機能高密度三次元集積化技術の成果

#### (3)次世代三次元集積化設計技術及び次世代三次元集積化のための評価解析技術の有効性実証

#### (a)実証デバイス#1

- ・メモリとロジックを4k-IOの超 ワイドバスで接続する構造を 実現した。

- ・超多ピン接続による信号授 受仕様、ノイズ低減技術は未 整備であり、世界標準を目指 す知財網構築が可能となって いる。

- ・応用分野としては、まずハイ エンドグラフィックスであり、次 にスパコン、サーバ、医療機 器、自動車などの安全運行制 御機器などに展開されうる。

# 性能 画像取り込み: 10,000フレーム/秒

(b)実証デバイス#2

画像サイズ: VGA仕様

産業機器

#### (C)実証プロセス

- ・300mmウェハのTSVプロセスや、積層 プロセスのインフラストラクチャは、世界中 をみても整っていない。

- ・実証プロセスで構築したプロセスや技術 は、参画企業が持ち帰り、三次元デバイス の試作・量産化技術として、活用する。

#### 300mmW2W積層技術

Via Last/Back Via方式TSV

## ②複数周波数対応通信三次元デバイス技術

(1)複数周波数対応可変RF MEMSデバイスの研究開発 (2)複数周波数対応通信フロントエンド回路の研究開発

・SDR用LSIと組み合わせ、世界中の通信 方式、通信周波数にソフトウエアの変更だけ で対応可能な携帯電話が実現。

•2013年以降本格普及する3. 9G(LTE)やその後のIMT advanced, 無線LANを狙う。

事業原簿IV-5~6

4. 実用化、事業化の見通しについて (1)成果の実用化可能性

公開

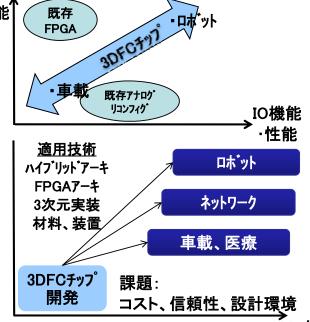

## ③三次元回路再構成可能デバイス技術

(1)三次元回路再構成可能デバイスに関する 三次元集積化技術の研究開発

演算 1/TSV容量 性能 (∝ TSV伝送速度) 数十fF 3DFC メモリ・ロシック 混載 数百fF 大容量メモリ 展開先: 3DFC, メモリ, ロジック混載 材料・装置 数千fF ワイヤ ボンド → 接続本数 1K 10K 100K (cm<sup>-2</sup>)

#### 三次元集積化の実用化

- ・三次元回路再構成可能デバイス(2014~)

- ・大容量メモリ、メモリ・ロジック混載への展開(2013以降)

- ・三次元デバイスのための装置・材料へ展開

(2)三次元回路再構成可能デバイスに関するアーキテクチャおよび設計技術の研究開発

2010年 2012年 2014年 2016年 2018年

## 4. 実用化、事業化の見通しについて (3)波及効果