「立体構造新機能集積回路 (ドリームチップ)技術開発」 (事後評価)第1回分科会 資料 5-1

「立体構造新機能集積回路(ドリームチップ)技術開発」

事業原簿

【公開版】

担当部

独立行政法人 新エネルギー・産業技術総合開発機構 電子・材料・ナノテクノロジー部

# 概要

# プロジェクト用語集

| 1.   | 事業の位置付け・必要性についく      |                                                 |              |

|------|----------------------|-------------------------------------------------|--------------|

| 1.   | NEDOの関与の必要性・制度への適合   | 生                                               | I -1         |

|      | 1.1 NEDOが関与することの意義   | •••••                                           | I -1         |

|      | 1.2 実施の効果(費用対効果)     | •••••                                           | I -2         |

| 2.   | 事業の背景・目的・位置づけ        | •••••                                           | I -3         |

|      | 2.1 事業の背景            |                                                 | I -3         |

|      | 2.2 事業の目的            | •••••                                           | I -4         |

|      | 2.3 事業の必要性と意義        |                                                 | I -5         |

|      | 2.4 事業の指針            |                                                 | I -6         |

| Ⅱ.₹  | 研究開発マネジメントについて       |                                                 |              |

| 1.   | 事業の目標                |                                                 | ∏ -1         |

| 2.   | 事業の計画内容              |                                                 | П-3          |

|      | 2.1 研究開発の内容          |                                                 | П-3          |

|      | 2.2 研究開発の実施体制        |                                                 | П-3          |

|      | 2.3 研究開発の運営管理        |                                                 | Ⅱ-5          |

|      | 2.4 研究開発の実用化・事業化に向け  | たマネジメントの妥当性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | Ⅱ -5         |

| 3.   | 情勢変化への対応             |                                                 | Ⅱ -6         |

| 4.   | 中間評価結果への対応           |                                                 | Ⅱ -6         |

| 5.   | 評価に関する事項             | •••••                                           | П-10         |

| Ⅲ. Ā | 研究開発成果について           |                                                 |              |

| 1.   |                      |                                                 | III - 1      |

| 2.   | 研究開発項目ごとの成果の概要       |                                                 | Ш-2          |

| 2.   | 1 多機能高密度三次元集積化技術     |                                                 |              |

|      | (1)次世代三次元集積化設計技術の研究開 |                                                 |              |

|      | (1)-A 設計環境技術の研究開発    |                                                 | <b>Ⅲ</b> −31 |

|      |                      |                                                 | Ⅲ-36<br>Ⅲ-41 |

|      | (2)次世代三次元集積化のための評価解析 |                                                 | ш-41         |

|      | (2)-A チップテスト技術の研究開発  |                                                 | <b>Ⅲ</b> -44 |

|      | (2)-B 熱・積層接合技術の研究開発  |                                                 | Ш-2          |

|      | (2)-C 薄ウェハ技術の研究開発    | •••••                                           | Ш-7          |

|      | 成果一覧                 | •••••                                           | <b>Ⅲ</b> −11 |

| (3)次世代  | 弋三次元集積化の共通要素技術開    | 発と設計基準策定      | Ē                                       |              |

|---------|--------------------|---------------|-----------------------------------------|--------------|

| (3)-A   | 実証デバイス研究開発         | ⇒平成22年度で終     | 終了(※)・・・・・・・・・・・                        | <b>Ⅲ</b> −48 |

| (3)-B   | 3Dインテグレーション技術の研究   | 開発・           | • • • • • • • • • • • • • • • • • • • • | Ш−11         |

| (3)-C   | 超ワイドバスSiP三次元集積化技術  | 析の研究開発 ・      | • • • • • • • • • • • • • • • • • • • • | Ш-16         |

| (3)-D   | デジアナ混載三次元集積化技術     | の研究開発         | • • • • • • • • • • • • • • • • • • • • | <b>Ⅲ</b> −21 |

| (3)-E   | ヘテロジーニアス三次元集積化技    | で術の研究開発       | • • • • • • • • • • • • • • • • • • • • | <b>Ⅲ</b> −26 |

| 成果-     | 一覧                 |               | •••••                                   | <b>Ⅲ</b> −30 |

| 2.2 複数  | 周波数対応通信三次元デバイス技    | 交術            | ⇒平成22年度で終了                              | (※)          |

| (1)複数   | 周波数対応可変RF MEMSデバイン | スの研究開発        | •••••                                   | <b>Ⅲ</b> −55 |

| (2)複数   | 周波数対応通信フロントエンド回路   | 8の研究開発        | •••••                                   | <b>Ⅲ</b> -58 |

| 2.3 三次  | 元回路再構成可能デバイス技術     |               | ⇒平成22年度で終了                              | (※)          |

| (1)三次   | 元回路再構成可能デバイスに関す    | るアーキテクチャ      | • • • • • • • • • • • • • • • • • • • • | <b>Ⅲ</b> -60 |

| およ      | び設計技術の研究開発         |               |                                         |              |

| (2)三次   | 元回路再構成可能デバイスに関す    | る三次元集積化技      | 技術の・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | <b>Ⅲ</b> −63 |

| 研究      | 5開発                |               |                                         |              |

| (※)について | 「は、中間評価にて評価済みのため   | )、『付録』(Ⅲ-31 』 | 以降)に掲載しておりまっ                            | す。           |

| Ⅳ 実用化・事 | 事業化の見通し及びその取り組みに   | こついて          | • • • • • • • • • • • • • • • • • • • • | •••IV-1      |

| 1. 成果   | の実用化・事業化の見通し       |               | •••••                                   | •••IV-1      |

| 2. 実用   | 化・事業化への取り組み        |               | • • • • • • • • • • • • • • • • • • • • | •• IV-4      |

別紙:

特許、論文等 プログラム基本計画 プロジェクト基本計画

# 概要

|                        | 作成日 平成25年6月28日                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| プログラム名                 | ITイノベーションプログラム                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| プロジェクト名                | 立体構造新機能集積回路(ドリームチップ)技術開発 プロジェクト番号 P08009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 担当推進部/担当者              | 者 電子・材料・ナノテクノロジー部/小林丈夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0. 事業の概要               | 半導体チップの積層技術(三次元集積化技術)は、世界に先駆けてNEDOが取り組んできたもので、研究開発実績としては我が国に優位性がある。この三次元集積化技術の完成度を高め、さらなる産業競争力強化に寄与するために、新たな機能の発揮と飛躍的な性能向上を実現する立体構造新機能集積回路技術を確立することを目的とする。内容としては、以下の3項目に関する技術開発を実施する。 ①多機能高密度三次元集積化技術 ②複数周波数対応通信三次元デバイス技術※ ③三次元回路再構成可能デバイス技術※ ※②、③は中間評価後見直しを行い①に統合および早期終了した。                                                                                                                                                                                                                                                   |  |  |  |  |  |

| I. 事業の位置付け・<br>必要性について | 我が国半導体技術の発展は、様々な機器の高性能化、小型化、省電力化に貢献し、情報通信産業や製造業といった我が国経済を牽引する産業の競争力を強化するものである。この発展を支える半導体デバイスの製造技術として、従来のCMOS-LSI用プロセス技術を二次元的に微細化する取り組みに加え、半導体集積化としてチップの積層構造(三次元的な構造)を採用する取り組みが顕在化してきている。この技術は、世界に先駆けてNEDOが取り組んできたものであり、研究開発実績としては今のところ我が国に優位性がある。今後、各国との開発競争が熾烈化するなかで、現在の三次元集積化における我が国の技術優位性を維持し、産業競争力を強化するためには、先進的な技術開発でありながら、業界におけるデファクト標準化を視野に入れた取り組みを行う必要がある。先進的な技術開発を行うためには、我が国産業界の強い製造力と大学や公的研究機関の先端的な知見の有機的結合が有効であり、また将来のデファクト標準化を円滑に進めるには研究開発の早い段階から共通基盤技術として完成度を高めることが望ましい。このことから、本研究開発は、NEDOの事業として、強力に推進することが必要である。 |  |  |  |  |  |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 事業の目標                  | ① 多機能高密度三次元集積化技術 ① - 1.次世代三次元集積化設計技術の研究開発 ・信号、パワー等のシミュレーション技術の開発(中間評価で評価済) ① - 2.次世代三次元集積化のための評価解析技術の研究開発 ・20W以上のチップ発熱に対応する放熱構造の評価解析技術の開発 ・車載環境での放熱冷却構造の最適化設計と、評価解析技術の開発 ・車載環境での放熱冷却構造の最適化設計と、評価解析技術の開発 ・要素技術の設計・レイアウト・プロセス工程のライブラリ開発 (TSV 加工、積層、中間処理など) ・ノイズ対応素子内蔵インターポーザの設計基盤技術を開発 ・多層積層における電源供給技術、高速信号伝送技術の開発 ・ロジックとメモリ積層時の高伝送能力、低消費電力の実現 ・各要素技術の設計基準の作成 ②複数周波数対応通信三次元デバイス技術 ① - 3 に統合 ③ 三次元回路再構成可能デバイス技術 ・3D プロセス技術 → ① - 3 に統合 ・回路再合成アーキテクチャ開発、素子技術の研究開発 → 早期終了                                                           |  |  |  |  |  |

| 事業の計画      | 画内容                         | 主な実施項目                                                                                                                                           | H20fy                                  | H21fy                            | H22fy                        | H23fy                            | H24fy                                   |                                  |

|------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|------------------------------|----------------------------------|-----------------------------------------|----------------------------------|

|            |                             | ①多機能高密度三次元集<br>積化技術<br>(1)設計技術                                                                                                                   |                                        |                                  | <b></b>                      | 目標を迫                             | <br> <br> <br> <br> <br> <br> <br> <br> | 月終了                              |

|            |                             | (1)設計投納<br>(2)評価解析技術                                                                                                                             |                                        |                                  |                              |                                  | <b></b>                                 |                                  |

|            |                             | (3)共通要素技術開発と設計                                                                                                                                   |                                        |                                  |                              |                                  |                                         |                                  |

|            |                             | 基準策定                                                                                                                                             |                                        |                                  |                              |                                  | <b></b>                                 |                                  |

|            | 次元デバイス技術<br>(1)可変 RF MEMS 積 | ②複数周波数対応通信三<br>次元デバイス技術<br>(1)可変 RF MEMS 積層技術<br>(2)通信フロントエンド回路                                                                                  |                                        |                                  | <b></b>                      | H23 J                            | にり①-3 とá                                | <b>売</b> 合                       |

|            |                             | の研究開発                                                                                                                                            |                                        |                                  | <b></b>                      | 早期約                              | K<br>多了                                 |                                  |

|            |                             | ③三次元回路再構成可能                                                                                                                                      |                                        |                                  |                              |                                  |                                         |                                  |

|            |                             | デバイス技術                                                                                                                                           |                                        |                                  | <b> </b>                     | H23 a                            | <b>たり①−3と</b>                           | 統合                               |

|            |                             | (1)3D プロセス技術<br>(2)回路再合成アーキテクチ                                                                                                                   |                                        |                                  |                              | 早期約                              | ·                                       |                                  |

|            |                             | ャ開発<br>(3)素子技術の研究開発                                                                                                                              |                                        |                                  |                              |                                  |                                         |                                  |

|            |                             | (C)XX 1 DXXII S SI DEDIGO                                                                                                                        |                                        |                                  | ·                            | 早期組                              | 終了                                      |                                  |

| 開発予算 (百万円) |                             | 会計・勘定<br>(補正予算分含む)                                                                                                                               | H20fy                                  | H21fy                            | H22fy                        | H23fy                            | H24fy                                   | 総計                               |

|            |                             | 一般会計                                                                                                                                             | 1,700                                  | 2,452                            | 1,740                        | 1,661                            | _                                       | 7,553                            |

|            |                             | 特別会計                                                                                                                                             | _                                      | _                                | _                            | _                                | _                                       | _                                |

|            |                             | 執行額                                                                                                                                              | 1,086                                  | 2,229                            | 1,614                        | 1,153                            | 1,271                                   | 7,353                            |

| 開発体制       | 開発体制                        | 経済産業省原課                                                                                                                                          | 商務情報政策局 情報通信機器課                        |                                  |                              |                                  |                                         |                                  |

|            |                             | プロジェクトリーダー                                                                                                                                       | 東京工業大学 教授 益 一哉                         |                                  |                              |                                  |                                         |                                  |

|            |                             | 委託先 技術研究組合 超先端電子技術開発機構                                                                                                                           |                                        |                                  |                              |                                  |                                         |                                  |

| 情勢変化対応     | ~の ¯                        | 本プロジェクトは、H22 年度<br>し三次元積層に関する要素<br>研究開発項目②-(1) 可変 R<br>①-(3)3D プロセス技術を研<br>(2)、③-(3)は早期終了とした。<br>また、平成23年度に、三次<br>ンを実現する為に加速予算の<br>に関する研究開発を強化した | 支術開発(F MEMS<br>字開発項。<br>元積層技<br>追加(100 | こより重点<br>積層技術<br>[目①-(3)<br>術の事業 | を置いた<br>及び研究<br>に統合し<br>化の大き | 目標に変開発③-(<br>開発③-(<br>、研究開発な課題とな | 更した。こ<br>(1)を研究 <br>発項目②-<br>さっている      | れにより<br>開発項目<br>-(2)、③-<br>コストダウ |

## Ⅲ. 研究開発成果に ついて

本研究開発に於いては、多機能高密度三次元集積化の次世代に向けた基盤技術構築のため、(1)設計技術、(2)評価解析技術、(3)共通要素技術開発と設計基準策定、を対象として研究開発を進めた。

(1) 次世代三次元集積化設計技術の研究開発

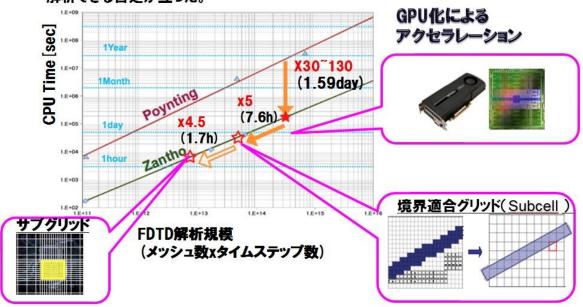

この研究開発項目の成果としては、回路シミュレータ、電磁界シミュレータ技術に於いて並列法や新規アルゴリズムの導入により、何れも既存技術(平成22年度時点)の500~800倍の性能を達成。更に回路品質・電源品質安定化回路技術に於いては、デジタル・アナログ混載回路や多電源化に対応したインターポーザと有機基板のコンカレント設計モデルを策定し有効性を確認した。また CMOS デバイスと他の機能デバイスを相互接続するインターフェース仕様を策定し成果を挙げた。尚、本テーマは平成22年度に終了し、中間評価にて評価済みである。

(2) 次世代三次元集積化のための評価解析技術の研究開発

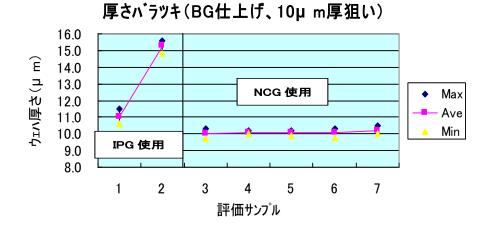

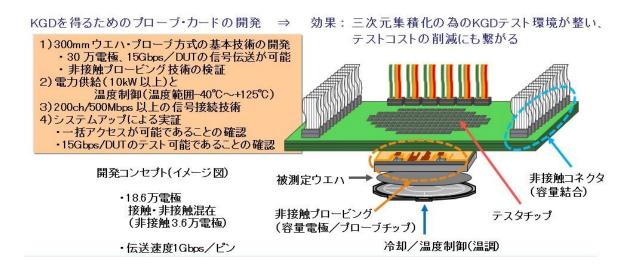

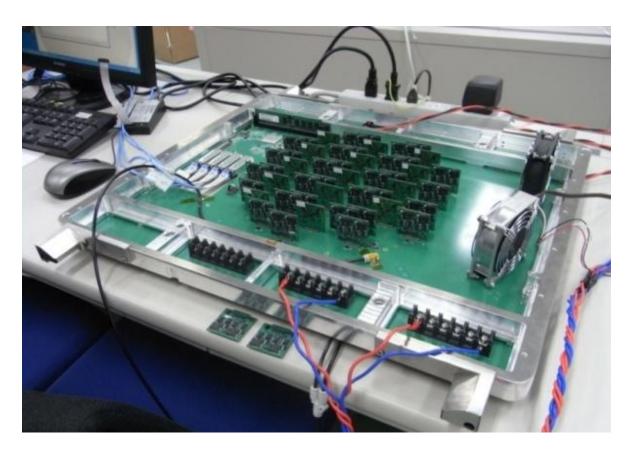

この研究開発項目の成果としては、チップテスト分野に於いて 300mm ウェハへの 30 万端子以上の一括アクセスを可能とする技術の開発に取り組み、大気圧加重による接触端子と容量結合による非接触端子との組み合せがもつ可能性を確認し、試験用に 18.6 万端子のプローブカードを試作し稼働を確認した。また、この技術を用いたウェハテスト/バーンイン動作のための温度制御技術(気化熱利用の冷却)を併せて開発した(本技術開発は平成 22 年度に前倒し達成・終了し、中間評価済みである)。更に、熱・積層接合分野の開発として、三次元積層構造体の 20W 以上の発熱に対応する放熱構造の評価解析を対象とし、熱伝導パラメータ抽出手法とシミュレーションを中心とした高精度の熱特性評価手法を確立した。また、併行してウェハの高精度薄化技術と極薄チップの加工技術に取り組み、10μm 厚のウェハ加工、ダイシング、チップ積層工程の効率化を可能とする開発を行った。

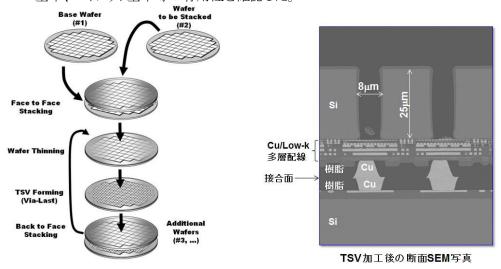

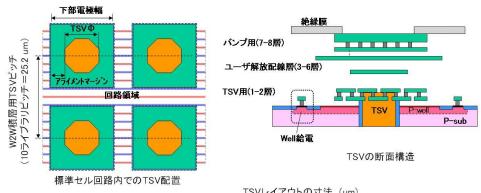

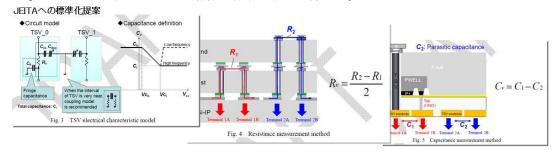

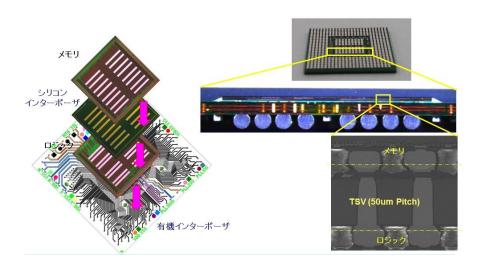

(3) 次世代三次元集積化の共通要素技術開発と設計基準策定

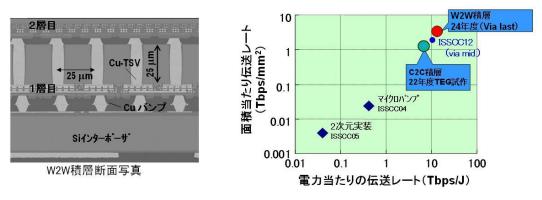

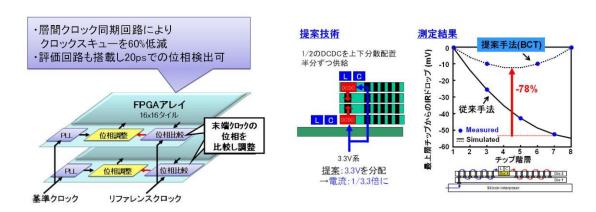

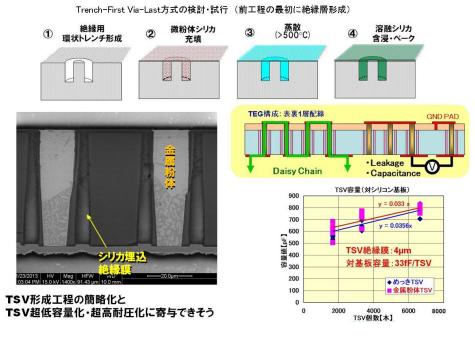

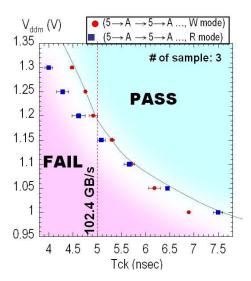

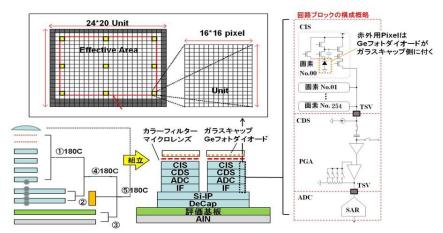

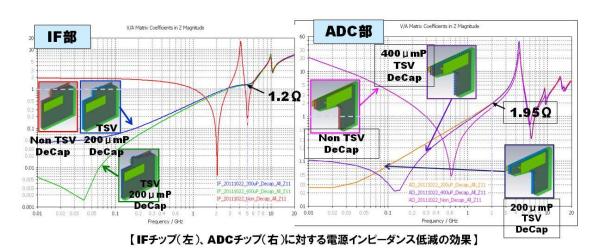

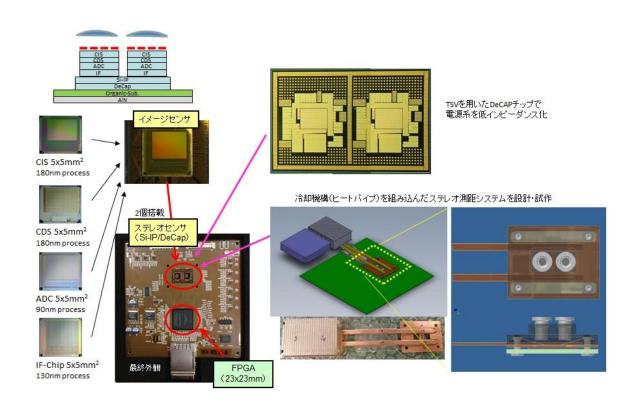

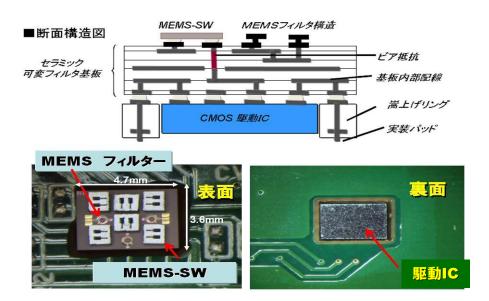

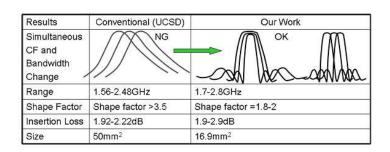

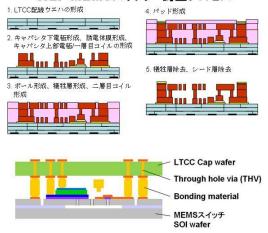

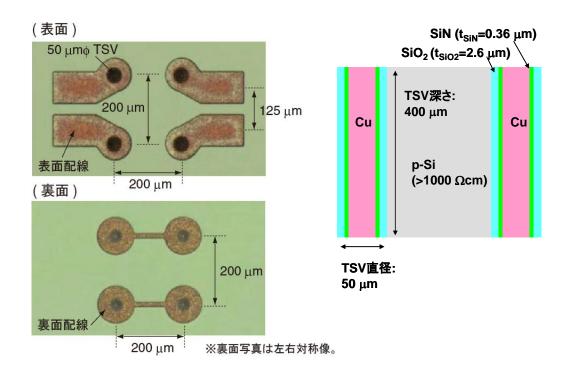

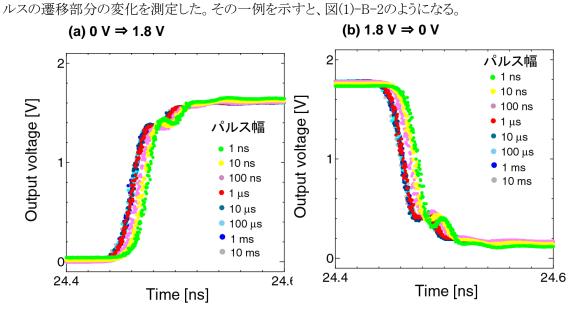

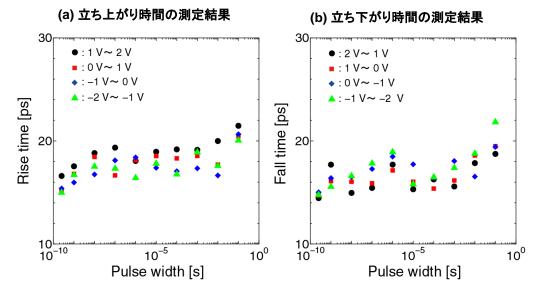

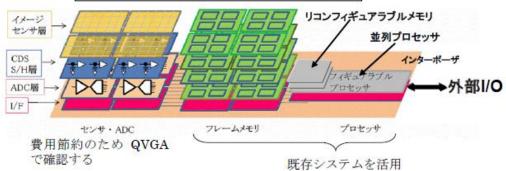

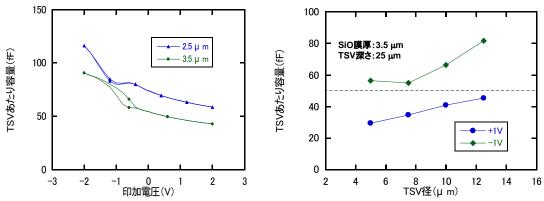

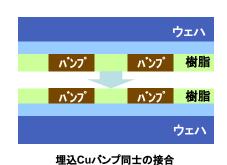

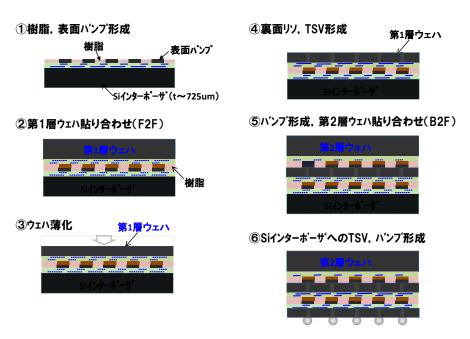

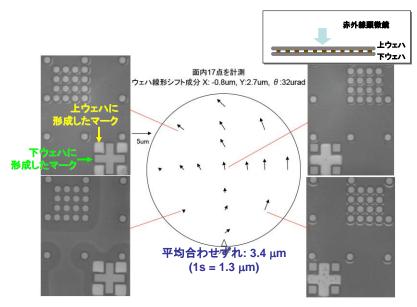

この研究開発項目の成果としては、TSV(シリコン貫通電極)を始めとする共通要素 に関わる設計基準・レイアウト基準・プロセス工程基準策定に取り組み、25µm ピッチ及 び 50µm ピッチの標準 TSV セル構造を開発してライブラリ化した。また積層 LSI の設 計・試作・評価により、加工対象を柔軟に選択できる Via-Last プロセスと、積層工程の 効率を改善する W2W 積層プロセスに関連する、各種レイアウト基準・プロセス基準を 策定し、更に、積層チップ間同期回路方式や積層構造への電源供給手段の改善など 回路設計面での開発も行った。また、三次元積層構造の特徴を最大限活かす超ワイド バスによるメモリとロジックの相互接続の可能性を探り、4,096 本の信号端子を 200Mbps 以上で動作させ、102GB/sec という従来比 8 倍以上の信号伝送能力と、そ の際のエネルギー消費が 0.56pJ/bit と大幅な低消費電力化を確認した。また、微粉体 シリカをTSV 絶縁膜として活用する技術開発にも取り組み、TSV 浮遊容量の大幅低減 とコストダウンの可能性を確認した。更に、アナログ素子(CIS)とデジタル素子(ロジッ ク)を組み合わせる画像処理システムの開発を通じて、車載環境下での安定動作のた め TSV をデカップリング・コンデンサとしても活用して電源品質の改善を図る技術開発 や、画像センサモジュールとしてCIS/CDS/ADC/IFチップの積層体を開発し、これを2 個用いる高度な自動車運転支援画像システムの評価を行った。また、非シリコン系三 次元積層構造の可能性として、LTCC(低温焼結セラミック)基板を用いた MEMS 可変 フィルタと WLP MEMS スイッチと制御 IC を積層して、三次元集積化 RF モジュール を試作・評価し、三次元構造化によって、中心周波数と帯域幅の制御が効果的に行え ることを確認した。こうした多岐にわたる開発により、先進的かつ実際的な開発成果を挙 げた。

| 投稿論文 | 23件                    |

|------|------------------------|

| 学会発表 | 377件                   |

| その他  | プレス発表 1件、講演など11件       |

| 特許   | 出願済: 144 件 (うち国際出願64件) |

#### IV. 実用化・事業化の 見通しについて

本事業では、三次元積層に関する「TSV形成技術」「チップ積層技術」「設計技術」「評価技術」「材料技術」の要素技術を開発した。本事業の主体となった技術組合ASE Tに参加した企業は事業に必要な技術要素を持ち帰り各社で事業化にむけた開発を継続する計画となっている。その適用範囲は広く、製造装置、半導体チップ、モジュール、IT機器事業などに採用される見通しである。また対象分野もモバイル製品からIT機器、ヘルスケア、車載電装品と幅広い。事業化については平成 28 年度~32 年度にかけてそれぞれの業界特性に応じて順次上市の見込みである。

| V. 評価に関する事<br>項 | 事前評価   | 平成 20 年度実施(担当部:電子·情報技術開発部)                                                          |  |  |

|-----------------|--------|-------------------------------------------------------------------------------------|--|--|

|                 | 中間評価以降 | 平成22年度8月実施                                                                          |  |  |

| VI. 基本計画に関す     | 作成時期   | 平成 20 年 3 月制定                                                                       |  |  |

| る事項             | 変更履歴   | 平成20年7月 イノベーションプログラム基本計画の制定により改訂<br>平成21年3月 研究開発項目③目標設定のため改訂<br>平成22年7月 中間成果記載のため改訂 |  |  |

# プロジェクト用語集

| 用語          | 説明                                                     |

|-------------|--------------------------------------------------------|

| hna         | Bit Per Second の略称。1 秒間に伝送されるデジタル信号の量で定義される数           |

| bps         | 値で、この値が大きい信号ほど高速な信号とされる。                               |

|             | 電源回路の一種で、直流電圧を異なる直流電圧へ変換する。回路部品として                     |

| DC-DC コンバータ | だけではなく、LSI 上にも分散的に配置・集積化し、LSI 内部の機能ブロックや               |

|             | それらの動作状況に応じた柔軟な電源電圧の制御を可能としている。                        |

| EMC歌伍       | Electric Magnetic Compatibility 電子機器からの電磁波の発生具合を評価す    |

| EMC 評価      | ること。                                                   |

| EDTD >+     | Finite Difference Time Domain 電磁気の基本方程式である、マクスウェル方程    |

| FDTD 法      | 式を差分化し、時間領域で解く方法。                                      |

| Hz (ヘルツ)    | 周波数の単位。IC チップが 1 秒間に信号を送受信する回数を表す。現在一般                 |

| HZ (*\/V)   | 的な IC チップでは、1Hz の信号は 2bps に相当する。                       |

| LIM         | Latency Insertion Method 回路計算のアルゴリズムの一種。               |

|             | Metal Insulation Metal の略称。主に半導体チップにおいて、金属(Metal)と金    |

| MIM         | 属(Metal)が絶縁膜(Insulator)を挟み込んだ構造になっているキャパシタのこ           |

|             | と。                                                     |

| MOC DET     | 電界効果トランジスタ(FET)の一種で、Metal-Oxide-Semiconductor          |

| MOS FET     | Field-Effect Transistorの略。LSIの中では最も一般的に使用されている構造。      |

|             | System in Package の略称。SoC(System on Chip)に対応する言葉で、1パッケ |

| SiP         | ージ内に複数のICチップが収納されてパッケージとしてシステムの機能を持つ                   |

|             | 半導体製品。                                                 |

|             | Simultaneous Switching Output の略称で、複数のデータ出力ピンが同時に動     |

| SSO         | 作する事を示す。この動作時には、出力ピンの数が増えると、この負荷を駆動                    |

| 330         | する為に大電流が流れ、これが素子の電源ノイズや内部動作の不安定性を誘                     |

|             | 発する可能性があり、設計・評価上、重要な項目となっている。                          |

| VNA         | Vector Network Analyzer(ベクトル・ネットワーク・アナライザ)の略。高周波回路     |

| VINA        | 網の通過・反射電力の周波数特性を測定する測定器。                               |

| アルゴリズム      | 計算の順番を決める考え方。                                          |

|             | 端子ピッチや配置が異なる LSI と配線基板との接続に用いられる中継用の配                  |

| インターポーザ     | 線基板。一般には、基材として有機材料(樹脂)が主に使用されているが、シリ                   |

|             | コン(Si)を基材として微細配線形成や素子内蔵が可能な形態のインターポー                   |

|             | ザは Si インターポーザとよばれる。                                    |

| エレクトロ・マイグレ  | 電気が流れることにより、配線を形成している材質の粒子が影響を受けること。                   |

| ーション        | 电水(パイクルムレのことにより、印がたかがたい)以している内 貝の位すが予告を又けること。          |

| コンデンサ、キャパ   | 電力を蓄えることができる電子部品。二次電池は化学的に電力を蓄えるのに                     |

| シタ          | 対し、コンデンサは電力を電界の形で蓄える。                                  |

| 1. 18. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. | ○・ 1.1. · · /片日日除) がいた。片日のマポトピル)。日/畑 しゃた日のは      |

|-----------------------------------------------|--------------------------------------------------|

| シグナル・インテグリ                                    | Signal Integrity (信号品質)。デジタル信号の正確な伝送に影響する信号の特    |

| ティ(SI)                                        | 性。例として、信号波形の歪み、タイミングのずれなど。                       |

| 次世代 SiP                                       | 従来のダイボンド、ワイヤボンド法ではなく、シリコン貫通電極(TSV)等を利用<br>       |

|                                               | して実現した SiP。                                      |

| シミュレーションエンジン                                  | 技術計算を実施するソフトウェアのこと。                              |

|                                               | 二つの回路間で送受信されるデータを、一本の配線を使って伝送する方式。               |

| シリアル(伝送)                                      | 配線が高速信号に対応した設計であれば、少数の配線で大量のデータを伝                |

|                                               | 送できるので、IC チップ・インターポーザ内の配線配置が容易になる。               |

| 線形エンジン                                        | 抵抗等の線形回路素子を計算するソフトウェア。                           |

| 線形部                                           | 抵抗等の線形素子を有する回路部。                                 |

| タイムステップ数                                      | 解析対象物の最小単位を解析する時間のこと。                            |

| -1°-±17 □                                     | 電子部品のうち、規格に基づいた寸法の直方体形状を持ち、表面に実装用の               |

| チップ部品                                         | 電極を備えたもの。                                        |

| デカップリング・コン                                    | 電源回路に接続されるコンデンサ。IC チップが動作した際の電源電圧変動を             |

| デンサ                                           | 抑制する役割がある。                                       |

| ドライバ                                          | ある回路の外部へ信号を出力する機能を持った回路要素。                       |

| ************************************          | IC チップ製造で用いる薄膜形成技術を応用し、キャパシタや抵抗など通常の             |

| 薄膜素子                                          | 電子部品と同等の機能を持つ構造を作りこんだもの。                         |

| 波形緩和法                                         | 複数の波形の中間を計算すること。                                 |

|                                               | 二つの回路間で送受信されるデータを、複数の配線を使って伝送する方式。               |

| パラレル(伝送)                                      | シリアル伝送に比べて低速な信号でも、大量のデータを伝送できることから、IC            |

|                                               | チップの回路設計が容易になる。                                  |

| プロ ハニガリニ                                      | Power Integrity (電源品質)。インターポーザを経由して IC チップに供給される |

| パワー・インテグリテ                                    | 電源の品質を指す用語で、電源の電圧の安定性が指標となる。電圧変動が小               |

| イ(PI)                                         | さい電源ほど、品質は良好である。                                 |

| 非線形エンジン                                       | MOS トランジスタ等の非線形回路素子を計算するソフトウェア。                  |

| 非線形部                                          | MOSトランジスタ等の非線形素子を有する回路部。                         |

| <b>*</b> 工學學                                  | インターポーザに部品を実装する手法の一つ。インターポーザ表面に設けられ              |

| 表面実装                                          | た電極に部品を搭載し、はんだなどで接続する技術。                         |

|                                               | インターポーザに部品を実装する手法の一つ。表面まで部品実装用の配線を               |

| 部品内蔵                                          | 引き出す代わりに、内部配線に部品を接続する。部品はインターポーザの内               |

|                                               | 部に組み込まれ、表面からは視認・検査できない。                          |

| ブロック LIM                                      | Block Latency Insertion Method 回路計算のアルゴリズムの一種。   |

| 並列化計算                                         | 複数の演算器を同時に動かして計算すること。                            |

| メッシュ                                          | 解析対象物を複数に分割する最小の大きさ。                             |

| モジュール                                         | 所望の機能を得るため、複数の部品を組み合わせた構成単位。(例えば、イン              |

| <u> </u>                                      |                                                  |

|                | ターポーザに IC チップ・コンデンサを実装した構造)                                                                          |

|----------------|------------------------------------------------------------------------------------------------------|

| 連成             | 異なるソフトウェアを情報を交換しながら同時に動かすこと。                                                                         |

| Arrhenius plot | 温度に対する反応速度変化をプロットし、寿命予測を行う手法。                                                                        |

| ASIC           | [英]Application Specific Integrated Circuit の略。電子部品の種別の一つで、特定の用途向けに複数機能の回路を 1 つにまとめた集積回路(IC)の総称をいう。   |

| CAE            | Computer Aided Engineering: コンピュータによって製品の設計、製造や工程<br>設計の事前検討の支援を行うこと、またはそれを行うツール。                    |

| СТ             | Computer Tomography: 様々な角度から撮像した(X線)像をコンピュータ処理することに依って断層画像を得る方法。                                     |

| DUT            | [英]Device Under Test の略。テストの対象となる半導体チップを指す。                                                          |

| EDX            | Energy dispersion X-ray analysis: エネルギー分散型 X 線分光器を用いた元素分析法。SEM で元素分析を行うのに適している。                      |

| EG             | Extrinsic Gettering の略。例えばウェハ裏面の薄厚加工時に残留するひずみ層は、上記同様ウェハ裏面からの不純物を捕らえる効果を持ち、表層のデバイス形成領域への不純物の拡散を防ぐ。    |

| EM             | Electro Migration: 金属に電流を流した際、原子が移動する現象。                                                             |

| FEM            | Finite Element Method: 有限要素法。                                                                        |

| H-WSS          | Hard Wafer Support System の略。従来のテープ保持方式に対比して、ガラス保持方式を示し、薄くてたわみやすい厚さのウェハ加工では必須となる。                    |

| IG             | Intrinsic Gettering の略。結晶内部の残留ひずみ層は、結晶裏面からの不純物を捕らえる効果を持ち、表層のデバイス形成領域への不純物の拡散を防ぐ。                     |

| IPG            | In Process Gauge の略。接触式の厚さ測定システムの意味。                                                                 |

| KGD            | [英]Known Good Die の略。テストやバーンインなどの信頼性工程を経て、良品の半導体チップであることが確認され、品質保証されたベアチップ(ウェハから切り出された状態の半導体チップ)をいう。 |

| NCG            | Non-Contact Gauge の略。非触式の厚さ測定システムの意味。                                                                |

| SEM            | Scanning electron microscope の略。走査型電子顕微鏡と呼ばれ、試料表面の形状観察に用いられる。                                        |

| TC             | Thermal Cycle: 披検物に温度変化のサイクルストレスを与え、環境加速耐久<br>試験を行う方法。                                               |

| TEG            | Test element groupの略。機能や性能検証を目的とした一連のテストパターン。                                                        |

| THB            | Temperature Humidity Bias:披検物を恒温恒湿で劣化加速試験を行う手法。                                                      |

| TIM            | Thermal Interface Material: 二つの物質間(たとえばシリコンチップと放熱器) に適用し、熱的に接続させる(熱伝導させる)ための材料。                      |

| TSV            | TSV(Through silicon via)とも略す。シリコン基板に貫通電極を埋め込み、基板の表面と裏面をつなぐ配線として利用。                                   |

| TTV          | Total Thickness Variation の略。            |

|--------------|------------------------------------------|

|              | ウェハ上にある半導体チップの電極に対して、プローブと呼ばれる針やバンプ      |

| アライメント       | (金属の突起)をあてる時の位置合わせ、あるいはその操作をいう。          |

|              | [英]alignment                             |

| ,            | 半導体チップを製造する材料。半導体素材のシリコンなどで作られた円柱状の      |

| ウェハ          | 塊を薄くスライスした円盤状の基板。[英]wafer                |

| 3 3          | ウェハ上に形成された半導体チップに対して、電気的検査を実施し、良品と不      |

| ウェハテスト       | 良品を識別するテスト。[英]wafer test                 |

| ウェハトレー       | ウェハを載せる浅い金属容器。 [英]wafer tray             |

| 温調           | 温度調節の略。                                  |

| F 11. V++ ±+ | 蒸発に伴う蒸発熱(気化熱)をいう。 物質が液体から気体に変化するときに起     |

| 気化潜熱         | こる吸熱現象。                                  |

| 高熱伝導材        | 一般に銅・銀といった金属材料よりも熱を伝えやすい性質を持つ材料。         |

| ーシャカ         | ケーブルを用いて電子機器どうしを接続するための電気部品で、特に複数の       |

| コネクタ         | 配線を同時に接続するものを指す。 [英]connector            |

| 古亦独关厂士士      | メンブレン方式プローブカードにおいて、微かな真空の圧力差を利用してプロ      |

| 真空微差圧方式      | ーブ電極を加圧する方式。                             |

|              | 固体どうしの接触面が完全に密着しないことによって生じる熱の伝わりにくさを     |

| 接触熱抵抗        | 表す値。鏡面処理された滑らかな固体面でも現実には凸凹な構造があるため       |

|              | に完全に密着しない。単位:℃/W                         |

| 大気圧加圧        | 大気の圧力を利用してウェハ全体に均一な荷重を加えること。             |

| チャックテーブル     | ウェハ研磨装置などで、ウェハを真空吸着して保持するステージ。           |

| テスタチップ       | テスト機能回路を搭載した半導体チップ。                      |

|              | 半導体製造工程において製造欠陥が原因で不具合(故障)を起こしている半       |

| テスト          | 導体チップを良品と不良品に選別する作業。テストは出荷される半導体が正し      |

| 7 211        | く動作することを保証するための重要な工程。試験、検査とも呼ばれる。        |

|              | [英]test                                  |

| テストコスト       | 半導体チップの製造コストの中に占めるテストに必要なコストをいう。 [英]test |

| 7 2 4 2 4    | cost                                     |

|              | テストを行う装置。テスタと呼ばれる。テスト対象となる半導体チップ設計時に作    |

| テストシステム      | 成したテストパターンを元に半導体チップへ入力し、半導体チップからの出力      |

|              | 信号を期待値と比較する。[英]test system               |

| テスト速度        | テストを行う際、テスト対象となる半導体チップの動作速度条件。           |

| 伝送速度         | 一定時間内に送ることができるディジタル信号量をいう。1秒間に送ることがで     |

|              | きるディジタル信号量を bps(bit per second)という単位で表す。 |

| バーンイン        | 半導体チップの初期不良を除去する選別手法の一つ。高温や高電圧を印加        |

| - 14         | し、半導体チップを動作させた状態で良品と不良品をふるい分ける。 [英]      |

|             | burn-in                                             |

|-------------|-----------------------------------------------------|

| 2° ( - 2° ) | 半導体製品の外形を構成する部分。半導体チップを包む樹脂や金属、セラミッ                 |

| パッケージ       | クを指す。[英]package                                     |

| バンプ         | チップ上の金属突起状端子。                                       |

| Ala         | パッケージされた半導体チップに対して、電気的検査を実施し、良品と不良品                 |

| ファイナルテスト    | を識別する最終工程のテスト。[英]final test                         |

| IF ETTO     | 一般に 1 ウェハ当たりのチップ収量数に対しウェハテストで残った良品数の比               |

| 歩留り         | 率を表す。イールドとも呼ばれる。[英]yield                            |

|             | 基板にチップを実装し電気的に接続する際, アレイ状に並んだバンプと呼ばれ                |

| フリップチップ     | る突起状の端子によって接続する方法。                                  |

|             | ウェハ上にある半導体チップの電極に対して、プローブと呼ばれる針やバンプ                 |

| プローブカード     | (金属の突起)をあて、テストシステムによる電気的検査を可能にするための冶                |

|             | 具。[英]probe card                                     |

| プローブチップ     | 非接触通信用の信号送受信回路を搭載した半導体チップ。                          |

| メンブレン方式プロ   | メンブレン、[英]membrane は薄い膜という意味。プローブ用の電極を耐熱性の           |

| ーブカード       | 樹脂シート上に配列したプローブカード。                                 |

|             | 2枚の金属板(電極)を近接させたときに生じる微小な静電容量を利用した結                 |

| 容量結合        | 合。                                                  |

|             | B はバイトで 8 ビットを1単位としたデータ量を示す。100GB/sec とは1秒間に        |

|             | 1x109 バイト(8x109 ビット)の転送能力を示す。こうしたデータの転送能力を「バ        |

| 100GB/sec   | ンド幅 Bandwidth」と呼ぶこともある。又「1秒あたり」を示す「/sec」を略して ps と   |

|             | して 100Gbps(ひゃくぎがびーぴーえす)と呼んだり記載したりすることが一般化           |

|             | している。                                               |

| 2k-IO       | データの入出力端子が 2,048 本あることを示す。                          |

| BCB(ベンゾシクロブ | - 11 11 11 11 11 11 11 11 11 11 11 11 11            |

| テン)         | ウェハ間封止樹脂の候補として検討中。                                  |

| C2C         | Chip to chip:チップ積層。                                 |

|             | Correlated Double Sampling(相間二重サンプリング)の略であり、ノイズキラーの |

|             | 働きをする方式である。CMOS 画像センサのフォトダイオードの光励起電荷を               |

| CDC         | 容量に取り込む際のスイッチオンでリセットノイズが乗る。短時間にもう一度取り               |

| CDS         | 込みを繰り返すと、二度目はリセットノイズが乗らないことから、この差をキャンセ              |

|             | ルして信号としてカウントする方式である。短時間二重サンプリングのため、アン               |

|             | プの 1/f ノイズも低減される。                                   |

|             | Chemical Vapor Deposition:絶縁膜等を化学的に気相成長させる方法。特にプ    |

| CVD 法       | ラズマを使った CVD 法は低温で成膜できるため、TSV の絶縁膜形成に使われ             |

|             | る。                                                  |

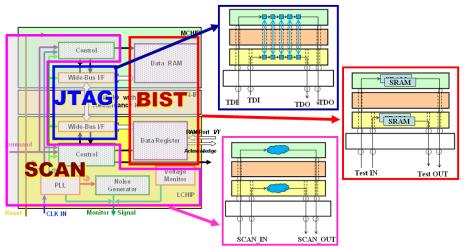

| DFT         | Design For Test の略号で試験性を考慮した設計手法のこと。                |

|                    | Video Graphic Array の略号で、1987 年、IBM は開発した画像表示仕様である。 デジタル画像は画素子から構成され、VGA は横 640 ドット、縦 480 ドットの画素子から構成されている 16 色のカラー画像表示仕様である。 発表当時は高 |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| VGA, QVGA          | 国系子がら構成されている 16 色のカノー画像表示任像である。 発表当時は同<br>精細であったが、現在はHDTV (High Definition TV)として高精細画像 (1920×                                        |

| VGA, QVGA          |                                                                                                                                      |

|                    | 1080)が一般化されている。QVGA (Quarter VGA)は VGA の 1/4 の画素子                                                                                    |

|                    | (320×240)を表現することが一般であるが、Quad VGA として 4 倍のが素子を                                                                                        |

| 77. EV. 4          | 表現することもある。ここでは 1/4 を表現している。                                                                                                          |

| Via First          | デバイスを形成する前に TSV を形成する方法。                                                                                                             |

| Via Last/Back Via  | デバイスを形成した後、ウェハ裏面から TSV を形成する方法。                                                                                                      |

| Via Last/Front Via | デバイスを形成した後、ウェハ表面から TSV を形成する方法。                                                                                                      |

| Via Middle         | トランジスタを形成した後に TSV を形成する方法。                                                                                                           |

| W2W                | Wafer to wafer:ウェハ積層。                                                                                                                |

| <br>  後樹脂法         | W2W あるいは C2C で、ウェハ間 (チップ間)を封止する樹脂を積層後に形成す                                                                                            |

| 区国加口               | る方法。                                                                                                                                 |

|                    | 一般にシステムの入出力をつかさどる回路で構成されたチップであるが、この                                                                                                  |

|                    | 場合は高速デジタル画像データが並列に I/F に落とし込まれるため、これを出                                                                                               |

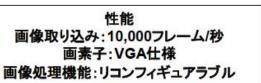

| インターフェースチ          | 来るだけ少ない本数にまとめて出力するパラレル/シリアル変換回路とデータの                                                                                                 |

|                    | タイミングを制御する回路、タイミングを制御するためのデータの高速一次保存                                                                                                 |

| ップ (I/F)           | 回路(高速ラッチ)、十分な駆動能力を持つ高速出力ドライバ回路、電源制御                                                                                                  |

|                    | 回路などが含まれている。ここではVGA仕様、10,000fpsの信号24Gbpsを十分                                                                                          |

|                    | 処理できる高速大容量設計となっている。                                                                                                                  |

|                    | ピクセルからの増幅データはアナログ信号であるため、これをデジタル信号に                                                                                                  |

|                    | 変える回路である。通常は8ビットのデジタル信号にするが、ここでも同じ8ビッ                                                                                                |

|                    | トとした。デジタルに区切るため、抵抗ラダーか容量ラダーかの方式があるが、                                                                                                 |

|                    | いずれにしても面積を取ることと、消費電力が大きくなる回路であり、高速化で                                                                                                 |

| AD コンバータ           | ますますこの傾向が増長される。3D 積層ではピクセル面積以内に押さえること                                                                                                |

| (ADC)              | が必要となり、10,000fpsを実現するためのキー技術であったが、画像 10×10 ピ                                                                                         |

|                    | <br>  クセルを一つの単位として AD 変換する回路方式にすること、ハイブリッドラダー                                                                                        |

|                    | │<br>│ 方式にすることなど、多くの工夫で解決できる見通して、世界最高レベルの技                                                                                           |

|                    | 術となった。                                                                                                                               |

| エポキシ               | ウェハ間封止樹脂の候補として検討中。                                                                                                                   |

|                    | Concurrent Design はシステム全体を同時に設計する手法を呼ぶ。複数の異種                                                                                         |

|                    | 構成要素がお互いに関連することから、個別設計で最適にしても構成要素間                                                                                                   |

|                    | で整合しない問題が生じる。特に異種回路の複数チップを積層して一つのモ                                                                                                   |

| コンカーレント設計          | ジュールとして機能を出すためには、接続の並列度(どのような信号関係にす                                                                                                  |

|                    | るのか)や接続電極の整合性はもちろんのこと、動作タイミングの整合、電力配                                                                                                 |

|                    | 分構成、放熱の配慮、機械的応力などのお互いに関連しあう項目を調整する                                                                                                   |

|                    | // 四//ヘ、//ヘハ៶シン口心心、//メア/メトエノ/レ゚ノプポにソルロ・パーに対定しはノアスロで明定する                                                                              |

| 先樹脂法成して          | あるいは C2C で、ウェハ間 (チップ間)を封止する樹脂を積層前に予め形                             |

|------------------|-------------------------------------------------------------------|

| 先樹脂法成して          | あるいけ C2C で ウェハ間(チップ間)を封止する樹脂を積属前に予め形                              |

| 成して              | かり 18 010 C() 二 同() 2 回 2 回 1 0 回 1 0 回 1 0 回 1 0 1 0 1 0 1 0 1 0 |

| 225              | おく方法。                                                             |

| CCD              | 画像センサに対して CMOS プロセスで出来る安価なセンサとしてデビュー                              |

| したもの             | ので、感度が低く、フォトダイオードあたりのアンプ(増幅器)を付けている                               |

| が、これ             | れに伴う多くの欠点があった。しかし、CMOS プロセスであることの利点                               |

| (小面和             | 責で回路が作れる)を利用して、その欠点をカバーする補助回路を設けて                                 |

| CMOS 画像センサ 性能向   | ]上が図られ、もともとの特徴、低消費電力、小面積ピクセル、単一電源、                                |

| 高速動              | h作などの利点を生かして、現在では主流の画像センサとなっている。本                                 |

| 研究で              | は 10,000fps のための増感が必要なため、10×10μmピクセルと比較的                          |

| 大きい              | サイズを考えている。                                                        |

| 超ワイドバスメモリと       | ロジックをつなぐデータ線の本数が 2,048 本以上であること。                                  |

| 多数の              | ピンで素子を相互接続した際に、接続の完全性を確認するテスト機能の                                  |

| <b>一つ。</b>       | 入出力端子に接続する回路にレジスタを追加し、これらを直列に接続                                   |

| バウンダリスキャン (カスケ   | アード接続) することで内部回路を経由せずに端子の接続性を確認する                                 |

| 試験機              | 能能。                                                               |

| デジタ              | ル信号は0か1かで表現される2進数で、この一つの0か1の表現をビ                                  |

| ットと阿             | んでいる。1秒間に何ビットのデジタル信号が伝送できたとか処理できた                                 |

| とかの              | データ速度としての表現である。Mbps(百万ビット/秒)、Gbps(10 億ビット                         |

| ビット/秒(bps) /秒)と  | いった単位がよく用いられている。最近は高速信号伝送とか処理の速度                                  |

| は100             | Gbps レベルである。ここでは VGA 仕様のセンサから来る画像アナログ信                            |

| 号を 8             | ビットのデジタル信号に変換するため、10,000fps のデータ量は 24Gbps                         |

| となる。             |                                                                   |

| パネル              | に表示される画像の単位をフレームと呼び、1秒間に何フレームで構成                                  |

| フレーム/秒(fps) される  | かの性能表示である。フィルム映画は32fps、TVは30fps、高速度カメラの                           |

| 最先端              | は 2,000fps である。ここでの目標は 10,000fps と設定している。                         |

| 上記り              | コンフィギュアラブルメモリの方式に整合する超並列プロセッサであり、初                                |

| 期的な              | :区分間をまたがって画面中を移動するオブジェクトを対象に画像処理す                                 |

| 並列プロセッサる場合       | などメモリの区分間自由度に対応して並列区分間をダイナミックに移動                                  |

| しなが              | ら処理できる方式を検討している。                                                  |

| TSV 0            | )Si エッチングで、深い Via を垂直に加工するためのドライエッチング方                            |

| ボッシュ(Bosch)法 法。エ | ッチングとデポジションを交互に繰り返して加工する。ため、垂直形状は                                 |

| 得られ              | るが、スキャロップと呼ばれる Via 側壁の荒れが発生する。                                    |

| 半導体              | xの保護膜として使われているが、ウェハ間封止樹脂の候補として検討                                  |

| ポリイミド中。          |                                                                   |

| 有機インターポーザ 一般に    | LSI パッケージという意味合いが強いものであるが、ここでは Si インター                            |

|            | ポーザを含む積層チップモジュールを受ける多層配線板である。高速信号と高                      |

|------------|----------------------------------------------------------|

|            | 速応答電源配線が含まれるため、十分な設計的工夫がなされている。                          |

|            | リコンフィギュアラブルメモリの意味はメモリのアドレス構造をニーズに合わせて                    |

|            | 自由に変更できるということである。上記、VGA 仕様 10,000fps の画像のキャッ             |

| リコンフィギュアラブ | シュメモリとして利用するもので、3Dとして並列度の大きい画像データを並列度                    |

| ルメモリ       | に区分されたマットに記憶するが、画像処理のためマット間にまたがるデータを                     |

|            | 利用したいとき、区分制限によるデータの遅れが出ることを避けるため、その区                     |

|            | 分をダイナミックに変更できる方式を持ったキャッシュメモリを考え検討してい                     |

|            | る。                                                       |

| LIDT       | Heterojunction Bipolar Transistor の略称。ヘテロ接合(異種の半導体接合)を   |

| HBT        | 利用したバイポーラ・トランジスタの素子構造の一つ。                                |

|            | Micro Electro Mechanical System の略称。機械要素部品、センサー、アクチュ     |

| MEMS       | エータ、電子回路を一つのシリコン基板、ガラス基板、有機材料などの上に集                      |

|            | 積化したデバイス。                                                |

|            | pseudo High Electron Mobility Transistor の略称。異なった化合物半導体を |

| pHEMT      | ヘテロ(異種金属)接合させ、高速化を図ったトランジスターの一つ。                         |

| RF         | Radio Frequency の略称。無線周波数。高周波。                           |

| インピーダンス    | 交流回路に電圧を加えたときの電流の流れにくさを示す量。                              |

|            | 3rd Generation の略称。第3世代の携帯電話方式の総称。基本的にCDMA               |

| 3G         | 方式を採用し(一部は改良型の TDMA 方式を利用)、高速なデータ通信やマル                   |

|            | チメディアを利用した各種のサービスなどが提供されている。                             |

|            | Asymmetric Digital Subscriber Line の略称。電話線を使い高速なデータ通信    |

|            | を行なう技術。電話の音声を伝えるのには使わない高い周波数帯を使って通                       |

| ADSL       | 信を行なう技術で、一般の加入電話に使われている一対の電話線を使って通                       |

|            | 信する。                                                     |

|            | Code Division Multiple Access の略称。携帯電話などの無線通信に使われる       |

|            | 方式の一つ。「符号分割多重接続」とも訳される。複数の発信者の音声信号に                      |

| CDMA       | それぞれ異なる符号を乗算し、すべての音声信号を合成して 1 つの周波数を                     |

|            | 使って送る。受け手は自分と会話している相手の符号を合成信号に乗算する                       |

|            | ことにより、相手の音声信号のみを取り出すことができる。                              |

| EVM        | Error Vector Magnitude の略称。デジタル変調信号の品質尺度。                |

|            | High Speed Downlink Packet Access の略称。NTTドコモなどが採用している第   |

| HSDPA      | 3 世代(3G)携帯電話方式「W-CDMA」のデータ通信を高速化した規格。3G 方                |

|            | 式の改良版であることから「3.5G」とも呼ばれ、従来の5倍以上の通信速度を実                   |

|            | 現する。                                                     |

|            | Noise Figure の略称。入力側の S/N に対して、出力側の S/N がどれだけ劣化          |

| NF         | するかを示す。                                                  |

|            |                                                          |

| S/N                     | 信号量 (signal) と雑音量 (noise) の比。                                  |

|-------------------------|----------------------------------------------------------------|

|                         | 携帯電話の高速なデータ通信仕様の一つで、NTT ドコモやソフトバンクモバイ                          |

|                         | ルなどが採用している「W-CDMA」の高速データ通信規格「HSDPA」をさらに                        |

| S3G                     | 進化させたもの。下り100Mbps 以上/上り50Mbps 以上の高速通信の実現を目                     |

|                         | 指したもので「LTE」Long Term Evolution とも呼ばれる。                         |

|                         | Wideband Code Division Multiple Access の略称。NTTドコモや Ericsson 社な |

|                         | どが開発した第 3 世代携帯電話(3G)の通信方式。高速移動時 144kbps、歩行                     |

| W-CDMA                  | 時 384kbps、静止時 2Mbps のデータ伝送能力があり、動画・音声によるリアルタ                   |

|                         | イムの通信が可能。                                                      |

|                         | Worldwide Interoperability for Microwave Access の略称。無線通信技術の規   |

| WiMAX                   | 格の一つであり、モバイル・パソコンなどのモバイル端末が ADSL 並みの速度と                        |

|                         | 料金でデータ通信できる技術として注目されている。                                       |

| 物理インターフェー               | ソフトウェアドライバとコネクタから成り、コネクタには、USB ケーブルなどのネット                      |

| ス                       | ワークメディアを接続する。                                                  |

| ベースバンド回路                | 変復調をする通信システムでは、変調前の信号および復調後の信号をベース                             |

| ・・・ハハント回路               | バンド信号と言い、ベースバンド信号を扱う回路をベースバンド回路と言う。                            |

| CMP                     | Chemical mechanical polishing の略。半導体プロセスで一般的に使用されてい            |

| Civii                   | る平坦化プロセスの名称。                                                   |

| CMOS                    | Complementary Metal Oxide Semiconductorの略称。狭義には MOSFET を相      |

| CWOO                    | 補形に配置したゲート構造のこと。                                               |

|                         | Field Programmable Gate Array の略称。利用者が独自の論理回路を書き込む             |

| FPGA                    | ことの出来るゲートアレイの一種。 多数の LUT とスイッチ搭載し、これを組み合                       |

|                         | わせて回路を構成する。                                                    |

| LUT                     | Look Up Tableの略称。入力ビット列をインデックスとして、出力すべき真理値を                    |

|                         | 格納したメモリ。任意の真理値表に対応する組み合わせ回路を実現できる。                             |

| SoC                     | System on Chip の略称。一つの IC チップに複数の回路機能が集積されてシス                  |

|                         | テムの機能を持つ半導体製品。                                                 |

| クロック                    | デジタル回路が動作する時に、複数の電子回路のタイミングを取る(同期を取                            |

|                         | る)ために使用される周期的な信号。                                              |

| 伝送スループット                | 単位時間あたりに送信されるデータのビット数。                                         |

|                         | バス方式では積層されたすべての TSV が 1 本の導体として共有されており、か                       |

| バス方式(TSV を使<br>った三次元通信) | つ各チップの送信バッファと受信バッファがこの TSV に接続されている。あるチ                        |

|                         | ップから信号を伝送する場合、該当するチップの送信バッファが全積層チップ                            |

|                         | の TSV を駆動する。その送信バッファからみた TSV 浮遊容量は積層チップ数                       |

|                         | に依存する。このため、負荷容量の増大に対する伝送レートへの影響は大き                             |

|                         | く、その反面1本の貫通導体を共有するため各チップ間の遅延時間には大きく                            |

|                         | は影響しない。                                                        |

| プロセッサ                    | プロセッサ (processor) は、コンピュータの中で、組込みソフトウェアを動作さ |

|--------------------------|---------------------------------------------|

|                          | せるためのハードウェアであり、演算器、周辺回路、命令や情報を格納するメ         |

|                          | モリから構成される。                                  |

| リコンフィギャラブル               | 再構成可能なプロセッサ。細粒度から粗粒度まで様々な粒度の再構成があ           |

| プロセッサ                    | る。                                          |

| リピータ方式(TSVを<br>使った三次元通信) | TSVとPAD 部を分離し、TSVとPADの間にリピータ回路(実際はバッファ)を挿   |

|                          | 入する。TSV は各チップ層で分離される。各チップの送信バッファは隣接する       |

|                          | チップへのみ信号を伝送し、その先のチップへはリピータ回路が送信する。送         |

|                          | 信バッファから見た TSV 浮遊容量は積層チップ数に依存せず常に 1 層チップ     |

|                          | 分となる。このため、負荷容量の増大に対する伝送レートへの影響は小さく、そ        |

|                          | の反面リピータ回路を介するため積層チップ数が増えるとチップ間の遅延時間         |

|                          | が増大する。                                      |

### I. 事業の位置付け・必要性について

## 1. NEDOの関与の必要性・制度への適合性

#### 1.1 NEDOが関与することの意義

我が国半導体技術の発展は、情報家電、コンピュータ、通信装置を始め、自動車、医療機器など様々な機器の高性能化、小型化、省電力化に貢献し、情報通信産業やその他の製造業など我が国経済を牽引する産業の競争力を強化するものである。従来、この発展を支える半導体デバイスの製造技術は、CMOS-LSI用プロセス技術を二次元的に微細化することにより追求されてきた。その一方、微細化進展により、その素子加工サイズが原子スケールに近付きつつある現状では、微細トランジスタのリーク電流や配線容量の増大にともなう消費電力の増大、微細化プロセスを開発するための研究開発投資、さらには製造設備投資の増大に代表される種々の課題が顕在化しつつある。

これら課題に対して、低リーク電流を実現するトランジスタ構造の研究開発や、低誘電率の配線層間絶縁材料等の微細化推進を可能とするための技術開発が行われ、その成果は着実に実用化されてきている。その一方で、現状技術のトランジスタ、配線材料等を用いつつ、Si 貫通ビアを活用した半導体デバイスの三次元集積化技術(立体構造化、あるいは積層化)を行うことによっても上記課題を克服することが可能である。また、この技術を他の技術分野との融合に利用し、CMOS 半導体デバイスとCMOS 以外のデバイスとの三次元集積化を行えば、従来 CMOS 半導体デバイスでは実現が難しかった多機能デバイスの実現が可能となり、従来にない革新的な性能を持つ種々のデバイス創出に波及する可能性を持つ。

このように、三次元集積化技術の構築によって、革新的な性能を期待できるデバイスを提供できる可能性が高い。このことから、平成20年に策定された経済産業省「ITイノベーションプログラム」の中で、あらゆる社会ニーズに情報技術が今後も迅速に対応し、夢の社会を創り上げるため、新しい方向の半導体技術として、立体構造という新たな概念を取り込み、多様な用途に応じた夢の新機能デバイス(ドリーム・チップ)を開発する、NEDO交付金の運用による実施が計画された。

NEDOは、その計画を受け、同プログラムの中で実施する他の半導体技術開発プロジェクトと 同様に、基本計画を策定し、それに基づいて実施者を公募し、研究開発を推進することとした。 本技術開発の意義は以下となる。

第1に、Si 貫通ビアを活用した半導体デバイスの三次元集積化技術(立体構造化、あるいは積層化)は、半導体分野においては、二次元的な微細化技術と共に半導体デバイスの更なる高性能化を実現するものである。さらに、半導体デバイス分野に限らず、他の技術分野とも融合する領域においても、革新的技術あるいは革新的機能デバイスを生み出しうるものである。

第2に、三次元集積化構造とすることにより、配線長の短縮が期待でき、寄生容量に起因する 消費電力増大を低減できる。すなわち低消費電力化を実現する有力な技術であり、情報通信分 野への応用を考えると、機器の小型、低消費電力化、さらにそれらによる普及促進という効果が 期待される。

本技術開発に対して、NEDOが関与することの意義をまとめると以下となる。

第1に、本プロジェクトの研究開発は、その成果によりわが国半導体産業の成長という大きな効

果が見込める一方で、多額の資金投入を要し、個別の企業ですべてをまかなうことに困難がある。

第2に、三次元集積化技術で積層されるデバイスを実現するには、川上から川下まで、すなわち設計ツール開発・材料開発・製造技術・検査技術・分析機器開発・応用製品開発等、様々な技術分野で開発されたものが必要となる。産業界における製品開発の効率性をあげるためには、それらデバイス間の接続方法等が事実上業界で標準化されることが望ましく、単独の企業主導で推進するよりも、NEDO主導のもと前記したような各種技術分野の有力企業の英知を結集して実施することで、その目的を達成しやすいものとすることが可能である。また、世界に先駆けて業界標準となる技術を開発できれば、広く日本の産業技術の競争力を高めることに繋がるものである。

また有力各企業の英知を結集して密接な情報交流の場を提供し、その連携を推進することも有益と予想でき、それにより、容易に想到できない製品形態への展開が触発される期待も持ち得る。

またさらに、各国が三次元集積化回路開発に関してわが国を猛追する中、本プロジェクトが仮に実施されなかったものと仮定すると、各企業における研究開発レベルの維持が困難となり、三次元集積回路へのマーケットニーズが顕在化した暁に、速やかにニーズに応えることが出来ず、わが国の半導体産業が事業機会を逸する可能性が高い。これは、きわめて危険が大きいと言える。

上記により、本技術開発はNEDOが関与すべきものであり、また政策のひとつである「ITイノベーションプログラム」において実施すべき内容である。

#### 1.2 実施の効果(費用対効果)

### (1) 新市場創出効果

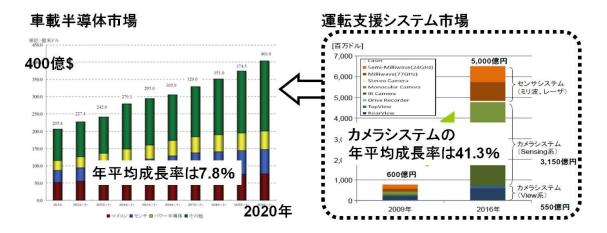

本事業の三次元積層技術の適用分野は、主に小型化、省電力を活かすモバイル製品と WideI/O などの高速伝送を必要とする IT 機器の2つの分野が牽引すると考えられる。また、半導体製品の品種別では DRAM, WideI/O メモリ、アプリケーションプロセッサ等の SoC、MEMS/センサ、パワーデバイス、カスタム LSI などが主要製品である。

調査会社の Yole Development が2012年7月に報告した半導体市場予測によると、平成29年(2017年)における三次元積層技術を使用した半導体市場は全世界で約4兆円である。このうち、本事業が取り組んだ、WideI/O、DRAM、MEMS, SoCなどが占める割合は約8割であり、3.2兆円のTAM (Total Available Market:有効市場)が見込まれる。今のところ顕在化していないが、センサの搭載数が増加する車載電装分野、医療分野は、小型、低消費電力への要求が強く三次元積層の波及分野として期待される。

本事業の事業規模を表1に示す。平成20年度から平成24年度までの5年間の執行額は合算で73億5千万円となった。しかしながら、前記した大きな市場インパクトとわが国の基幹産業である半導体産業の競争力維持強化の目的には妥当な規模であると考える。

表1 本「ドリームチップ」プロジェクトの事業規模年度推移

| H20 年度 | H21 年度 | H22 年度 | H23 年度 | H24 年度 | 合計    |

|--------|--------|--------|--------|--------|-------|

| 1,086  | 2,228  | 1,615  | 1,153  | 1,271  | 7,353 |

単位:百万円

## 2. 事業の背景・目的・位置づけ

#### 2.1 事業の背景

#### (1) 産業的基盤

先に、我が国半導体技術の発展を支える半導体デバイスの製造技術として、CMOS-LSI用プロセス技術を二次元的に微細化する技術開発が進められてきたものの、その進化に伴い、種々の課題が顕在化してきたことを述べた。また本研究開発における三次元集積化技術はその解決策の位置付けにあるとした。ここでは、より詳細に二次元的な微細化技術で顕在化してきた課題を列記し、それに対する三次元集積化技術の利点を示す。

二次元的な微細化技術の課題は以下にまとめられる。

- ・ 配線容量の増大と信号クロック周波数の高周波化による消費電力の増加

- ・ 配線抵抗と、配線容量の増大による信号伝搬遅延増大

- ・ 微細トランジスタのリーク電流増加による消費電力増加

- 製造レベルでのばらつき制御や歩留まり対策の高度化

- ・ 特性ばらつき増大による設計困難度の増加と設計期間の長期化

- ・ 微細化を実現するための研究開発投資、設備投資の増大

三次元集積化の利点の一つは、チップを積層することにより、二次元的構成において平面的に配置していた配線を、対抗するチップ間の配線に置き換えることができ、その距離を短縮できる点である。またそのチップ間の配線本数は、二次元的配置に比べ桁違いに多く設計することが可能になる点である。これにより、配線容量を低減できると共に、同容量の信号伝送量を確保するために必要な信号クロック数を低減することが可能となり、消費電力の増加を抑えられる。また、配線容量の低減は信号伝搬遅延の増大を低減し、これにより特に信号伝搬遅延を補償するために求められた、トランジスタ高速性に対する要求が低減される。すなわちリーク電流が大きな高速トランジスタを使用しなくてはならない条件が緩和され、回路全体としては低消費電力化に繋がる。さらにトランジスタ特性に対する要求が緩められると、その製造段階の特性ばらつき低減や歩留まりに向上につながり、設計困難度を緩和することになる。

また別の観点から、三次元集積化技術は、既存の開発済みのチップ、あるいはデバイスを組み合わせる事が可能な技術であり、既に確立された設計資産を有効活用することができる。これにより、新たなプロセス開発の研究開発投資や、設備投資を低減することができ、産業の開発効率を改善する直接的な効果を生む技術である。また設計資産を有効に活用することで、製品設計期間の短縮も期待される効果である。

# (2) 技術的基盤

前述のように、三次元集積化技術は半導体素子の高性能化に効果があり、海外各国においてもその開発が強化されている。

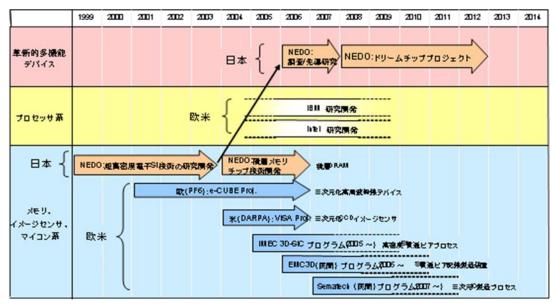

NEDOは、世界に先駆けて高密度三次元積層技術(超高密度電子 SI 技術プロジェクト(平成 11~15 年度)におけるポリSi 貫通ビアによる三次元チップ積層技術開発、積層メモリチップ技術開発(平成 16~18 年度)における積層 DRAM 技術開発)の成果があり、研究開発実績としては今のところ我が国に優位性がある。最近、わが国を急追する各国の動きは前述のNEDOプロジェクト成果を考慮したものである可能性がある。これらの状況を時間軸にまとめたものが図 1 である。

各国の開発活動の活発化に照らして、今後、三次元集積化技術を軸とした開発競争は熾烈化するものと考えられ、この状況を放置すれば三次元化に関する技術開発の競争力を失いかねない。このことから、三次元集積化技術を軸とした立体半導体開発分野での産業競争力を維持し、さらに他に先駆けて革新的機能デバイスを生み出す技術開発を行う必要性が理解される。

また、2005年以降、TSMC、GF、Intel、AMKOR、サムソンなどの事業会社の取組みも 強化されているとの報道があり事業化・実用化が加速されている。

(図1 三次元集積化技術に関する研究開発プログラム)

#### 2.2 事業の目的

NEDOで実施してきた過去の技術開発プロジェクトにおいて、ポリ Si 貫通ビア技術や、それを用いた半導体メモリ積層の大容量化(同種チップの多層化)技術を確立した。それら技術は主として製造技術に関わるものであり、その成果の展開は既に各企業の競争領域となりつつある。本技術開発ではそれら技術の先進度および完成度をさらに高め、半導体素子と他の機能デバイスとの三次元集積化が可能な技術へと高めることを主たる目的とする。

三次元集積化技術を広く展開する上で課題となるのは、今までにない三次元構造という状態

での回路解析・設計技術、さらに回路設計を最適化する技術である。また三次元的構造の内部で発生する熱を効率よく伝達、放熱する技術も重要である。さらに三次元積層時の製造歩留まりに直結する、各チップの機能検査を効率よく行う検査技術も必要である。これらのことから、研究開発項目の一つとして、立体構造(三次元集積化構造)における回路設計技術、熱設計技術などの設計技術、チップテスト、欠陥評価など評価技術を中心とした三次元集積化技術の開発を目的とする。また立体構造を適用したデバイスの効果を実際に示すためのデバイス開発として、MEMS デバイスと CMOS 回路との三次元集積化を含む周波数特性可変の高周波デバイス、それらを用いた複数周波数対応通信システム開発の実証を目的とする。さらに先進的な取り組みとして、三次元集積化構造を活かし、画期的な性能向上を実現する回路再構成可能デバイスの開発も目的とする。

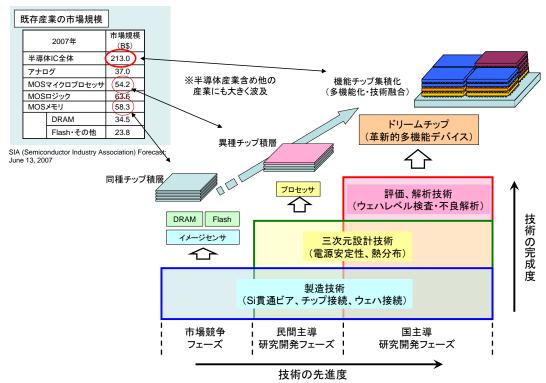

図2に三次元集積化における技術の先進化、完成度の向上の概念を示す。なお、立体構造による MEMS デバイス及び回路再構成可能デバイスは、図において完成度を高めた技術により実現されるデバイス応用の一つとして位置づけられるものである。

(図2 多機能高密度三次元集積化技術の目的と既存市場での応用分野)

#### 2.3 事業の必要性と意義

我が国が他に先駆けて取り組んだ、三次元集積化技術の完成度を高め、立体構造という新しい概念のデバイス設計、解析技術を開発することで、半導体デバイスとの集積化が困難であったデバイスと、半導体デバイスとの集積化が可能となる。これにより、例えば中期的には複数周波数対応通信三次元デバイスや三次元回路再構成可能デバイス等に代表される小型、高機能デバ

イスが開発され、IT 社会における様々な情報通信機器の小型化、高機能化に寄与する。また長期的には、様々な技術の融合による新たな機能デバイスを創出する環境が構築され、新規事業分野を継続的に展開し続けうる、持続的技術革新が可能な社会環境が整う。これにより、この技術に関する優位性を維持しつつ、革新的デバイスを創出することで、産業競争力の向上に寄与するものである。

## 2.4 事業の指針

本研究開発は、これまでの同一機能のメモリの積層による高集積化とは異なり、異機能を持つチップの積層技術、デジタル・アナログ回路や微小可動機構の積層技術、さらには三次元的に積層したチップに対し後からプログラムを書き換えて機能を発揮させる技術など、これまでにない三次元化技術により、新たな機能の発揮と飛躍的な性能向上を実現する立体構造新機能集積回路技術を確立することを目的とする。具体的には以下の3つの研究開発項目を行う。

# ①多機能高密度三次元集積化技術

半導体デバイスである各種メモリ、ロジック回路などと、半導体以外のデバイスとを立体的に 集積化する際に必要な設計、評価技術を開発する。これにより引き続きシリコン半導体デバイス の高性能化を推進すると共に、半導体デバイスと異なる技術分野のデバイスを集積化する手段 を確立し、革新的なデバイス創出可能な開発環境の構築を目指す。

## ②複数周波数対応通信三次元デバイス技術

シリコン半導体デバイスと、微小可動構造(MEMS)による通信デバイスを三次元集積化し、 放送、携帯電話、無線 LAN などの複数の電波帯域で利用可能な通信デバイスを開発する。これにより、多くの周波数帯に対応した、いつでもどこでもつながる通信端末を実現する。

# ③三次元回路再構成可能デバイス技術

リコンフィギャラブル半導体(※)が本質的に抱える問題点(動作速度、チップサイズ、消費電力など)を、立体構造を導入することで大幅に改善する技術開発を行う。これにより従来のリコンフィギャラブル半導体では対応できなかった分野(モバイル製品等)においても、不具合や故障などの修復に柔軟に対応できるという利点を持った小型、低消費電力のリコンフィギャラブル半導体を実現する。これにより高度な情報通信機器の高信頼化に資することになる。

(※)リコンフィギュアラブル半導体(プログラム可能論理素子):製造した後にソフトウェアプログラムで機能を複数回変更することのできる半導体デバイス。

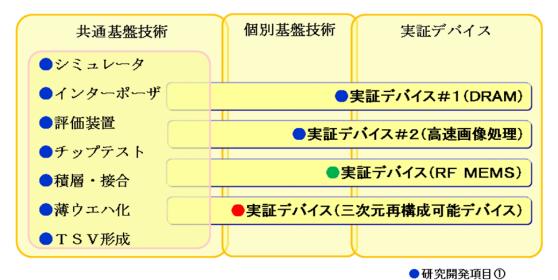

これらの関係を図3に示す。まず①は、主に三次元集積回路基盤技術開発を目的とし、一部、本構造の有効性を示すための実証デバイスの開発を含める。次に②および③は主に、立体構造を生かした適用製品の例として、本構造の有効性を示すための実証デバイスとして開発を実施するものである。産業育成を目的とした場合、基盤技術の開発のみを行うのでは片手落ちであり、どのように役立つかを実証することにより、市場も同時に開拓していく、あるいは潜在ニーズを掘り起こす起爆剤を提供する努力が同時に必要と考えられるためである。これらの実証デバイスの開発の中では、メインに①の中で行う共通基盤的技術開発のほかに、各実証デバイス個々に深く関係した個別基盤技術があるため、その開発も同時に進めることとした。

- · 기호텔닷컴

- ●研究開発項目②

- ●研究開発項目③

図3 各研究開発項目の関係

#### Ⅱ. 研究開発マネジメントについて

### 1. 事業の目標

以下に各研究開発項目の平成22年度末における中間目標、ならびに平成24年度末における最終目標を記載する。まず、各研究開発項目の平成22年度末中間目標および平成24年度末最終目標を列記する。各研究開発項目は、さらに細分化された個別技術課題を設定しており、それらの個別技術課題毎に目標設定を行い、成果管理を行っている。それらの細目は、煩雑を避けるため本章では触れず、「Ⅲ. 研究開発成果について」の章において、目標と成果を対比して示すこととしたい。

前節で述べたように、本プロジェクトの内容は、大別して基盤技術と、その応用可能性を示すための実 証デバイス、そして個別デバイスに深く関係した個別基盤技術に三分して考えている。

第一に、基盤技術としては、三次元化に伴い膨大になる設計工数を現実的な時間内で実施可能なものとするためのシミュレータ技術を開発する。また、三次元積層する際に、良品チップのみを選別して積層する、または良品率の高いウェハを選別して積層しないと、不良品を大量に製造することになる恐れがあるが、それを避けるため、良品を選別するためのテスト技術が不可欠である。テスト技術の内容としてインターポーザ、また評価装置、それらを用いたチップテスト技術を開発する必要がある。また、TSV形成技術、積層技術についても、さらなる開発が必要である。

第二に、実証デバイスは特定のアプリケーションを念頭に、固有の技術を盛り込んで設計・製造することになる。実証デバイスには、現時点で以下の四つの開発課題を実施中である。一つ目は、基本計画に掲げた三つの研究開発項目のうちの研究開発項目①の中で実施することとした「実証デバイス#1」であり、ロジックとメモリを融合した超ワイドバスメモリ素子である。二つ目は、イメージセンサをロジックに積層することで、高速画像処理を可能とするデバイスである。三つ目は、研究開発項目②の中で検討することとした「複数周波数対応通信三次元デバイス技術」である。最後に、四つ目は研究開発項目③の中で検討することとした「三次元回路再構成可能デバイス技術」である。

第三に、実証デバイスそれぞれに関わる個別な基盤的技術としては、複数周波数対応通信三次元デバイス技術の中におけるRF MEMSデバイス開発や、三次元回路再構成可能デバイス技術開発におけるデバイスプロセスのフロー検討がある。

以下、これらの各研究開発項目について、設定目標の概要を説明する。

## 1.1 研究開発項目①「多機能高密度三次元集積化技術」

本技術開発においては、情報通信デバイスや信号処理デバイスの小型化、低消費電力化に必要な、 Si 貫通ビアを用いた三次元積層システムインパッケージ(SiP)を実現するための設計技術および評価解析技術の確立を目標とする。

最終目標として、平成24年末までに以下の目標を達成する。

実用的なアプリケーション仕様に準ずる、Si 貫通ビアを用いた三次元積層 SiP を試作し、機能を検証することで、多機能高密度三次元集積化技術として開発した設計技術と評価解析技術

## の有効性を実証する。

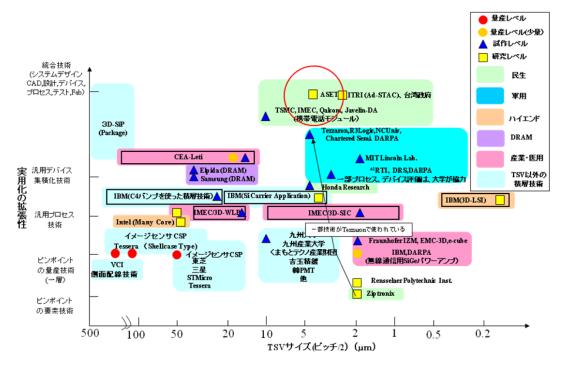

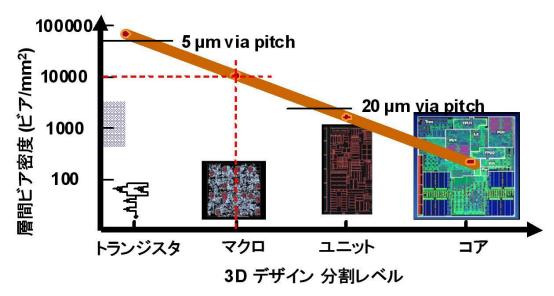

これらの目標の設定理由を図4を用いて説明する。図の縦軸は技術の集積度・完成度を示し、上に行くほど総合的な技術を複合して開発しており製品化への距離が近いことを示す。図の横軸は積層したウェハを貫くTSVのピッチを示し、右に行くほど微細なピッチで結合しており技術的な困難度が高い。図中の赤丸で示した部分が本プロジェクトで狙う目標であり、TSVピッチも世界最高レベルであり、かつ技術的にも設計から製造まですべてをそろえ、事業化に向けて準備を完了させる目論見である。

図4 研究開発項目①に関わる、目標設定に関するベンチマーク図

# 1.2 研究開発項目②「複数周波数対応通信三次元デバイス技術」

本技術開発においては、微小可動構造(MEMS)を用いたMEMS回路、制御・電源回路が積層された複数周波数・複数通信方式に対応する三次元デバイスを開発する。最終的には、ボード基板上に並べられたRF通信デバイスを小型化しSiPとすることが可能な技術を確立する。

また、最終目標として、平成24年末までに以下の目標を達成する。

MEMS 回路、制御・電源回路が積層された複数周波数・複数通信方式に対応する三次元デバイスとして、700MHz~6GHz の周波数帯域で周波数特性可変の MCM を開発し、通信方式ごとの個別回路を MCM 構成にて実装した場合に比較し、実装面積で 1/8 に小型化可能なことを実証する。

# 1.3 研究開発項目③「三次元回路再構成可能デバイス技術」

本技術開発においては、三次元的な積層構造を利用した回路再構成可能デバイス(フィールドプログラマブルゲートアレイ(FPGA)、動的リコンフィギャラブルプロセッサ等)技術を開発する。

平成20年度は、三次元積層を含むデバイス作製プロセスのフロー骨子を決定する。また、三次元配線 密度等の具体的な基本仕様の策定を行うとともに、その仕様に基づき、三次元アーキテクチャの基本構 造の決定と、それにより実現する目標性能及び機能を確定する。

最終目標として、平成24年末までに以下の目標を達成する。

三次元回路再構成可能デバイスのアーキテクチャを実証する。さらに三次元回路再構成可能デバイスのプロセスフローを実証する。

なお、これらの目標は、先述のように、随時見直しを行っており、上記した目標は平成21年3月に見直 しの結果改訂した、平成22年7月26日現在、最新のものである。

#### 2. 事業の計画内容

# 2.1 研究開発の内容

#### (1) 概要

本プロジェクトは、経済産業省「IT イノベーションプログラム」の一環として実施し、これまでの同一機能のメモリの積層による高集積化とは異なり、異機能を持つチップの積層技術、デジタル・アナログ回路や微小可動機構の積層技術、さらには三次元的に積層したチップに対し後からプログラムを書き換えて機能を発揮させる技術など、これまでにない三次元化技術により、新たな機能の発揮と飛躍的な性能向上を実現する立体構造新機能集積回路技術を確立することを目的とする。

(2) 事業全体のスケジュール及び年度別予算

本プロジェクトは多額の資金を投入する国家プロジェクトであり、予算の執行は注意深く行う必要があることをNEDOは強く認識している。予算執行について注意すべき点は以下の通りである。

- 1) 基盤技術であっても、必須な技術開発項目には予算を投じる。

- 2) 事業化間近なフェーズである場合は、助成への切り替え、ないし企業独自の製品開発への移行を推進する。

- 3)企業間の連携により、相乗効果が見込めるテーマを重視し、重点的に予算を配分する。

# 2.2 研究開発の実施体制

NEDOにおいては、研究開発効率上、最適なフォーメーションを組むことにより、研究投資額に対するパフォーマンスの最大化を強く意識している。このため、基本計画検討委員会を組織して外部有識者の意見を取り込み、基本計画を策定した。また、その結果を踏まえてNEDO外部ウェブページに「基本計画」「事前評価書」「資料」(巻末添付資料参照)を公開し、パブリックコメントを募集し、その内容(同じく巻末に添付)を適切に計画に反映した。なおこの一連のプロセスをNEDOポストと呼んでいる。

引き続いて公募を行い実施者を広く募った。外部有識者及びNEDOメンバーからなる採択審査委員会を組織し、応募者の中から、競争の上で研究推進能力、成果の事業化への見通し、など多岐にわたる比較項目を検討し、実施者を選定した。

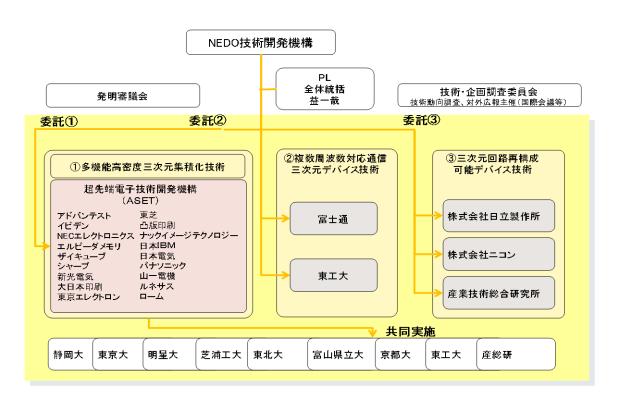

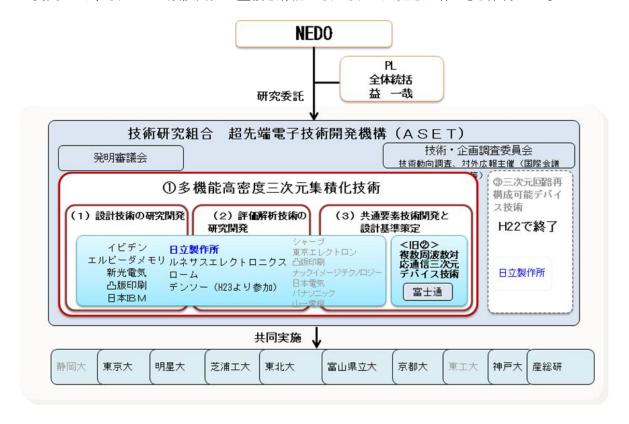

同時に、効率を意識した研究開発項目の組み換えなどに指導力を発揮することを期待し、プロジェクトリーダを委嘱した。図5に、本プロジェクト発足時の実施者フォーメーションを示す。プロジェクトリーダは東京工業大学教授 益 一哉氏に委嘱した。本プロジェクトの特徴として、当初より産官学連携を強く意識し、主たる実施者である技術研究組合 超先端電子技術開発機構から、共同実施先として国内の有力大学研究機関、および独立行政法人 産業技術総合研究所との連携開発を推進してきた。

図5 本ドリームチッププロジェクト発足時の実施者

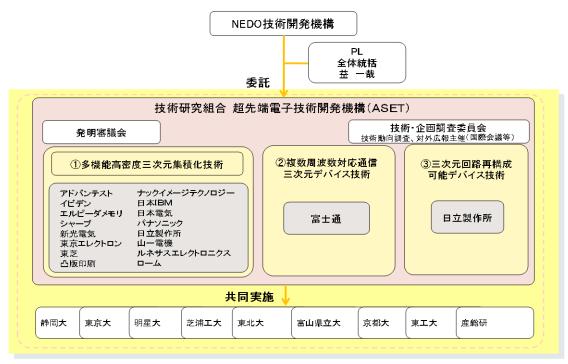

図6 H22年度初におけるドリームチッププロジェクトの実施者フォーメーション

本プロジェクトでは実施者相互の連携を強めるため、随時連絡を取り合い、NEDOのヒアリング等の機会を利用して連携強化を推進した。その結果、H22年度初めにおいて、図6のように、研究開発契約を技術研究組合 超先端電子技術開発機構との間に一本化し、その中で研究開発項目①、②および③のすべてを実施することとした。

# 2.3 研究開発の運営管理

研究開発全体の管理・執行に責任を有するNEDOは、経済産業省および研究開発責任者と密接な関係を維持しつつ、プログラムの目的及び目標、並びに本研究開発の目的および目標に照らして適切な運営管理を実施する。具体的には、年2回開催するNEDO定期ピアリングほか、随時のコミュニケーションを通して運営管理にNEDOの意思を反映させる。

# 2.4 研究開発成果の実用化・事業化に向けたマネジメントの妥当性

NEDO においては、随時ヒアリングを通じて進捗状況を把握し、また国内外の技術開発動向を常にウォッチすることにより、適時・適切なベンチマークに努めている。進捗状況によって事業化が可能と判断できるものに関しては早期に開発を参加企業の自主開発に切り替えを推進している。一方、知的財産権の取得についても奨励しているが、開発項目の性質上特許化するよりも戦略的に不出願にしてノウハウを守ることが好ましいものについては適切に判断すべきと考えている。

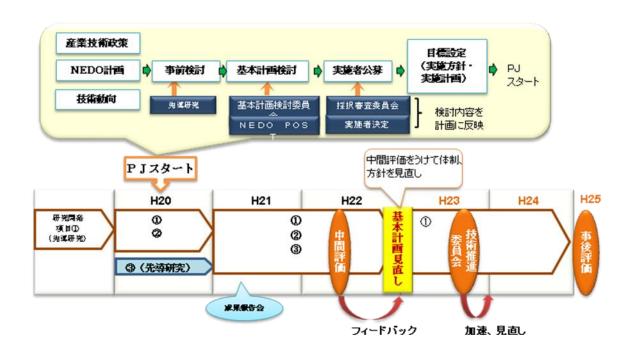

## 3. 情勢変化への対応

本研究開発の計画から実施に至る過程、およびその後の進行予定概要を図7に示す。平成19年度に行った先導研究の成果を受けて開始したが、開始にあたっては、広く企業、民間研究機関、独立行政法人、大学等(委託先から再委託された研究開発実施者を含む)から改めて公募を行って、より良い実施体制を組むべく研究開発実施者が選定され、その上で平成20年度より委託により実施している。平成20年度は先導研究として別契約にて実施していた研究開発項目③を、全体に組み込んで現在は一体として実施中である。なお、図中には省略したが、この組み換えに際しても、外部有識者による採択委員会を組織して最大限その意見を反映した。

図7 ドリームチッププロジェクトの立案から現在に至る経緯

# 4. 中間評価結果への対応

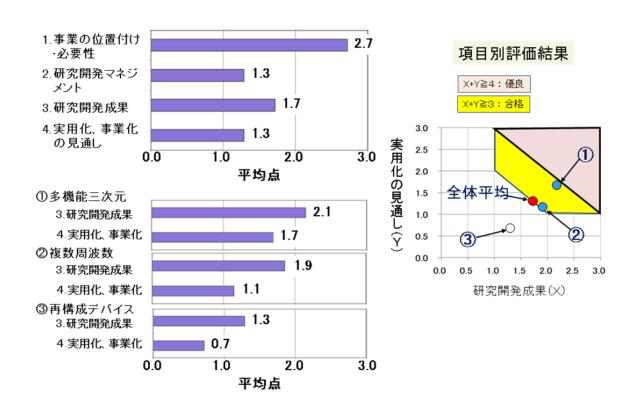

平成22年8月に中間評価を実施した。その結果を図8に示す。

図8 中間評価結果(H22年8月実施)

総合評価では、本技術の必要性、NEDOプロとしての意義について評価を得たが、研究開発項目毎の評価では、実用化デバイスの研究開発項目②、③に関して、三次元積層化の必然性の有無と①の要素技術開発との重複部分に関し指摘をうけ再考を要するとの評価をうけた。

表2 研究開発項目別評価内容

| 研究開発項目                  | 評価                                                                                     |

|-------------------------|----------------------------------------------------------------------------------------|

| ①多機能高密度三次元集<br>積化技術     | 電気系三次元シミュレータ、ウエハー括多端子プローブ技術、ウエハレベルバーンイン技術は世界トップクラスであり評価できる。ただし、ソフトウエア系の技術は利用環境の観点で不十分。 |

| ②複数周波数対応通信三<br>次元デバイス技術 | 有効性に疑問がある。MEMS素子の安定性とコストの点で過去の二の舞とならないように以前の技術蓄積を活用すべき。                                |

| ③三次元回路再構成可能<br>デバイス技術   | 目標値(二次元ICの25%程度の性能改善)は、二次元ICの改良技術でも十分である。三次元ICとすることの優位性、実現性を明確にする必要がある。                |

そこで、以下の3点に関し見直し及び強化を行った。

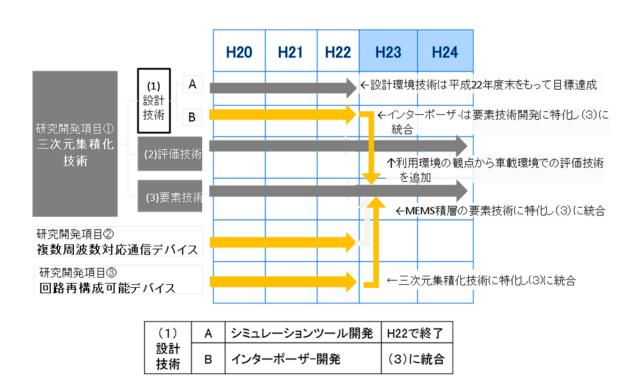

#### 4.1 研究開発テーマの見直し

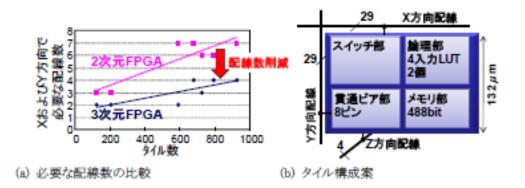

中間評価の指摘をうけ、三次元積層に関する要素技術開発に重点を置くこととし、従来の実用化デバイスは縮小もしくは中止とした。具体的には、研究開発項目①の多機能高密度三次元集積化技術を(1)設計技術、(2)評価解析技術、(3)共通要素技術開発と設計基準策定(製造プロセス技術)に細分化し、個別開発の開発内容を再配置した。次に研究開発項目②の複数周波数対応通信三次元デバイス技術は、異種材料(MEMS)の積層技術に重点を移し、新研究開発項目①の(3)に統合した。研究開発項目③の三次元回路再構成可能デバイス(積層FPGA)は①の内容と重複していた三次元積層要素技術(TSV形成、チップ積層他)を新研究開発項目①の(3)に統合し、実用化デバイス(積層FPGA)の開発は中止とした。

また、旧研究開発項目①の設計技術で開発アイテムとなっていた、インターポーザー開発と電気的インターフェース作成は新研究開発項目①の(3)の共通要素技術開発と設計基準策定に移行した。(図9参照)

図9 研究開発テーマの見直し

# 4.2 実施体制の見直し

研究開発テーマの見直しに伴い ASET における各開発テーマ担当を図10のように変更した。この変更により、それまでの類似開発の重複を解消しそれぞれの知見を共有できる体制とした。

図10 見直し後の実施体制(平成23年度以降)

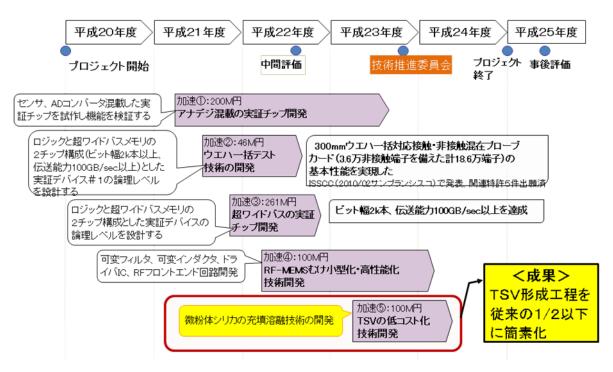

## 4.3 加速資金による研究開発の推進

図11に本プロジェクトの加速案件の概要を示す。中間評価以前の平成22年度までは、実証チップの性能強化に重点が置かれていた。中間評価の指摘をうけ三次元積層の要素技術強化に取り組んだ。具体的には、三次元積層の実用化における最大の課題である製造コスト削減に絞り、TSV形成工程のコストダウン技術の開発に加速資金1億円を投入し、工法、材料の研究開発に取り組んだ。その結果、製造ステップ数を1/2以下にできる目処が立った。(本編Ⅲ-19 参照)

図11 加速資金による研究開発の概要

## 5. 評価に関する事項

NEDOは、技術的及び政策的観点から、研究開発の意義、目標達成度、成果の技術的意義ならび に将来の産業への波及効果等について、外部有識者による研究開発の中間評価を平成22年度8月 に実施した。この中間評価の結果を踏まえて必要に応じプロジェクトの加速・縮小・中止等見直しを迅 速に行った。

また、平成23年12月に外部有識者による技術推進委員会を実施し、進捗状況の確認、最終年度 (平成24年度)の開発内容の確認及びプロジェクト参画企業の事業化にむけた取組について確認を 行った。以上、適宜評価活動を行いプロジェクト終了後の平成25年度に事後評価を実施する。

# 目次

| Ш  | 研究開発成果について                                                                                                                                                                                                                                   |                                              |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1. | 事業全体の成果の概要                                                                                                                                                                                                                                   | <b>Ⅲ</b> −1                                  |

| 2. | 研究開発項目ごとの成果の概要                                                                                                                                                                                                                               | <b>III</b> -2                                |

| 2  | 2.1 多機能高密度三次元集積化技術 (1)次世代三次元集積化設計技術の研究開発(※) (1)-A 設計環境技術の研究開発 ⇒平成22年度で終了(※) (1)-B インターポーザ技術の研究開発 ⇒(3)-Dに統合(※) (1)-C インターフェース仕様書の策定 ⇒(3)-Dに統合(※)                                                                                              | Ⅲ-31<br>Ⅲ-36<br>Ⅲ-41                         |

|    | <ul> <li>(2)次世代三次元集積化のための評価解析技術の研究開発</li> <li>(2)-A チップテスト技術の研究開発 ⇒平成22年度で終了(※)</li> <li>(2)-B 熱・積層接合技術の研究開発</li> <li>(2)-C 薄ウェハ技術の研究開発<br/>成果一覧</li> </ul>                                                                                  | III−44<br>III−2<br>III−7<br>III−11           |

|    | <ul> <li>(3)次世代三次元集積化の共通要素技術開発と設計基準策定</li> <li>(3)-A 実証デバイス研究開発 ⇒平成22年度で終了(※)</li> <li>(3)-B 3Dインテグレーション技術の研究開発</li> <li>(3)-C 超ワイドバスSiP三次元集積化技術の研究開発</li> <li>(3)-D デジアナ混載三次元集積化技術の研究開発</li> <li>(3)-E ヘテロジーニアス三次元集積化技術の研究開発成果一覧</li> </ul> | Ш-48<br>Ш-11<br>Ш-16<br>Ш-21<br>Ш-26<br>Ш-30 |

| 2  | 2. 2 複数周波数対応通信三次元デバイス技術 ⇒平成22年度で終了(※)<br>(1)複数周波数対応可変RF MEMSデバイスの研究開発<br>(2)複数周波数対応通信フロントエンド回路の研究開発                                                                                                                                          | Ⅲ-55<br>Ⅲ-58                                 |

| 2  | 2.3 三次元回路再構成可能デバイス技術 ⇒平成22年度で終了(※)<br>(1)三次元回路再構成可能デバイスに関するアーキテクチャ<br>および設計技術の研究開発                                                                                                                                                           | <b>Ⅲ</b> −60                                 |

|    | (2)三次元回路再構成可能デバイスに関する三次元集積化技術の研究開発                                                                                                                                                                                                           | <b>Ⅲ</b> −63                                 |

(※)については、中間評価にて評価済みのため、『付録』(Ⅲ-31以降)に掲載しております。

#### Ⅲ 研究開発成果について

## 1. 事業全体の成果の概要

ここでは「ドリームチップ」プロジェクト全体の目標と達成度を大まかに記載する。プロジェクト全体の進捗として、すべての研究開発テーマに於いて目標を達成した。一部の開発テーマについては最終目標を前倒しで達成したため、プロジェクトでの研究開発を終了し、企業レベルでの実用化に移行した。又、平成22年度の中間評価の結果を受け、研究開発テーマと開発体制の見直しを行った。それぞれの達成状況を次章以降に示す。

本プロジェクトの研究開発テーマは以下の通りである。

## 2.1多機能高密度三次元集積化技術

- (1)次世代三次元集積化設計技術の研究開発

- (1)-A 設計環境技術の研究開発

- (1)-B インターポーザ技術の研究開発

- (1)-C インターフェース仕様書の策定

- (2)次世代三次元集積化のための評価解析技術の研究開発

- (2)-A チップテスト技術の研究開発

- (2)-B 熱・積層接合技術の研究開発

- (2)-C 薄ウェハ技術の研究開発

- (3)次世代三次元集積化の共通要素技術開発と設計基準策定

- (3)-A 実証デバイス研究開発

⇒平成22年度で終了

⇒平成22年度で終了

⇒平成22年度で終了

⇒(3)-Dに統合

⇒(3)-Dに統合

- (3)-B 3D インテグレーション技術の研究開発

- (3)-C 超ワイドバスSiP 三次元集積化技術の研究開発

- (3)-D デジアナ混載三次元集積化技術の研究開発

- (3)-E ヘテロジーニアス三次元集積化技術の研究開発

- 2. 2複数周波数対応通信三次元デバイス技術

- ⇒平成22年度で終了

- (1)複数周波数対応可変RF MEMSデバイスの研究開発

- (2)複数周波数対応通信フロントエンド回路の研究開発

- 2. 3三次元回路再構成可能デバイス技術

- ⇒平成22年度で終了

- (1)三次元回路再構成可能デバイスに関するアーキテクチャおよび設計技術の研究開発

- (2)三次元回路再構成可能デバイスに関する三次元集積化技術の研究開発

これ等のうち、開発目標を前倒しで達成した (1)-A、(2)-A、(3)-A、2.2、2.3は平成22年度で終了した。また、(1)-Bと(1)-Cは平成23年度より(3)-Dに統合した。

これら平成22年度(中間評価時点)で終了した開発テーマ及び統合されたテーマの成果は、付録として本章の末尾に記載した。

このため、以下の研究開発成果の記載に関しては、上記**太字で示した研究開発テーマ**を対象としており、連続した項番とはなっていない。

# 2. 研究開発項目ごとの成果の概要

研究開発項目ごとの成果を記載する。

# 2.1 多機能高密度三次元集積化技術

# (2) 次世代三次元集積化のための評価解析技術の研究開発

# (2)-B 熱·積層接合技術の研究開発

#### (2)-B-1 目標の達成度

1)基本計画の目標

(概要)

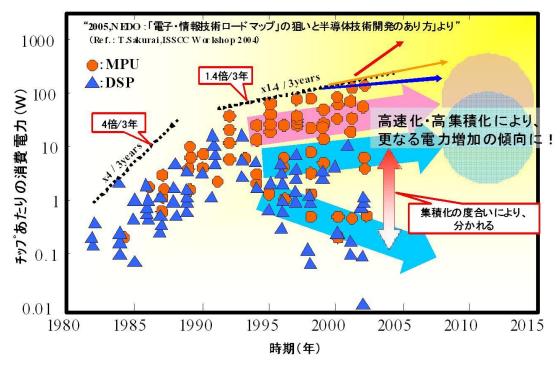

電子機器の基本機能を担うMPU(Micro-Processing Unit)・DSP(Digital Signal Processor) などの 半導体 LSI(Large Scale Integrated Circuit) 製品の消費電力については、微細化・高集積化・高速 化により、1990 年頃まで、"4 倍/3 年"のペースで増加する傾向にあった。しかしながら、電子機 器の多様化により、1990 年以降は、性能優先(高機能)製品と、消費電力優先(低消費電力化)製 品に二分化され、それに合わせて、性能優先(高機能)製品の電力増加も"1.4倍/3年"のペース とやや鈍化する傾向となった。しかしながら、半導体 LSI 製品の消費電力は、ペースを落としつつ も、依然増加傾向にあり、2010 年以降の半導体 LSI 製品(単チップ)の消費電力は、少なくとも、 MPU は 50W 以上、DSP は 15W 以上になることが予測される。 さらに、三次元的に複数チップを 積層することにより、MPU・DSP などの消費電力推移予測を超えて、半導体 LSI 製品の消費電力 の増加を加速させ、20W を超える DSP 製品がでてくることが予想される。一方、比較的消費電力 の小さい現状のデジタルコンシューマ機器では、小型・薄型などの厳しい要求下で数W程度の放 熱性能が達成されている。しかし、高機能化にともなう総消費電力の増加や電力集中などから熱が 大きな問題となってきており、加えて、静音性などの新たな機能要求から熱対策が制約されるなど、 いっそう熱課題が増加する傾向にあり、小型・薄型かつ静音性を要求される条件下においても、20 W程度の放熱を可能とする新規技術開発は不可避と考えられる。 参考として 図(2)-B-1 に NEDO による消費電力推移のグラフをあげる。

図(2)-B-1 チップあたりの消費電力

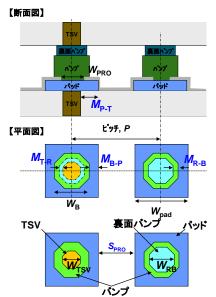

本プロジェクトでは目標としてシリコン貫通電極 (TSV: Through Silicon Via)の接合バンプ径は 5 μ m以下、接続バンプ 10,000 個以上を掲げている。このバンプ径は、図(2)-B -2 に示すグラフの三次元デザイン分割レベルとしてマクロレベルを考えた場合に対応する。

\*\* IBM J R&D -2006. A. W. Topol et al..

図(2)-B-2 チップの集積化レベル

チップのテクノロジーによって、バンプ径要求に差異はあるかと思われるが C2C(Chip to chip)接合による実装では、この分割が微細度が最も高いレベルであると思われる。TSV や接合部を配置したチップ部分に能動素子を配置できないと仮定すると、接合や TSV のエリアは実装のためのペナルティーとなる。このエリアペナルティーを仮に 1%まで許すものとすると、接合バンプ数は 1cm² あたり、10,000 個となる。このバンプ径とバンプ数を前提とした高信頼のチップ間接続技術の開発とその信頼性を評価するための技術を開発し、三次元積層 SiP (System in Package) を実現するために必要な接合バンプ構造の標準化と最適接合条件を確立することが必要である。

#### (基本計画)出典:基本計画 P5

三次元集積化の熱評価解析技術、積層接合評価解析技術を開発する。

# 出典:基本計画 P6

最終目標(平成24年度):

・ ひとつの三次元積層 SiP あたり 20W 以上の発熱に対応する放熱構造の評価解析技術を開発する。

# 2)開発成果の要約

- 2)-1熱評価および積層接合評価解析技術の研究開発

- 2)-1-1熱評価および放熱対策技術の研究開発

熱評価および放熱対策技術の研究開発では、Cu-TSVが微小・極薄積層構造体における熱伝導に与える効果を、三層積層 TEG (Test Element Group) である TV200 (実デバイスの動作状態を再現するための発熱部、測温体、TSV を有する)を用いた実測によるパラメータ導出方法を開発し、このパラメータを使ったシミュレーションを行う三次元 SiP の高精度熱特性評価技術を確立した。こ

#

の評価に基づき、積層チップ間及び薄チップ面内の熱伝導評価を行い、チップのバンプ配置設計 指針を取得した。

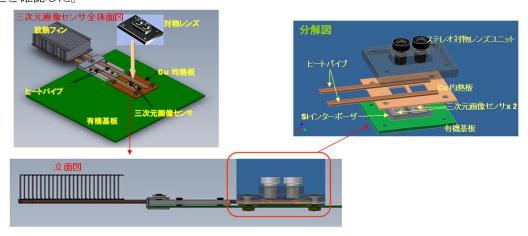

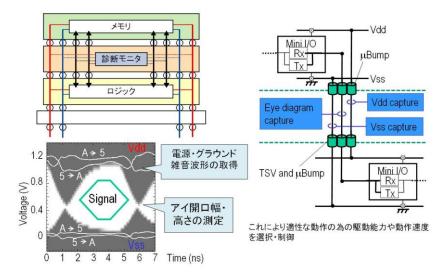

この指針に基づき、自動車用運転支援画像処理システムの小型・高効率冷却システムの開発では、積層画像センサ内の温度勾配が約 10℃(2 watt 発熱時)に収まる設計を行った。高温環境下での放熱冷却構造の研究開発では、画像モジュール(CIS: C-MOS Image Sensor、CDS: Correlated Double Sampling、ADC: Analogue to Digital converter、IF: Interface)を搭載するSi-IP(Silicon Interposer)から直接筺体に放熱する超小型ヒートパイプでの冷却構造が可能であることを確認した。

図(2)-B-3 自動車運転支援画像システムの冷却システム

また、20W/cm<sup>2</sup>の発熱体を、システム筐体を放熱器として自然空冷で放熱できる構造を開発し、 実験及びシミュレーションによって、その性能を確認した。

#### 60 N. C. Temp. 150 H. P. Temp. Temperature rise on heater 50 40 30 N. C. Temp. 解析モデル : 自然対流のみで フィとートシンク: 幅60mm 設置高さ80mm フィン高さ20mm フィン枚数5枚 板厚5mm 材質: Al 20 ヒートパイプ: □1cm x 1cm 全長150 mm 冷却したケース 10 H. P. Temp. : ヒートパイプを利用 して伝熱促進を ヒートパイプ出口・ 筐体壁に直接 フィンを取り付け 6 9 12 15 18 21 試みたケース Heat dissipation [W]

ヒートパイプを利用したシステム(自然対流冷却)

図(2)-B-4 20W/cm<sup>2</sup>の発熱体に対応する冷却システム

# 2)-1-2積層接合評価解析技術の研究開発

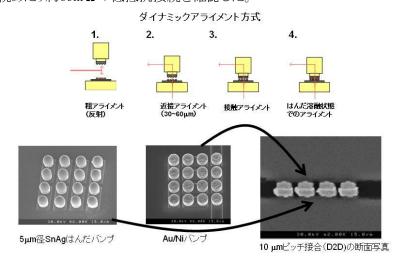

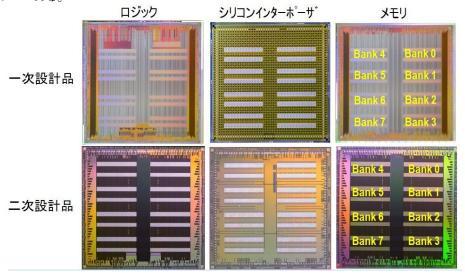

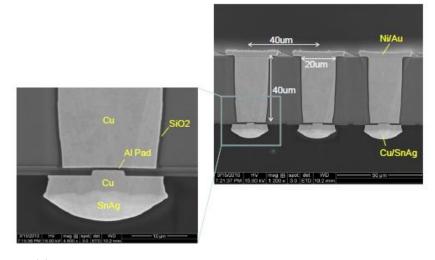

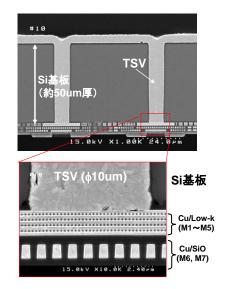

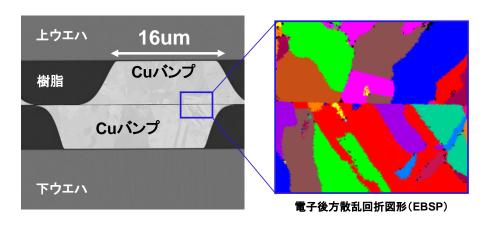

積層接合評価解析技術の研究開発では、超微細 $(10 \, \mu \, m)$ 接合ピッチの接合技術開発のために、  $10 \, \mu \, m$ TEGと、より信頼性の高い、やや大きな $(40 \, \mu \, m)$ TEGを組み合わせることによって、微細接合技術開発を実施する手法を開発した。この方法を適用し、C2C 接合のはんだバンプ構造最適化を行った。この最適化構造バンプを適用し、統合ES#2チップの4層接合を確認した。

# 2.1 多機能高密度三次元集積化技術 (2)次世代三次元集積化のための評価解析技術の研究開発

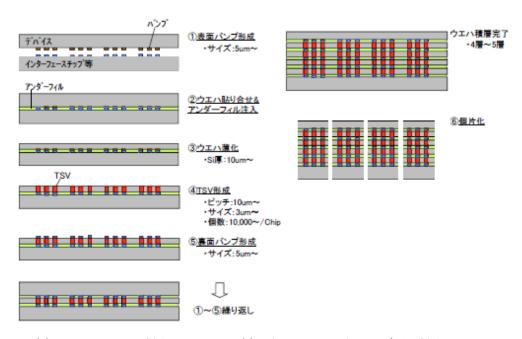

微細接合においてバンプ接触時およびはんだ溶融時に発生する位置ずれを修正するダイナミックアライメント技術と、1N以下の低圧圧着技術を適用することにより、 $\pm 0.6\,\mu$  m以下の接合精度を達成した。この技術を適用して10  $\mu$  mピッチ11,520バンプのデイジーチェインTEG(TV10)の接合を実施し、1接続あたり約69m  $\Omega$ の低抵抗接続を確認した。

図(2)-B-5 10 µm ピッチのマイクロバンプ接合技術

微細接合チップ間の狭ギャップ(<10 µ m)対応するとともに、積層プロセスの高スループットと高信頼性が期待できる、チップ間封止先樹脂(プリアプライ)法と、この手法を発展させた一括接合技術を開発し、キャピラリ法樹脂封止と繰り返し接合を行った場合と同等の接合抵抗を得ることができることを確認した。三次元画像センサ接合に適用できる、低温(<180℃)接合バンプ形成技術を開発し、このバンプを用いた低温接合プロセスを開発した。

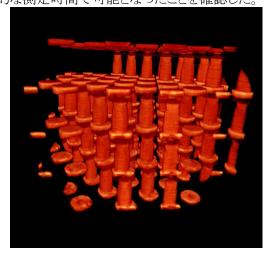

検査評価技術では、X線CT装置の機能向上開発により、従来困難であった $1\mu$  m台の微細な TSVボイドの観測が実用的な測定時間で可能となったことを確認した。

図(2)-B-6 X線CT装置によるTSV観測

#### 3)最終目標の達成度

以上の内容を表(2)-B-1 にまとめる。このように、基本計画に定義された最終目標は達成された。

# 表(2)-B-1 目標と達成状況

| テーマ        | 目標                                                                                    | 成果                                                                                                                | 達成度 |

|------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|

| 熱·積層接合評価技術 | ・20W以上の発熱に対応する放熱構造の評価解析技術を開発する。<br>・車載環境下での放熱冷却構造の最適化設計と、評価解析技術の開発<br>・放熱設計技術仕様書を策定する | ・TSVをもつTEG三積層構造で熱伝導パラメータ抽出手法を開発。シミュレーションとコリレーションから熱特性評価技術を確立。・20W/cm2に対応する放熱構造は、ヒートパイプを介してシステム筐体に放熱する構造とすべきことを確認。 | 0   |

# (2)-B-2 成果の意義

従来、世界的にも次世代三次元積層 SiP の熱評価技術・冷却技術は系統的に研究されておらず、基本データが存在しなかった。本研究では三次元微細接合技術を開発し、微細接合部の分析や機械特性評価観測技術を開発し、微細接合部の熱特性測定を行い、測定によって求めたパラメータを活用した熱伝達シミュレーション技術を開発した。これらの研究成果は次世代三次元積層 SiP を実現するための小型高性能冷却システムに活用することができる。

また、本研究で開発した三次元微細合技術の一つである、封止樹脂をあらかじめチップや基板に塗布しておき、これらの金属バンプを溶融接合すると同時に、樹脂を重合硬化する技術(プリアプライ方式)は、10 µm ピッチレベルの微細接合を製品に適用するときに、コストや製品歩留まり、信頼性を確保する上で大きな役割を果たすことが期待される。本技術は、世界的にも実用化されておらず、チップ積層だけでなく、ウェハ積層の微細接合の技術としても適用できると考える。

#### (2)-B-3 知的財産権の取得及び標準化への取組

成果を特許として出願した。出願状況を以下にまとめた。

H23 年度 7 件出願済み H24 年度 4 件出願済み 2 件出願準備中

# (2)-B-4 成果の普及

学会、講演会などを通じて、以下にまとめたように成果を発表し普及に努めた。

H21年度 8件 国際会議3件

H22年度 9件 内国際会議 4件

H23 年度 17 件 内国際会議 10 件

H24年度 16件 内国際会議 8件

#### (2)-C 薄ウェハ技術の研究開発

# (2)-C-1 目標の達成度

1) 基本計画の目標

(概要):背景の概要を含む