### ITイノベーションプログラム・エネルギーイノベーションプログラム

# 「高速不揮発メモリ機能技術開発」

(2010年度~2012年度 3年間)

(事後評価)

プロジェクトの概要 (公開)

「研究開発成果」

エルピーダメモリ シャープ 産総研 中央大学 2013年 11月18日

18

### 目 次

公開

Ⅰ. 事業の位置付け・必要性

(NEDO)

Ⅱ. 研究開発マネジメント

(NEDO)

III. 研究開発成果

(エルピーダメモリ)

IV. 実用化・事業化に向けての 見通し及び取り組み (エルピーダメモリ)

3.1 プロジェクトの概要

### プロジェクトの背景1

### 公開

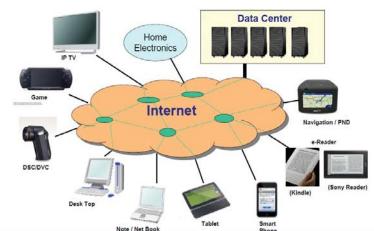

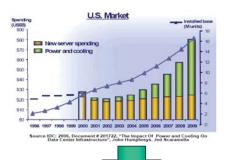

◆コンピューティングのパラダイムシフト クラウド・コンピューティング

全てがクラウドの中でつながる。 Mobile機器、電子Bookなど需要が高まり、 通信量が増大。

◆クラウド・コンピューティング の理性へ

の環境への影響

⇒ストレージ容量の増大、データセンターの巨大化 ⇒ストレージ環境、発熱の問題→冷却コストの増大 例) 2020年2ギガIOP/秒のデータ処理に必要な設備

HDD : 必要台数:500万台

設置面積:16,500 ft2 消費電力:22メガワット

HDDシステムを代替する

◆低消費電力化、低コスト化、 高性能化を実現する 不揮発デバイスの要求大

事業原簿:17ページ

20

Ⅲ. 研究開発成果

3.1 プロジェクトの概要

### プロジェクトの体制

東京大学

→中央大学)

公開

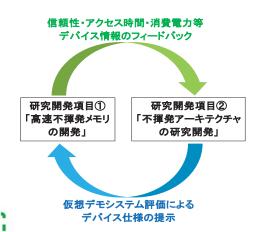

◆研究体制の詳細

研究開発項目①「高速不揮発メモリの開発」

◆密接な研究項目の連携

密接な連携の下、研究開発を推進 迅速なフィードバックを通して、 デバイス・システムのブラッシュ アップを計る。

製品の特徴を生かしたシステム 開発及び標準化を実施。

事業原簿:17ページ

研究開発項目②「不揮発性アーキテクチャの構築」

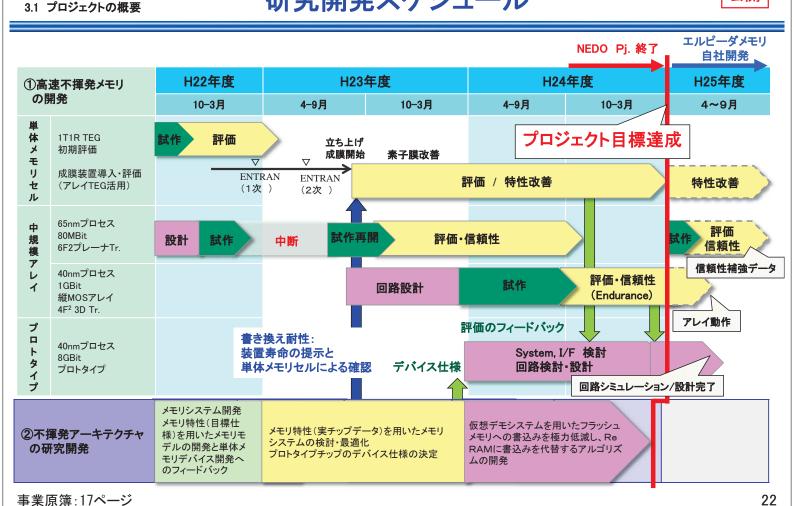

### 研究開発スケジュール

公開

Ⅲ. 研究開発成果

3.2 事業全体の成果

### 研究開発項目の目標と達成状況

公開

23

#### ①高速不揮発メモリの開発

| 目標 |                                                                                                                | 成果                                               | 達成度 | 今後の課題          |

|----|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----|----------------|

| 1  | DRAMの書き換え耐性以上(≧10 <sup>16</sup> 程度)<br>または、研究開発項目②との組み合わせに<br>おいて、実質的に適用製品の装置寿命と同<br>等であること(≧10 <sup>5</sup> ) | 研究開発項目②より実用化に必要な装置寿命は≥105。デバイス性能は108を達成し、目標をクリア。 | 0   | バラツキの改善        |

| 2  | 書き込み電流:50uA以下/セル                                                                                               | <30uA の実力を有することを確認                               | 0   |                |

| 3  | 容量:1Gbit以上                                                                                                     | 中規模アレイ(1Gbit)の設計・評価完。<br>8Gbitプロトタイプ設計完。         | 0   | 実用化の判断         |

| 4  | 書き込み時間:ランダム3nsec以下<br>実用化目標10ns以下(off chip)                                                                    | <10ns(Off Chip)の実力を有することを確認                      | 0   | 縦MOS Tr特性・バラツキ |

| 5  | 動作温度上下限:0~55℃で動作                                                                                               | 保持特性: 240年@55℃達成                                 | 0   |                |

| 6  | そのほか、民生用情報機器への適用時に致命的な制約がないこと                                                                                  | 民生機器の実用化レベルまで達成している                              | 0   |                |

#### ②不揮発アーキテクチャの研究開発

|   | 目標                                                                            | 成果                                                                                                     | 達成度 | 今後の課題 |

|---|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-------|

| 1 | 研究開発項目①で得られたメモリを用い、<br>現行のアーキテクチャの消費電力に対し、<br>実質上1/10以下に削減する不揮発アーキ<br>テクチャの提示 | 高速不揮発メモリに書き込みを代替するアーキテクチャと制御アルゴリズムを開発することに成功。<br>その結果、消費電力を従来SSDアーキテクチャより<br>実質1/10とすることができ、本研究の目標を達成。 | 0   |       |

◎ 大幅達成、〇達成、△達成見込み、 ×未達

事業原簿:18ページ

3.3 研究開発項目毎の成果

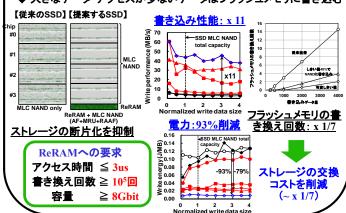

### ②不揮発アーキテクチャの研究開発

### 不揮発アーキテクチャの研究開発【実施者:中央大学,エルピーダメモリ(2010年度のみ)】

#### 目的

◆研究開発項目①で得られたメモリを用い、現行のアーキ テクチャの消費電力に対し実質上1/10以下に削減する 不揮発アーキテクチャの構成事例を提供

#### 機能配述モデルを組み合わせた 実施内容 仮想デモシステムを開発 最適なアーキテク チャ・ReRAMの仕様 ◆ 仮想デモシステムの開発 プラットフォームCADの構築 DRAM ReRAM ◆ ReRAMとフラッシュメモリの ハイブリッド構成の低電力メモリ システムレベルの消費費力・件能等を評価 システムを提案し、電力1/10以下 MLC RAM NAND SSD controlle Tables DRAN SCM (ReRAM Host MLC USFT / dy/Busy, NAND PCI / MRII / H H H ← TS\ SSD SAS, USB, ReRAM

#### 結果

- ◆ データサイズ、書き込み頻度に応じて最適な書き込みを選択

- ◆ 断片化したデータ、頻繁に書き換えるデータはReRAMに記憶

- ◆ 大きなデータ・アクセスが少ないデータはフラッシュメモリに書き込む

#### 成果のまとめ・残された課題 電力1/10以下を達成

電力93%削減、性能11倍増加、信頼性7倍を同時に達成

・ReRAMのスペックを明確化し、研究①にフィードバック アクセス時間≤3us、書き換え回数 ≥105回、容量 ≥8Gbit

課題)実用化するアプリケーションでのアルゴリズムの最適化

24

事業原簿:19ページ

Ⅲ. 研究開発成果

3.3 研究開発項目毎の成果

### ①高速不揮発メモリの開発

公開

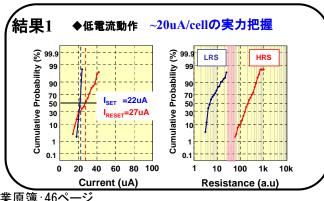

### 単体メモリセル評価【実施者:エルピーダメモリ、産総研、シャープ】

#### 目的

- ◆書き込み電流≦50uAを目指したメモリセル抵抗素子膜の 成膜プロセス条件の最適化

- ◆高速書き込みなどのReRAM特性の確認、及び、書き換え 回数・データ保持特性などの信頼度データ取得

#### 実施内容

◆中規模アレイTEGと同等のメモリセルを1T1R構成で評価 (下部電極サイズ:50nmq) 試作TATを短縮し、早期のプロセスフィードバックを実現

#### 結果2 SETパルス印加後抵抗 ◆高速書き込み (a.u) lset 22uA : 1 10nsecでの Iset 28uA 高速&低電流 書き込み達成 1.E-08 1.E-07 1.E-06 1.E-05 1.E-04 1.E-03 SETパルス幅(sec) ◆1E8サイクル書き換え耐性 (no Verify) 108サイクル 100k 達成 Resistance (a.u) 10k 1k 100 10 1-100 10M 100M 10K 100K 1M **Switching Cycle**

### 成果のまとめ・残された課題

成果) 低電流動作,高速書き込み,SCM実用化目標以上の 書き換え耐性を確認。

課題) 更なる微細化セル対応用に電流低減を目指す

事業原簿:46ページ

25

## ①高速不揮発メモリの開発

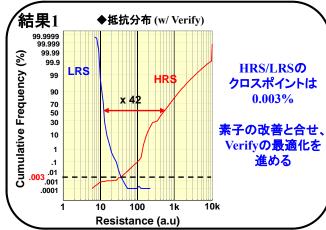

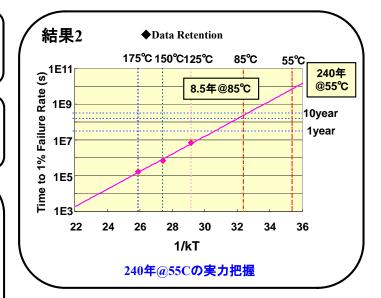

### 2)-1 中規模アレイ チップ開発・評価【実施者:エルピーダメモリ,シャープ】

#### 目的

◆64Mbitの容量を持つアレイTEGにて、ReRAM特性ばらつき の低減及び信頼性データの蓄積を行う

#### 実施内容

◆設計最小寸法65nmプロセスで、選択デバイスにプレーナー タイプのMOS Tr.を使用

事業原簿:47ページ

#### 成果のまとめ・残された課題

<mark>成果</mark>) 不揮発メモリとして240年@55Cを実現。

課題 抵抗分布の改善

\*tail bitの不良解析、Verify最適化ほか推進中

26

- Ⅲ. 研究開発成果

- 3. 研究開発項目毎の成果

### ①高速不揮発メモリの開発

公開

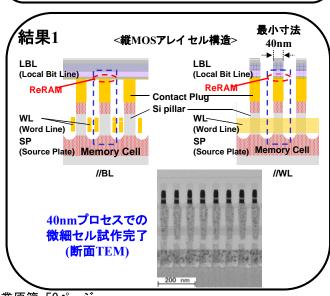

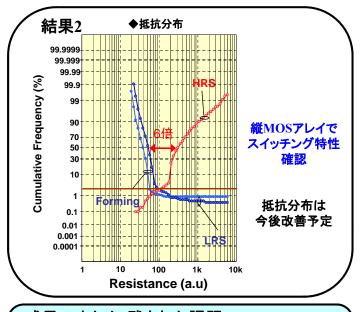

### 2)-2 中規模アレイ 縦MOSアレイTEG開発・評価【実施者:エルピーダメモリ,シャープ】

#### 目的

- ◆大容量プロトタイプで用いるセル構造(設計最小寸法40nm プロセス&選択デバイスにセルサイズが4F2となる縦MOS Tr. 適用)を用いた設計と開発

- ◆1Gbitの容量を持つアレイでの特性評価

#### 成果のまとめ・残された課題

成果

- •40nmプロセス,4F2セルの試作成功。

- ・ギガビットアレイでReRAM特性を確認。 ⇒ストレージクラスメモリ実現への可能性を提示

課題) 抵抗分布の改善 (セルトランジスタ周りのプロセス改善ほか)

事業原簿:50ページ

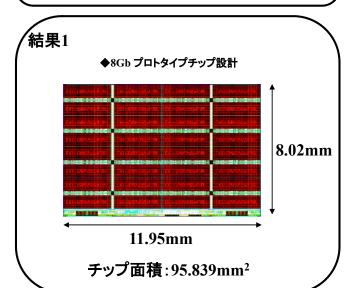

## ①高速不揮発メモリの開発

### 3) 大容量プロトタイプチップ設計【実施者:エルピーダメモリ】

#### 目的

◆「不揮発アーキテクチャ」に適用可能な大容量プロトタイプ チップの設計

- ◆チップ全体シミュレーションにより動作確認

- ◆目標仕様に対するシミュレーション結果は以下の通り

| 項目                              | 目標                                        | シミュレーション結果                             |

|---------------------------------|-------------------------------------------|----------------------------------------|

| ページプログラム時間 (typical)            | 8us                                       | 8.48us                                 |

| ブロック消去時間 (typical)              | 0.5ms                                     | 0.78ms                                 |

| 1stアクセス時間 (max.)                | 1us                                       | 1.2us                                  |

| シリアルアクセス時間 (min.)               | 5ns                                       | 5ns                                    |

| Din/Dout<br>スループット (max.)       | SDR Mode: 200MB/s<br>Toggle Mode: 400MB/s | 200MB/s<br>400MB/s                     |

| 動作電流1 (max.)<br>@Din/Dout Burst | SDR Mode: 30mA<br>Toggle Mode: 200mA      | 46.3mA (@tCK=5ns)<br>8.5mA (@tCK=30ns) |

| 動作電流2 (max.)<br>@Program/Erase  | 30mA                                      | Program:49.22mA<br>Erase:24.85mA       |

| スタンバイ電流 (max.)                  | 50uA                                      | 19uA                                   |

#### 成果のまとめ・残された課題

成果) 8Gb プロトタイプチップ設計完了。

課題

目標仕様未達項目について、チップ内動作の最適化を行なう

事業原簿:51ページ

28