戦略的省エネルギー技術革新プログラム フェーズ名:実用化開発

# シリフォト32G光送受信器の開発

プロジェクト実施者: アイオーコア株式会社

プロジェクト実施期間: 2018年7月~2021年2月

# 1-1.研究開発の背景

# PCIe Gen5に適合の光送受信機 コンピューティング応用に注力したシリコンフォトニクスベースの32G光送受信器を開発

### 背景

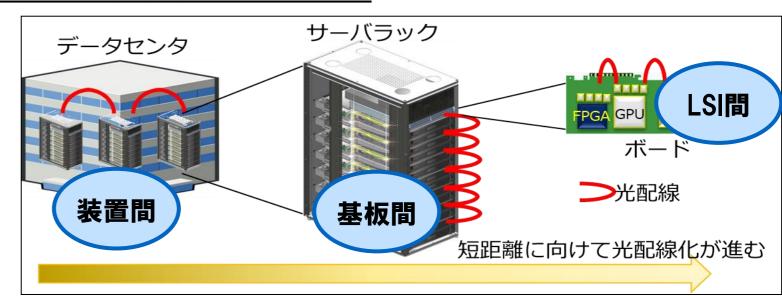

- ■光配線は短距離領域に向けて進む

- 光トランシーバの小型,省エネ,高速化がますます重要に

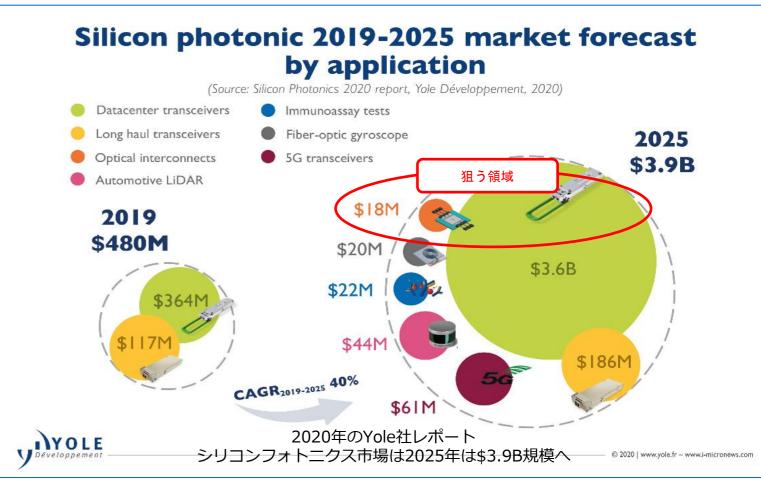

- ■光トランシーバの主流はシリフォトになってきている シリフォトのマーケット予測も大幅に伸長

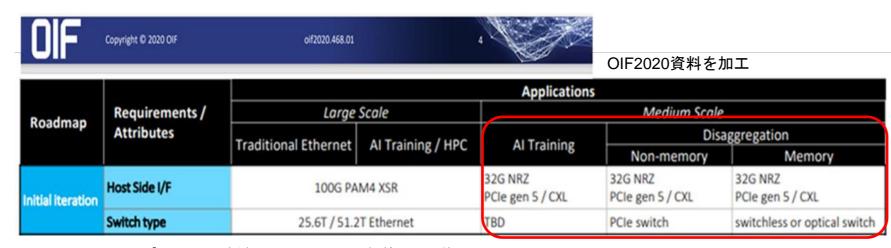

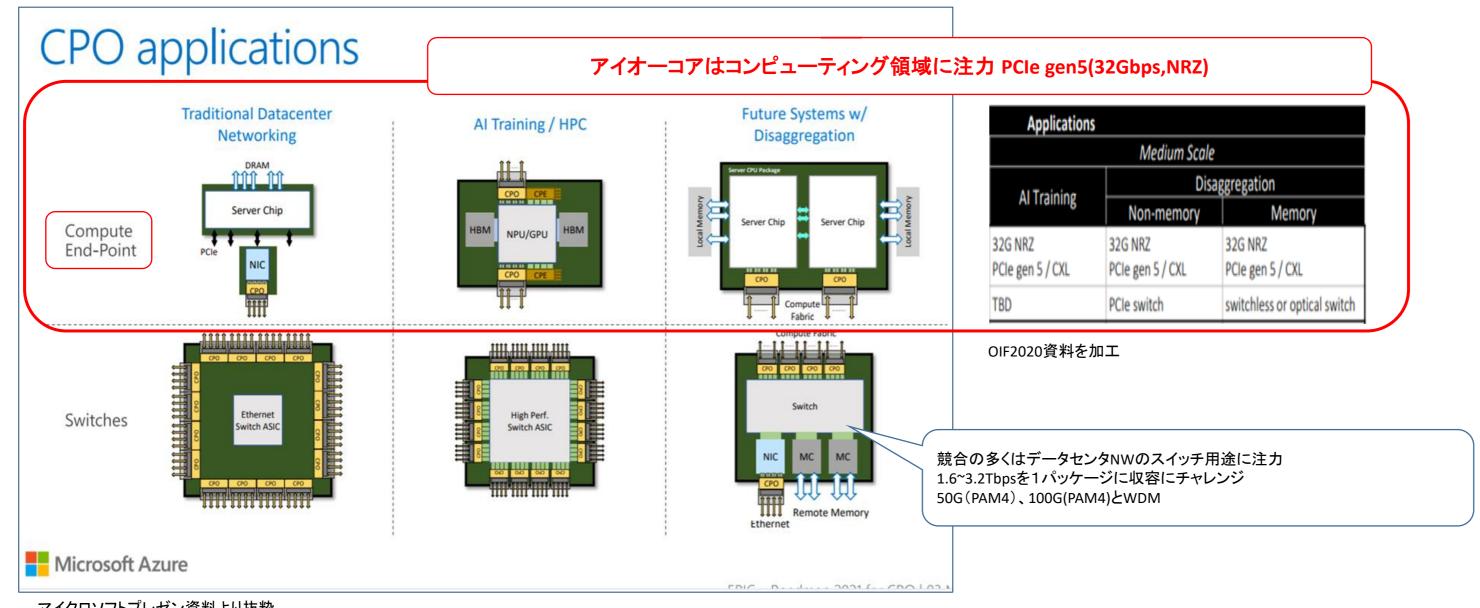

- ■データセンタに加え コンピューティングへの適用の動き活発化

- 32G (PCIegen5、CXL) 適用の光インタフェースの規格化議論が 2 0 2 0 よりOIFにて始まる

PCIe gen5、コンピュータの高速インタフェース規格、5世代(32Gbps) CXL(Compute Express Link)、PCIeをベースにしたインターコネクト規格 OIF(The Optical Internetworking. Forum)、光接続の規格を策定する業界団体

# 1-1.研究開発の背景

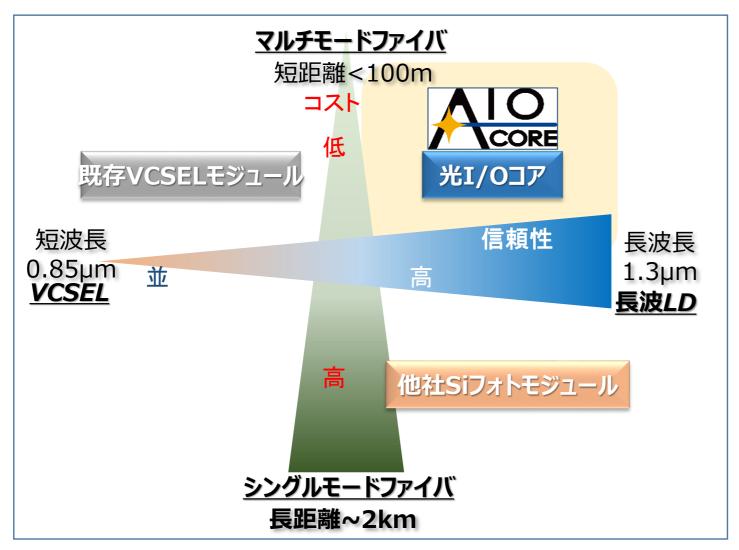

# アイオーコア社の立ち位置と競合技術

■ VCSEL: 25Gbpsより高速の光トランシーバ開発が鈍化、Siフォトへの期待が高まってきている

■Siフォト:各社データセンタNWむけ50G(25G×2) PAM4の方向へ、32G\_NRZは取り残されている

■低コスト、高信頼の32GbpsSiフォト(光I/Oコア)をPCIe gen5のタイミングに合わせ開発

アイオーコア社の立ち位置

Siフォト光トランシーバの比較 MMF-100m CORE アイオーコア コンピューティング用途 に特化 Si photo circuit Passive alignment 25G→32Gへ Passive alignment 構造シンプル Optical Grating 小型、低コストで QD-FP Modulator coupler Pins 優位 LUXTERA/CISCO SMF2km Si photo circuit Active alignment 大規模SW用途 Active alignment 25G→50GPAMへ Grating DFB LD 1ch チップサイズ大 coupler Modulator coupler Isolator/Lenz SMFアセンブリ 構造複雑 **INTEL PSM4/CWDM** →コスト大 Active alignment Si photo circuit Hvbrid Si LD Si Raman LD Isolator/Lenz Modulator Mirror SMF0.5-2km INTEL/AYAR LABS 大規模SW用途 External 50GPAM Si photo circuit Active alignment Active alignment LD Module 外部光源 Multi ch Ring Grating Grating 特殊ファイバ必須 coupler Modulator WDM LD coupler SMFアセンブリ Isolator/Lenz? 構造複雑 →コスト大

# 1-2.研究開発の目的、目標

- > 現在保有の25Gbpsのコア技術を基盤に主要部の性能を向上し、PCIeGen5(32Gbps)適合の光トランシーバを実現する

- ▶ 帯域、受光感度、利得等の、複雑なトレードオフ関係の最適化

- ➤ 新型デバイス構造、消費電力の最小化等で、32Gbps化を図る

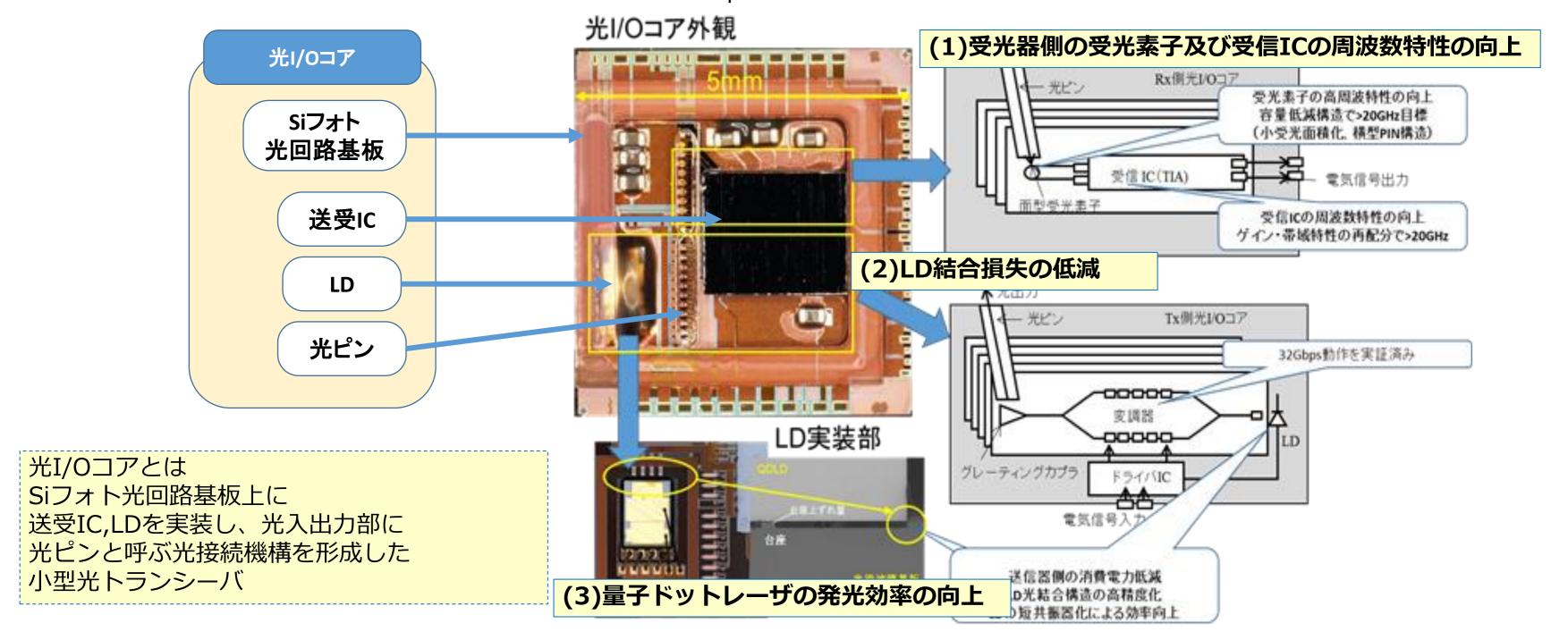

# 2-1.研究開発内容

# 32G光送受信機、開発の狙い

■目的:25Gbps/ch光I/Oコア技術をベースに32Gbps/ch (PCI5.0) 光I/Oコアを開発

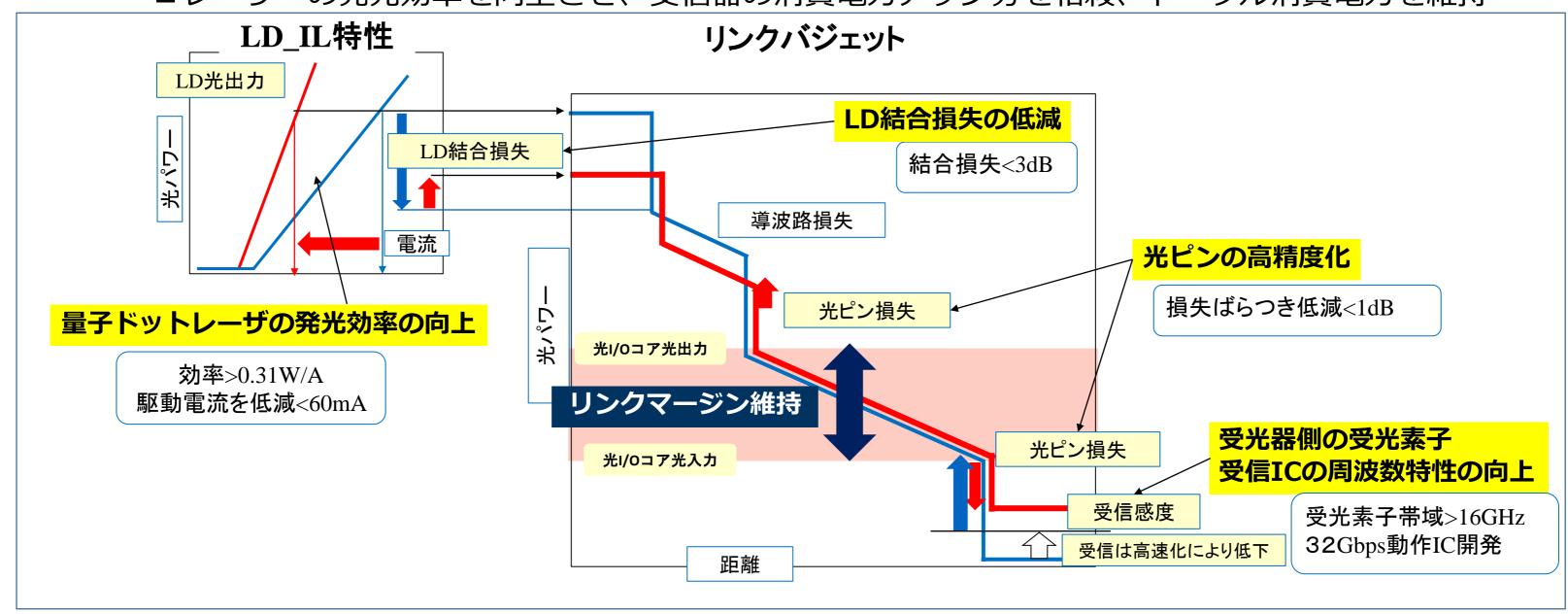

■目標:消費電力、リンクマージンを犠牲にせず32Gbps動作を実現

■ 受信器の受信感度低下分をLD結合損失、光ピン損失低減でリンクマージンを確保

■レーザーの発光効率を向上させ、受信器の消費電力アップ分を相殺、トータル消費電力を維持

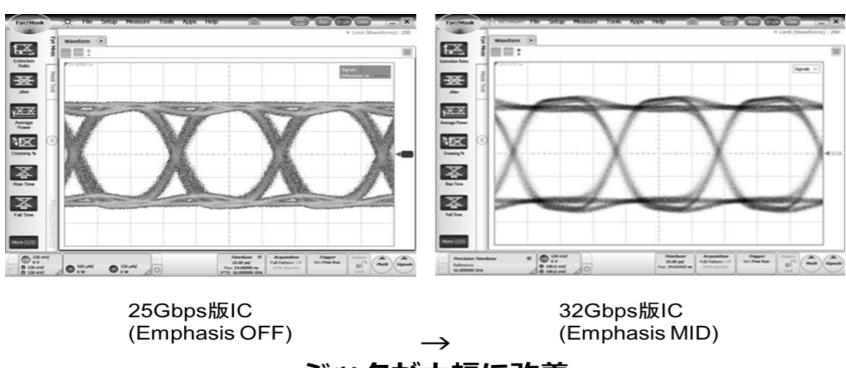

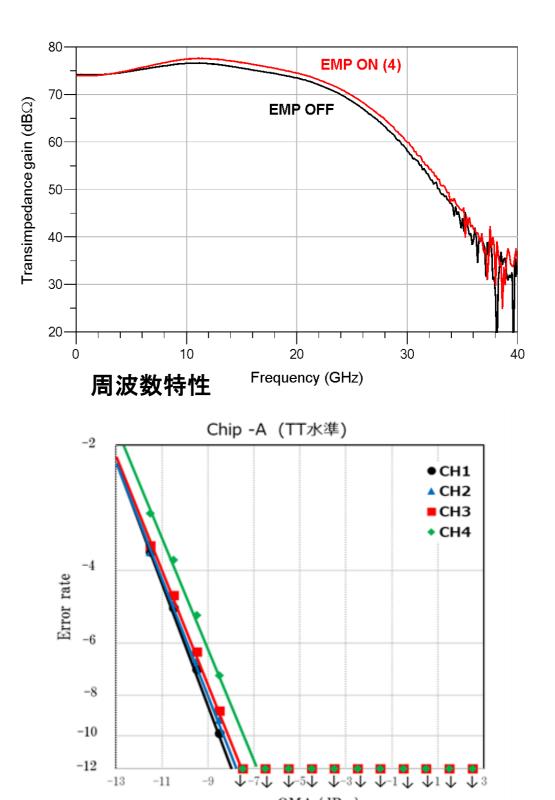

# 3(1)1)受信ICの周波数特性の向上

・32Gbps動作の受信ICを開発 設計通りのアイ開口、周波数特性を確認 光I/Oコアチップに搭載し特性検証を実施(後述)

### 32G受信側出力波形

ジッタが大幅に改善

チップ単体の受信感度<sup>OMA (dBm)</sup>

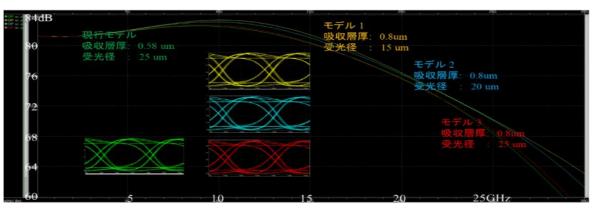

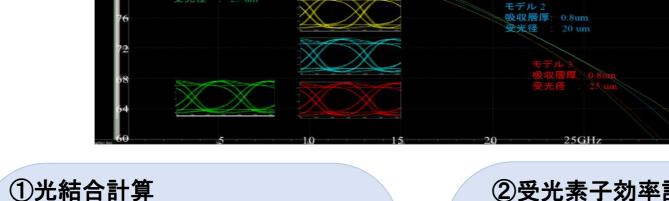

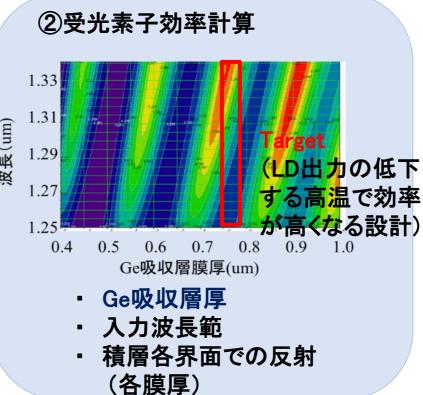

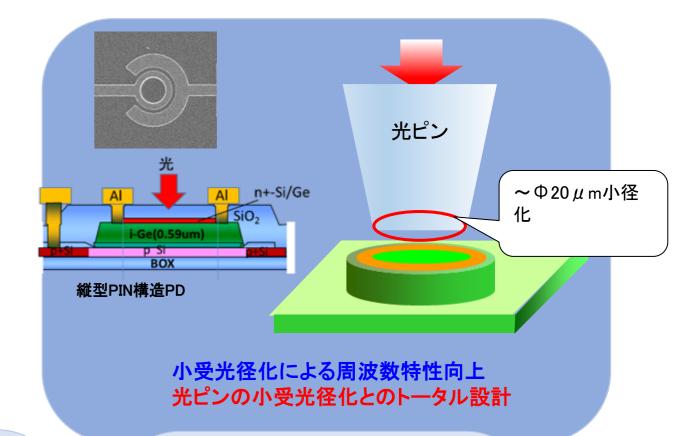

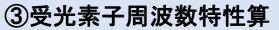

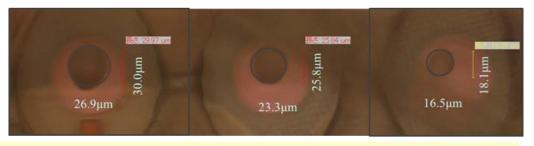

# 3\_(1)\_2) 受光素子

複数PD構造の感度、周波数特性をシミュレーションにより求め 受光径 Φ 20um ~ Φ 25um に設計値を絞り込み TEG\_PDで32Gbps動作を確認後、光I/Oコア集積チップに搭載 周波数特性検証

# 光ピン出射端光強度分布計算例

- 受光素子受光径

- 光ピン製造ばらつき

- ・ 実装位置ずれ

- · MMF入力光強度分布

- Ge吸収層厚

- 受光素子受光径

- ・ キャリア走行時間

- · Ge吸収係数

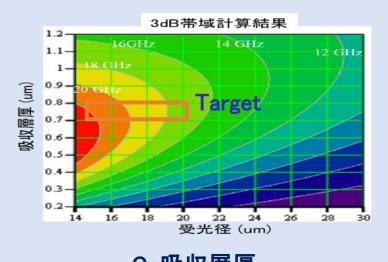

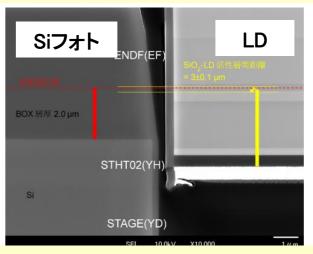

3\_(2)\_1) LD光結合損失の低減 光I/OコアはベアチップLDのパッシブアライメント技術を適用 台座高さ精度とSiフォト導波路端面の面粗度、傾きが結合損に影響 ⇒プロセス条件出しを繰り返し精度を向上

SiO2深掘エッチングとSiリセスエッチング条件出しを行い目標仕様を達成

- SiO<sub>2</sub>エッチング側壁角度:85度以上

- > ウェーハー面内均一な台座エッチング深さ精度<40 nm

- > 実デバイスウェハーでの検証を実施

Alignment mark on LD LD array Electrodes Si alignment mark Si pedestals AuSn solder bump 台座上ずれ量

台座高さ、浮きによる 高さ方向位置ずれ

端面角度、表面あれによる損失増加

目標 高さ精度:<100nm 端面角度:>81°表面粗:<50nm

LD搭載度、突き当て面断面

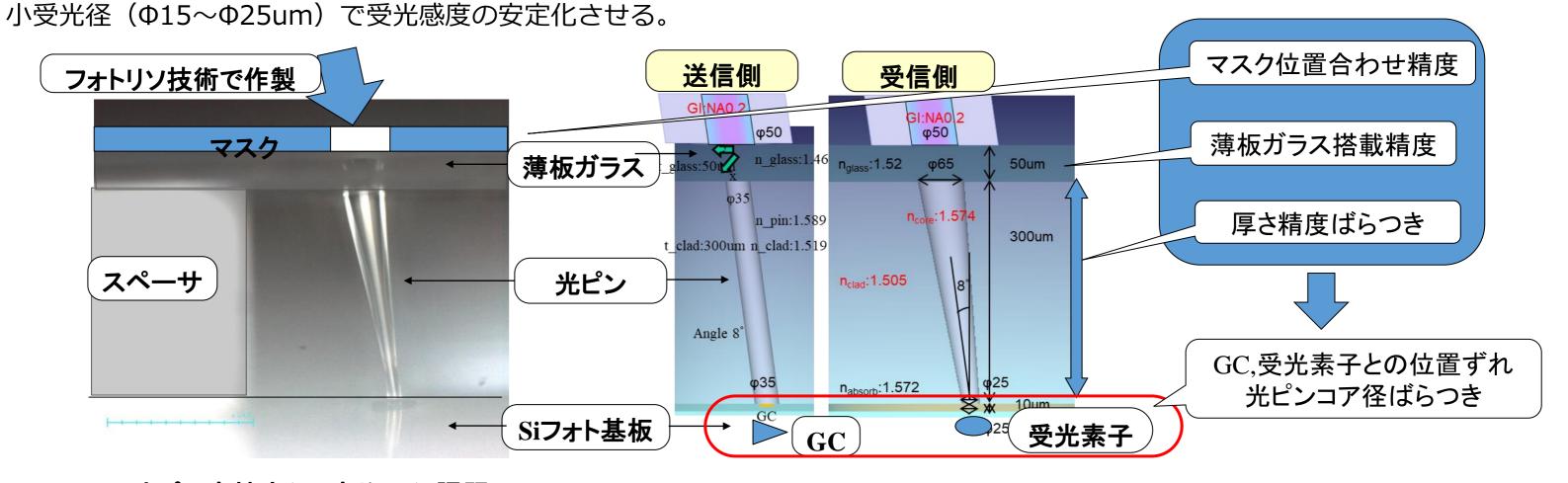

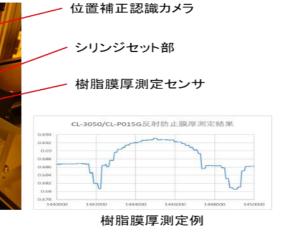

# 3\_(2)\_2) 光ピンの高精度化

光ピンの精度は、マスクの位置合わせ制度だけではなく、周辺部材のスペーサーや薄板ガラスの高さばらつき、傾きの影響を受ける。実装工程の設備の設備の高精度化、自動化を行う事で、光ピンの位置精度、ピン径のばらつきを抑制

### 光ピン高精度化、高均一化課題

- i)光ピン形成用の紫外線硬化樹脂注入位置および高さ、注入量の安定化

- ii)光ピンを形成する薄板ガラスと露光マスクの間隙の均一化

- iii)光ピン現像工程の最適化と安定化

- ▶ 現像液注入→静置→現像液排出をプログラム制御する光ピン形成用自動現像装置を導入

- > エタノール洗浄を最適組合せ条件を求め、現像の過不足によるピン径のばらつきを改善

- > 光ピン細径化及び精度安定化条件導出を継続中。

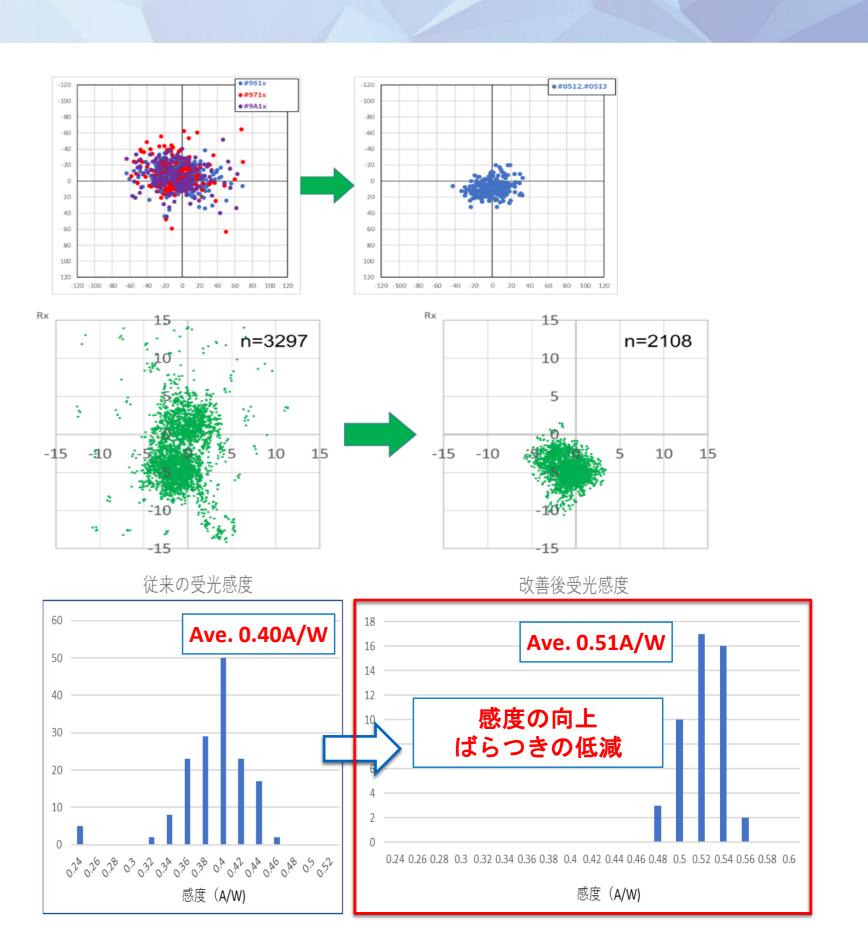

# 3\_(2)\_2) 光ピンの高精度化

光ピン形成に影響する各部材の実装精度を向上し 0.4A/Wから0.5A/Wと受光感度の向上を実現

整列するガラスの XYθz補正が可能な 搬送系を採用

ガラス整列精度向上用 認識光学系を導入

マスクの開口径を小さくし細径化

受光径(15~20 µ m)に適合のコア径作製確認

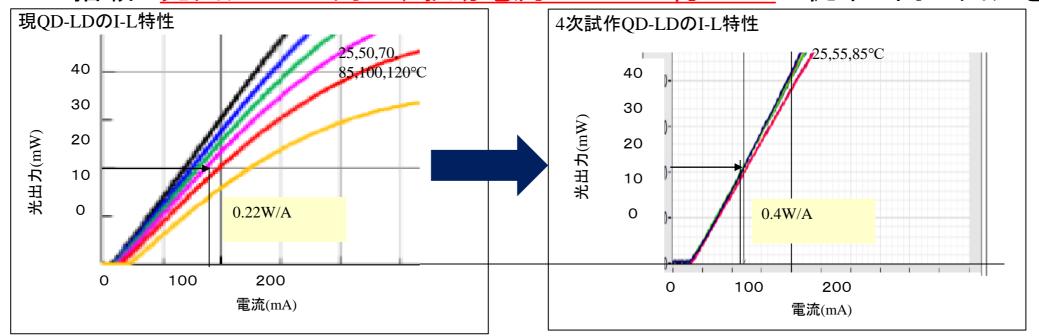

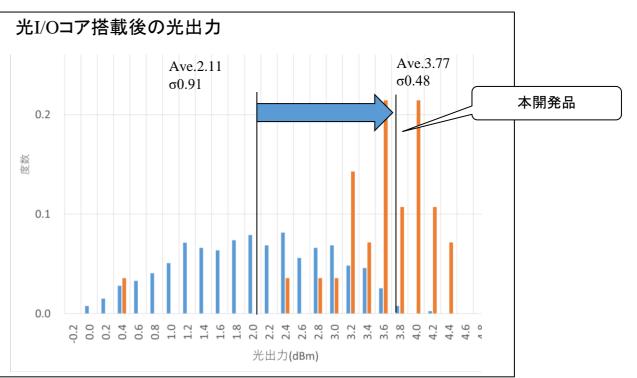

- 3\_(3) 量子ドットレーザーの発光効率の向上

- ・LDの共振器長、コーティング反射率、基板タイプを見直し発光効率を向上&MFDとSSCの最適化で結合効率を低減

- •QD-LDで発光効率0.22W/A⇒0.4W/Aを実現

- ・光I/Oコアチップに搭載し<u>光出力1.6dB向上、駆動電流100mA⇒約60mA</u>で従来と同一出力を確認

### 3\_(3) 総合評価

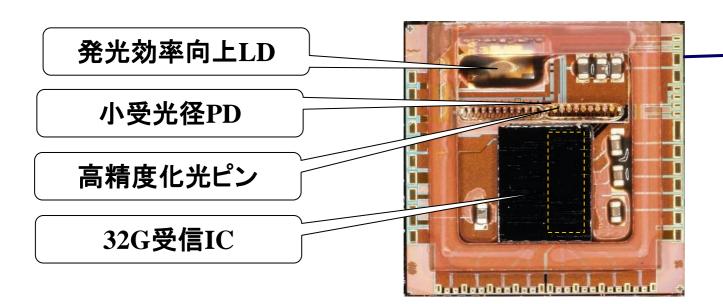

・各施策を取りいれたSiフォトチップ、IC、LDを用い光I/Oコアを試作

モジュール化し特性を評価

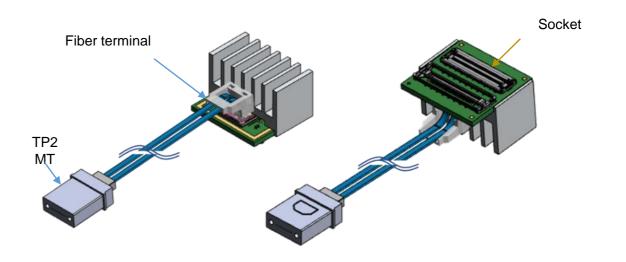

・光I/Oコア

小受光径化PD、高精度化LD台座を形成したSiフォト基板に 開発したIC,LDを搭載、高精度化光ピンを形成

・外観、ピン配置は現行の25Gbps光I/Oコアと同一

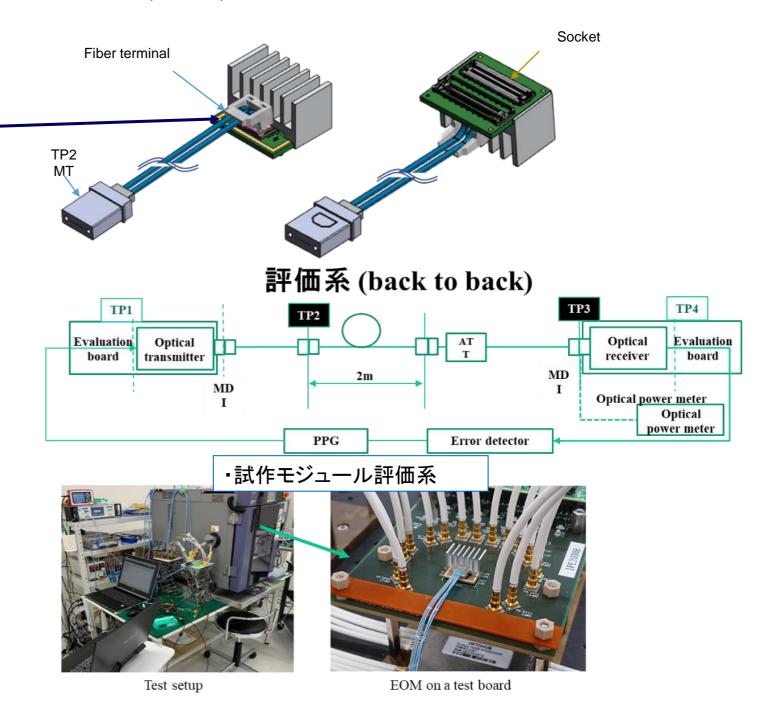

・EOM (Embedded optical module) 光I/Oコアを搭載した光モジュール

### ・モジュール

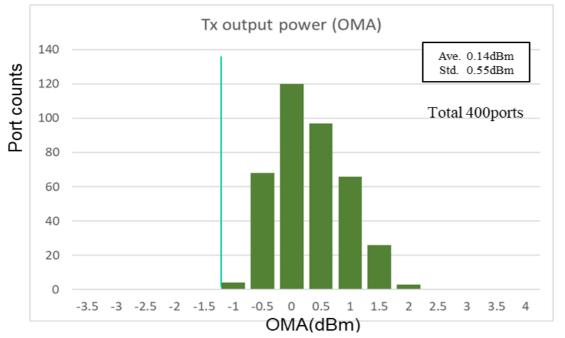

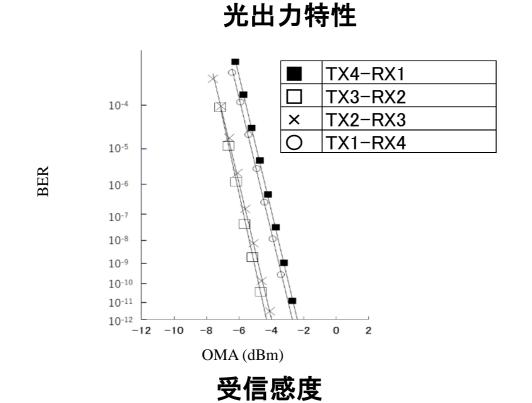

# 3\_(3) 総合評価(2) 評価結果

### ・送受信同時動作において32Gbpsのリンク接続特性を確認 Tx

Ta=105℃

Ta=25℃

•消費電力: 7.8mW/Gbps

# 3-2.今後の展望

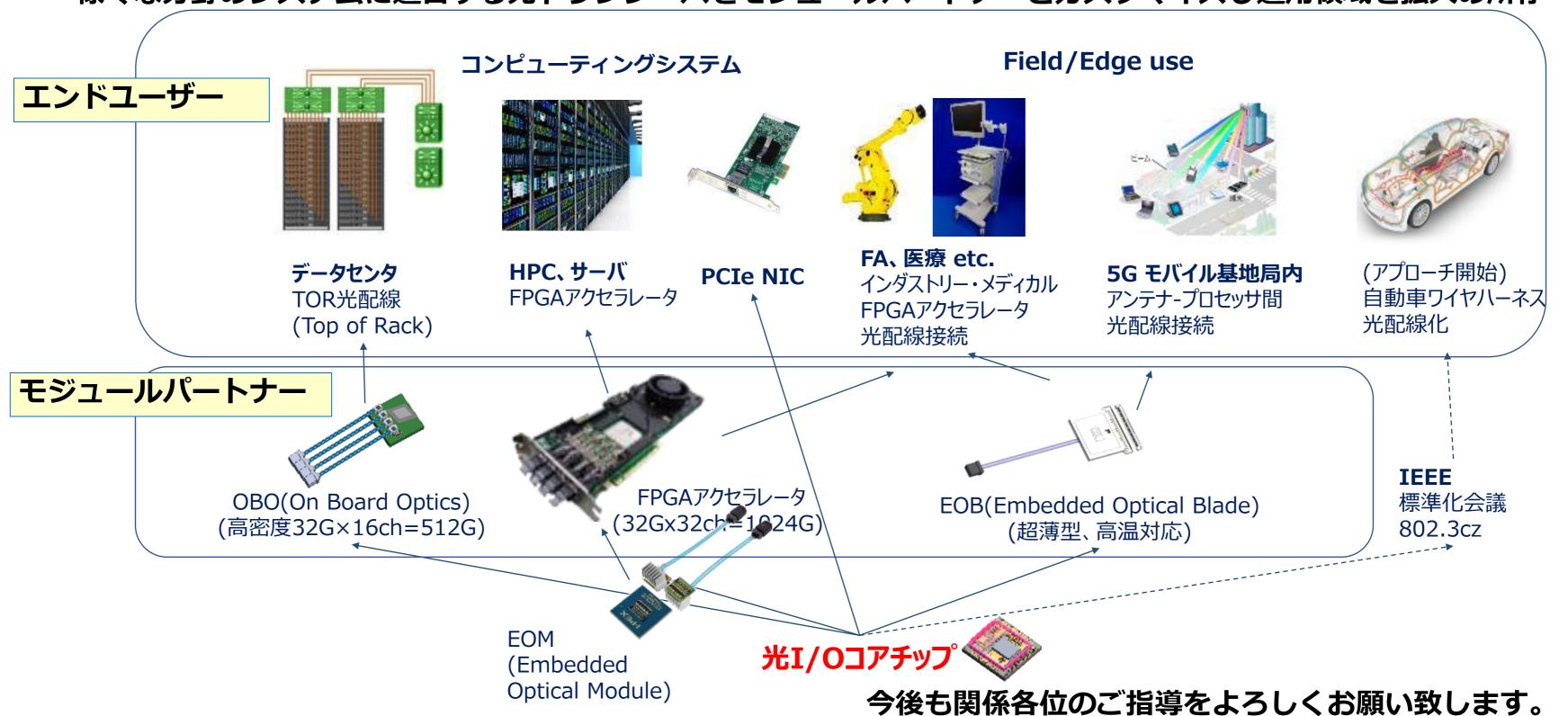

### 3-2 今後の展望:事業動向

コンピュータ系の光インターコネクションに関しての議論が浮上、活発化している 32Gbpsの実際のアプリケーション拡大は2023以降と予想、システム検討、試作は既に始まっている。 光I/Oコアをモジュール化するパートナ企業と共同で拡販を開始 有望な顧客へコンタクト、データ提供、サンプル評価の協議を開始している。

マイクロソフトプレゼン資料より抜粋

# 3-2.今後の展望

# 様々な分野のシステムに適合する光トランシーバをモジュールパートナーとカスタマイズし適用領域を拡大の所存