# 「チップレット設計基盤構築に向けた技術開発事業」 (終了時評価)

2023年度～2024年度 2年間

## プロジェクトの説明 (公開版)

2024年7月16日

国立研究開発法人 新エネルギー・産業技術総合開発機構

半導体・情報インフラ部（旧IoT推進部）

## チップレット設計基盤構築に向けた技術開発事業

IoT推進部

PMgr: 芹澤慎 主査

### プロジェクトの概要

Society 5.0 の実現に向けてデジタル化技術を進展させるために、エッジでの情報処理が不可欠である。情報処理に活用するAI半導体として、高い性能を維持しつつ設計・製造コストの増加を抑制する。ポストムーア技術の一つとしてチップレットと呼ばれる技術への取組が標準化を含め米国を中心に加速しており、日本としても早急な対応が必要になってきている。

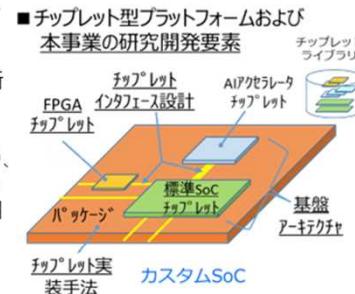

本事業では、世界のチップレット技術の標準化動向を注視しつつ、性能とコストを両立する半導体を容易に実現するためのチップレット設計基盤構築に向けた技術開発を進め、民間企業等が広く活用できる基盤技術となることを目指す。

研究開発項目 チップレット型カスタムSoC設計基盤技術開発

関連する技術戦略: NEDOコンピューティング技術戦略

プロジェクト類型: 基礎的・基礎的研究開発

### 既存プロジェクトとの関係

・NEDO「ポスト5G情報通信システム基盤強化研究開発事業」(2019年度～)

当該プロジェクトでは、「先端半導体製造技術の開発」等を推進しており、本プロジェクトのチップレット設計技術との融合も重要であるため連携してプロジェクトを推進する。

・NEDO「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業」(2021～2025年度)

当該プロジェクトでは「新世代パワー半導体の開発」等を推進しているが、本プロジェクトのチップレット向けにパワー半導体技術との融合も重要であるため連携してプロジェクトを推進する。

### 想定する出口イメージ等

|                  |                                                                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

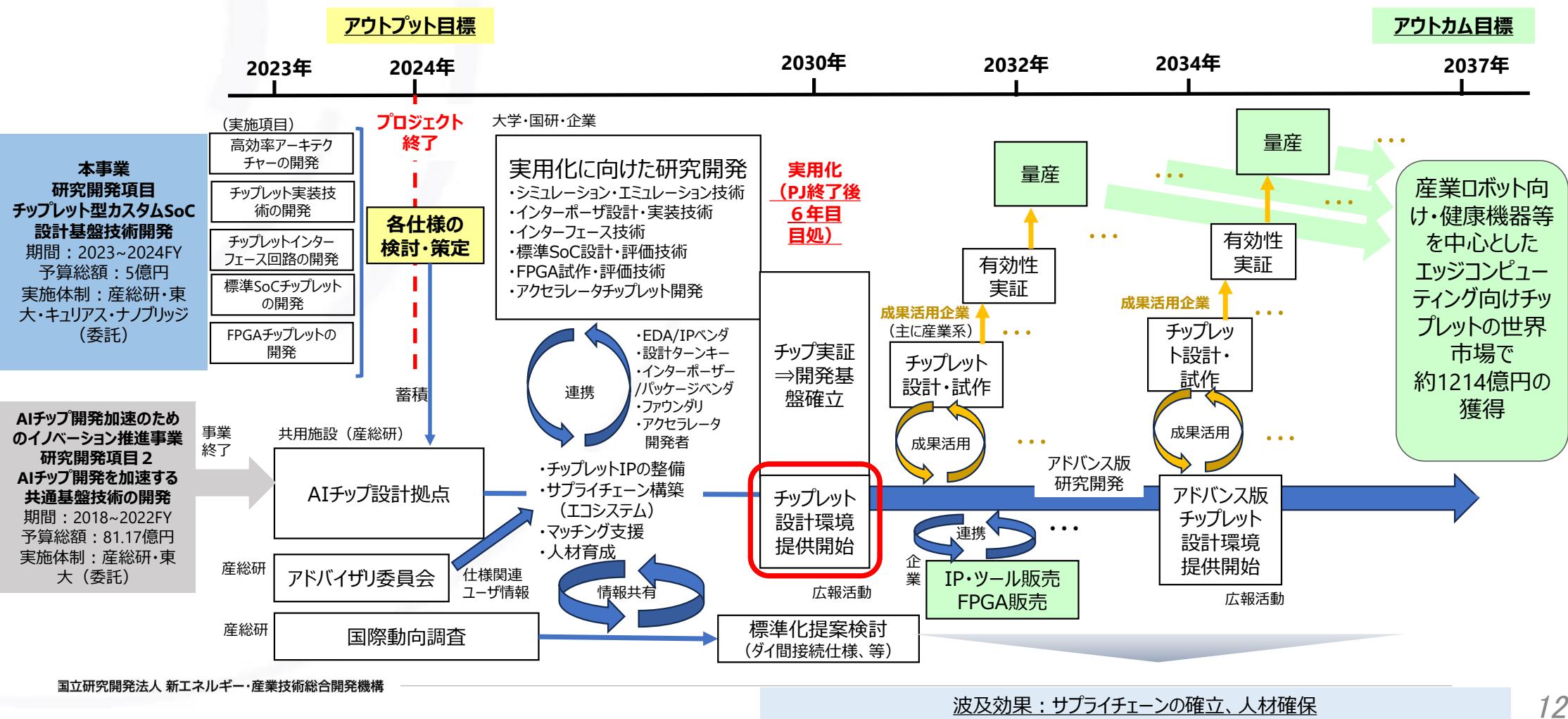

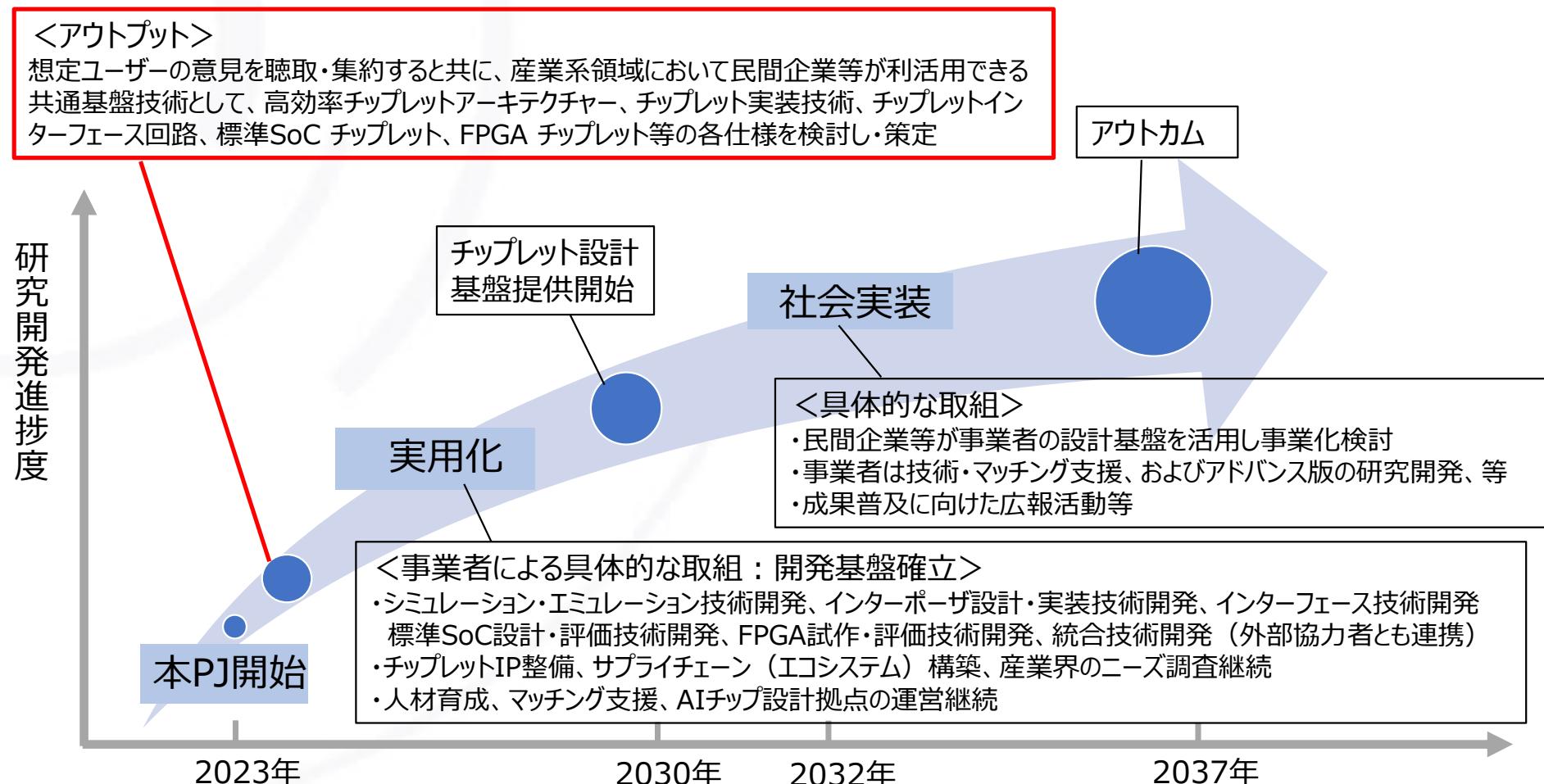

| アウトプット目標         | ・産業系領域において民間企業等が利活用できるチップレット型カスタムSoC設計基盤技術として、想定ユーザーの意見を聴取・集約すると共に、共通基盤技術となる高効率チップレットアーキテクチャ、チップレット実装技術、チップレットインターフェース回路、標準SoCチップレット、FPGAチップレット等の各仕様を検討し策定する。                                                                     |

| アウトカム目標          | 2037年(令和19年)の産業ロボット向け・健康機器等を中心としたエッジコンピューティング向けチップレットの世界市場で約1,214億円の市場獲得を目指す。                                                                                                                                                     |

| 出口戦略<br>(実用化見込み) | ・研究開発項目の事業者は協力者と連携し、民間企業等へ提供できるようチップレット型カスタムSoCの開発基盤を確立する。<br>・国際標準化活動予定: 有 委託者指定データ: 無                                                                                                                                           |

| グローバルポジション       | ・プロジェクト開始時: RA → プロジェクト終了時: RA<br>半導体関連要素技術に関しては、メモリを中心とし論文数・特許出願件数においてシェア平均20%を占めている。エッジ向けAI半導体の実現に資する先端技術を持つベンチャー企業が存在し、新材料の分野で世界をリードする大学、国研や、革新的AI半導体の基盤技術と成り得る要素デバイスの研究実績がある大学、国研が存在する。共通基盤によりこれらを支援し研究を加速する。プロジェクト終了時はRAとした。 |

### 事業計画

期間: 2023～2024年度(2年間)

総事業費(NEDO負担分): 5億円(予定) (委託)

2024年度予算: 0.07億円(一般) ※2023年度繰越予算分

### <研究開発スケジュール・評価時期・想定する予算規模>

|            | 2023 | 2024                                                      |

|------------|------|-----------------------------------------------------------|

| 研究開発<br>項目 |      | チップ<br>レット型<br>カスタム<br>SoC可<br>け設<br>計基<br>盤技<br>術の<br>開発 |

| 評価時期       |      | 終了時<br>評価                                                 |

| 予算<br>(億円) | 4.93 | 0.07                                                      |

# 報告内容

## ページ構成

※本事業の位置づけ・意義

(1)アウトカム達成までの道筋

(2)知的財産・標準化戦略

1. 意義・アウトカム（社会実装）達成までの道筋

(1)アウトカム目標及び達成見込み

(2)アウトプット目標及び達成状況

2. 目標及び達成状況

(1)実施体制

※受益者負担の考え方

(2)研究開発計画

3. マネジメント

- ・事業の背景・目的・将来像

- ・政策・施策における位置づけ

- ・技術戦略上の位置づけ

- ・外部環境の状況（技術、市場、制度、政策動向など）

- ・他事業との関係

- ・アウトカム達成までの道筋

- ・知的財産・標準化：オープン・クローズ戦略

- ・知的財産管理

- ・実用化の考え方と

アウトカム目標の設定及び根拠（事業化は非該当）

- ・アウトカム目標の達成見込み

- ※費用対効果

- ・非連続ナショナルに該当する根拠（非該当）

- ・前身事業との関連性（非該当）

- ・本事業における研究開発項目の位置づけ

- ・アウトプット目標の設定及び根拠

- ・アウトプット目標の達成状況

- ・研究開発成果の副次的成果等

- ・特許出願及び論文発表

- ・NEDOが実施する意義

- ・実施体制

- ・個別事業の採択プロセス

- ・研究データの管理・利活用

- ・予算及び受益者負担

- ・目標達成に必要な要素技術

- ・研究開発のスケジュール

- ・進捗管理

- ・進捗管理：事前/中間評価結果への対応

- ・進捗管理：動向・情勢変化への対応

- ・進捗管理：成果普及への取り組み

- ・進捗管理：開発促進財源投入実績（非該当）

- ・モティベーションを高める仕組み（非該当）

## ＜評価項目 1＞意義・アウトカム（社会実装）達成までの道筋

- ※ 本事業の位置づけ・意義

- (1) アウトカム達成までの道筋

- (2) 知的財産・標準化戦略

# 報告内容

## ページ構成

### 1. 意義・アウトカム（社会実装）達成までの道筋

※本事業の位置づけ・意義

(1)アウトカム達成までの道筋

(2)知的財産・標準化戦略

- ・事業の背景・目的・将来像

- ・政策・施策における位置づけ

- ・技術戦略上の位置づけ

- ・外部環境の状況（技術、市場、制度、政策動向など）

- ・他事業との関係

- ・アウトカム達成までの道筋

- ・知的財産・標準化：オープン・クローズ戦略

- ・知的財産管理

### 2. 目標及び達成状況

(1)アウトカム目標及び達成見込み

(2)アウトプット目標及び達成状況

### 3. マネジメント

(1)実施体制

※受益者負担の考え方

(2)研究開発計画

# 事業の背景・目的・将来像

## ●背景

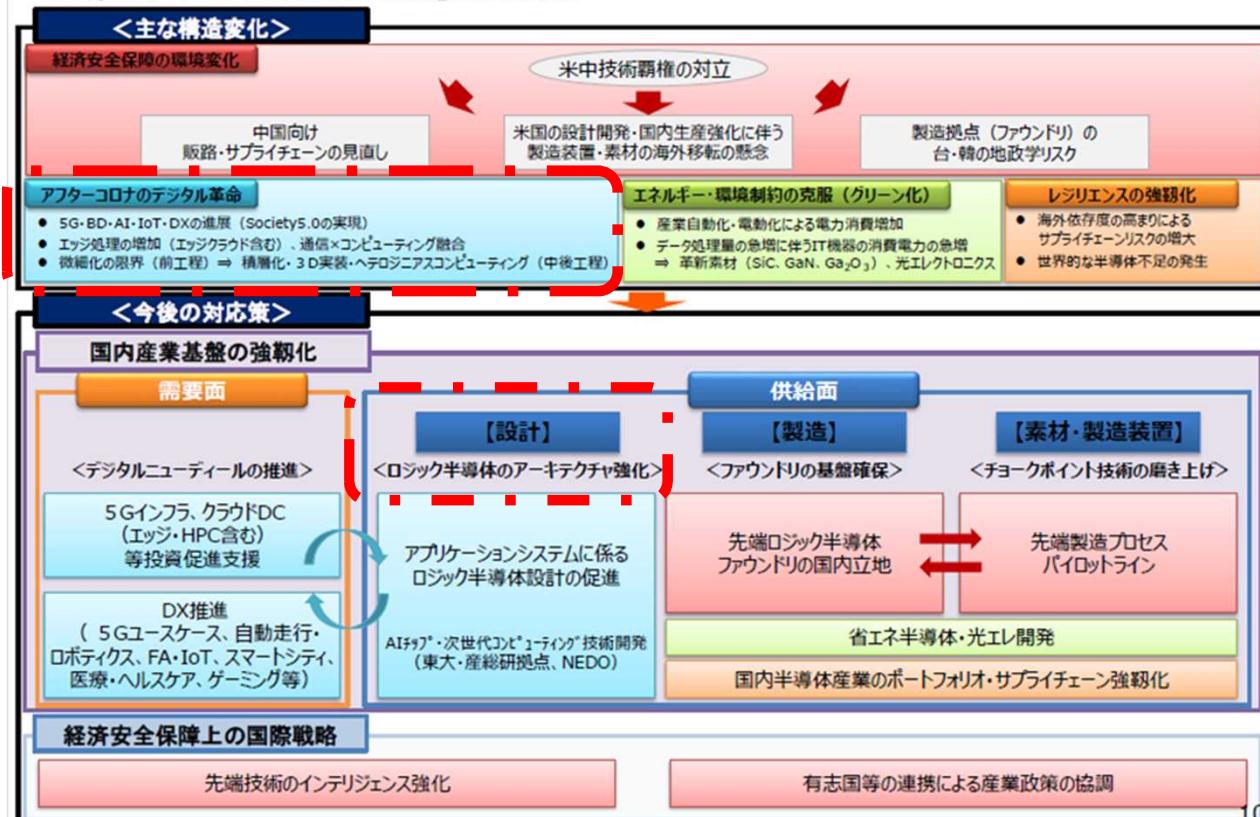

- デジタル化技術の進展によるSociety5.0実現に向け、増大するデータの処理が課題。

- 増大するデータはクラウド領域に加え、エッジ領域での処理も不可欠。エッジ領域の処理はAI技術の活用も期待され、自動走行やロボティックス以外の分野からも注目。

- エッジ領域のデータ処理を行う半導体の高性能化として、更なる微細化は設計・製造コストの上昇が顕著。対応として、チップレット技術への取組が標準化含め米国を中心に加速。

## ●目的・将来像

- 世界のチップレット技術の標準化動向を注視しつつ、性能とコストを両立する半導体を容易に実現するためのチップレット設計基盤構築に向けた技術開発を進め、我が国の民間企業等が広く活用できる基盤技術となることを目指す。

# 政策・施策における位置づけ

## ○統合イノベーション戦略2021（令和3年6月18日閣議決定）

経済安全保障の確保・強化のため、半導体、AI等の先端分野における重要技術について、実用化に向けた強力な支援を行う。（p9）

## ○成長戦略実行計画（令和3年6月18日閣議決定）

半導体、AI等の分野における経済安全保障強化の観点から重要な先端技術について、実用化に向けた強力な支援を行う。（p15）

## ○経済財政運営と改革の基本方針2022（令和4年6月7日閣議決定）

国家・国民の安全を経済面から確保する観点として、「先端半導体基盤の拡充」、「次世代半導体の設計」等の確立（p23）

## ○第6期科学技術・イノベーション基本計画（令和3年3月26日閣議決定）

次世代社会インフラ実現として、半導体等の研究開発に取り組む。（p22）

## ○デジタル社会の実現に向けた重点計画（令和4年6月7日閣議決定）

情報処理の高度化のための次世代コンピューティングとして、「AI半導体」や「チップレット」等の技術開発に取り組む。（p122）

# 技術戦略上の位置づけ

## ●NEDOコンピューティング技術戦略に記載されるチップレット設計基盤技術の開発

実現への道筋

### 3. 4 半導体に関する既存の取り組みとプロジェクトイメージ

TSC Digital Innovation Unit

#### ■ 半導体デバイス技術開発予算のポートフォリオとの対比

委託事業

助成事業

今後必要なプロジェクト

| 項目    |    | 課題                                            | ニーズ                          | 既存プロジェクト・取り組み                                                                                                                          |

|-------|----|-----------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| AIチップ | 設計 | AIアルゴリズムの玉成とハードウェア化（GPUに代わってハードウェアロジックでAIを実装） | モビリティ、製造・FA、物流、ヘルスケア、スマートフォン | <p>NEDO「AIチップ開発加速のためのイノベーション推進事業」</p> <p>AIチップに関するアイディア実用化に向けた開発</p> <p>AIチップ開発を加速する共通基盤技術の開発</p> <p>AIエッジコンピューティングの産業応用加速のための技術開発</p> |

|       |    | Beyond CMOS                                   | 同上およびデータセンター                 | <p>「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発」</p> <p>次世代コンピューティングの技術開発（量子、ニューロモルフィック、光等）</p>                                              |

| ロジック  | 設計 | DTCO、STCO等の最適化設計技術                            | データセンター、スマートフォン              | <p>「GI基金事業/次世代デジタルインフラの構築/次世代データセンター」</p> <p>次世代グリーンデータセンタ技術開発</p> <p>光に適合したチップ等の高性能化・省エネ化技術の開発</p>                                    |

|       |    | Beyond 2nm (CFETなど)                           |                              | <p>「ポスト5G情報通信システム基盤強化研究開発事業」</p> <p>先端半導体の前工程技術の開発</p>                                                                                 |

|       |    | (装置) ナノインプリント                                 |                              | <p>DNPで実用化</p> <p>ナノインプリントリソグラフィの改善</p>                                                                                                |

| 後工程   |    | パッケージング、チップレット実装                              |                              | <p>「ポスト5G情報通信システム基盤強化研究開発事業」</p> <p>先端半導体の後工程技術の開発：</p> <p>高性能コンピューティング向け実装技術、エッジコンピューティング向け実装技術、実装共通基盤技術</p>                          |

|       |    | (装置)                                          |                              |                                                                                                                                        |

| 製造能力  |    | 国内製造能力の強化                                     |                              | 「特定半導体基金事業」先端半導体の国内生産拠点の確保                                                                                                             |

# 外部環境の状況（技術、市場、制度、政策動向など）

## 我が国半導体産業を巡る全体像

経済産業省 半導体戦略（概略、2021年6月）より抜粋

国立研究開発法人 新エネルギー・産業技術総合開発機構

## 米国政策の動向

- DARPAがエレクトロニクス再生イニシアチブを2018年に立ち上げ（予算規模15億ドル）

- 複数のダイによってチップを構成する、Common Heterogeneous Integration and IP Reuse Strategies (CHIPS) プログラム等を推進

参照元：DARPA ERI Summit 2018

## チップ間接続の規格を推進する団体の設立

- 米国半導体大手、ファウンドリ、クラウドプロバイダ企業が半導体チップ間接続のための規格 Universal Chiplet Interconnect Express (UCIE) を推進する団体を2022年3月に設立。標準仕様を発表。

- 設立時の参加企業10社

(ASE, AMD, Arm, Google, Intel, Meta, Microsoft, Qualcomm, Samsung, TSMC)

- 2024年4月時点で120社以上参加

参照元：同団体HP<<https://www.uciexpress.org/>>

# 他事業との関係

| 実施機関   | 事業名／研究開発項目                                                                                             | 期間         | 概要                                                                                                       |

|--------|--------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------|

| 1 NEDO | ポスト5G情報通信システム基盤強化研究開発事業／<br>①ポスト5G情報通信システムの開発<br>(d1) MEC向け大規模先端ロジックチップ設計技術の開発<br>MEC：モバイルエッジコンピューティング | 2021年～     | 先端ロジック世代のAI処理可能なSoC設計技術、スケーラブルなマルチチップシステムを実現するための設計技術等を開発する。                                             |

| 2 NEDO | ポスト5G情報通信システム基盤強化研究開発事業／<br>②先端半導体製造技術の開発<br>(f1) 2nm世代半導体チップ設計技術開発                                    | 2024年～     | 2nm以細を狙う次世代半導体設計技術として、生成AIを含むエッジ推論処理用途に専用化したエッジAIアクセラレータを開発する。                                           |

| 3 NEDO | ポスト5G情報通信システム基盤強化研究開発事業／<br>②先端半導体製造技術の開発<br>(f2) 自動車用高性能コンピュータ向け最先端SoC技術開発                            | 2024年～     | 車載課題を解決するチップレットの要素技術を確立する。                                                                               |

| 4 NEDO | ポスト5G情報通信システム基盤強化研究開発事業／<br>②先端半導体製造技術の開発<br>(d4) 2nm世代半導体のチップレット・パッケージング設計・製造技術開発                     | 2024年～     | 先端半導体の製造技術を開発する。                                                                                         |

| 5 NEDO | チップレット設計基盤構築に向けた技術開発事業／<br>チップレット型カスタムSoC設計基盤技術開発                                                      | 2023～2024年 | 世界のチップレット技術の標準化動向を注視しつつ、性能とコストを両立する半導体を容易に実現するためのチップレット設計基盤構築に向けた技術開発を進め、我が国の民間企業等が広く活用できる基盤技術となることを目指す。 |

# 国内外のチップレット開発状況

## 国内

- (1) MEC向け大規模先端ロジックチップ設計技術の開発(ポスト5Gプロジェクト、2021年～)

- ・先端ロジック世代のAI処理可能なSoC設計技術、スケーラブルなマルチチップシステムを実現するための設計技術等を開発

- (2) 2nm世代半導体チップ設計技術開発 (ポスト5Gプロジェクト、2024年～)

- ・2nm世代半導体技術によるエッジAIアクセラレータの開発

- (3) 自動車用高性能コンピュータ向け最先端SoC技術開発(ポスト5Gプロジェクト、2024年～)

- ・車載課題を解決するチップレットの要素技術を確立

- (4) 2nm世代半導体のチップレット・パッケージング設計・製造技術開発(ポスト5Gプロジェクト、2024年～)

- ・先端半導体の製造技術の開発

## 海外

- (1) 民間企業

- ・AMD(US) : CPUチップレット(5nm)、IOチップレット(6nm)を用いてサーバ製品展開 (2022年～)

- ・Intel(US) : CPUチップレット(4nm)、SoCチップレット(6nm)を用いてPC製品展開 (2023年～)

- ・ベンチャ : Tenstorrent(US)、Ventana(US)、Esperanto(US)、BlueCheetah(US)、DreamBiG(US)、Zero ASIC(US)等、チップレット製品・プラットフォーム計画 (2023年～)

- (2) 大学、コンソーシアム等

- ・スタンフォード大 : チップレットプラットフォーム(標準SoC + カスタム)構想 (2022年～)

- ・UCIeコンソーシアム : 仕様の改訂版 UCIe Rev 1.1公開 (2023年8月)

各WGでAuto、テスト、管理、セキュリティの拡充を中心にRev 2.0を策定中2023年7月～)

## アウトカム達成までの道筋

# 知的財産・標準化戦略

- 我が国の民間企業等が活用できるよう、チップレット設計に必須の共通技術や設計環境は原則公開

- ダイ間接続に係る共通技術はUCIEコンソーシアム内の活動継続、接続仕様に関する標準化活動・設計反映に貢献

- 想定ユーザの要求仕様等は非公開情報として継続して秘匿・更新し、設計技術にも反映

- 今後、設計ガイドラインを作成し公開。チップレット型カスタムSoC設計プラットフォームを利用可能とする。(2030年目途)

|     |                                                                                  |                                                                                                                                                                                                                                                                                             |

|-----|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 公開  | ダイ間接続に係る共通技術<br>→標準化推進団体UCIEコンソーシアムに参加し、各WG活動を通じて標準化推進に貢献するとともに、仕様の整合検証、早期実装を行う。 | <ul style="list-style-type: none"> <li>チップレット設計手法</li> <li>IPライブラリリスト</li> <li>設計クラウド</li> <li>設計ガイドライン</li> </ul> <p>利用許諾後に公開（今後蓄積）<br/>IPライブラリ<br/>有料で公開（今後蓄積予定）<br/> <ul style="list-style-type: none"> <li>RTLガイドライン</li> <li>実装に係る技術</li> <li>チップレット設計プラットフォーム（2030年～）</li> </ul> </p> |

|     | 上記の標準や論文のエビデンスとなるデータ等（標準化等の過程において公開を必要とされなかったもの）                                 | <ul style="list-style-type: none"> <li>標準SoC内部回路・レイアウト</li> <li>FPGA内部回路・レイアウト</li> <li>想定ユーザの要求仕様情報</li> <li>その他分解しても解明不能な技術領域<br/>→秘匿</li> </ul>                                                                                                                                          |

| 非公開 | 非競争域                                                                             | 競争域                                                                                                                                                                                                                                                                                         |

## 事業者の戦略

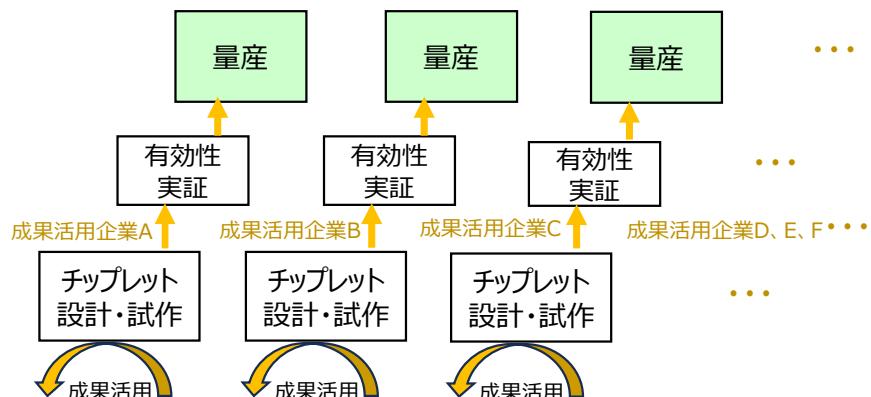

## 民間企業等による事業成果活用

## 知的財産管理

### ➤ 知的財産権の帰属

産業技術力強化法第17条第1項に規定する4項目及びNEDOが実施する知的財産権の状況調査（バイ・ドール調査）に対する回答を条件として、知的財産権はすべて発明等をなした機関に帰属する

### ➤ 知財マネジメント基本方針（「NEDO知財方針」）に関する事項

本事業は、「NEDOプロジェクトにおける知財マネジメント基本方針」を適用する

### ➤ データマネジメントに係る基本方針（NEDOデータ方針）に関する事項

本事業は、「NEDOプロジェクトにおけるデータマネジメントに係る基本方針（委託者指定データを指定しない場合）」を適用する

## ＜評価項目2＞目標及び達成状況

- (1) アウトカム目標及び達成見込み

- (2) アウトプット目標及び達成状況

# 報告内容

ページ構成

## 1. 意義・アウトカム（社会実装）達成までの道筋

※本事業の位置づけ・意義

(1)アウトカム達成までの道筋

(2)知的財産・標準化戦略

## 2. 目標及び達成状況

(1)アウトカム目標及び達成見込み

(2)アウトプット目標及び達成状況

- ・実用化の考え方と

アウトカム目標の設定及び根拠（事業化は非該当）

- ・アウトカム目標の達成見込み

- ※費用対効果

- ・非連続ナショブロに該当する根拠（非該当）

- ・前身事業との関連性（非該当）

- ・本事業における研究開発項目の位置づけ

- ・アウトプット目標の設定及び根拠

- ・アウトプット目標の達成状況

- ・研究開発成果の副次的成果等

- ・特許出願及び論文発表

## 3. マネジメント

(1)実施体制

※受益者負担の考え方

(2)研究開発計画

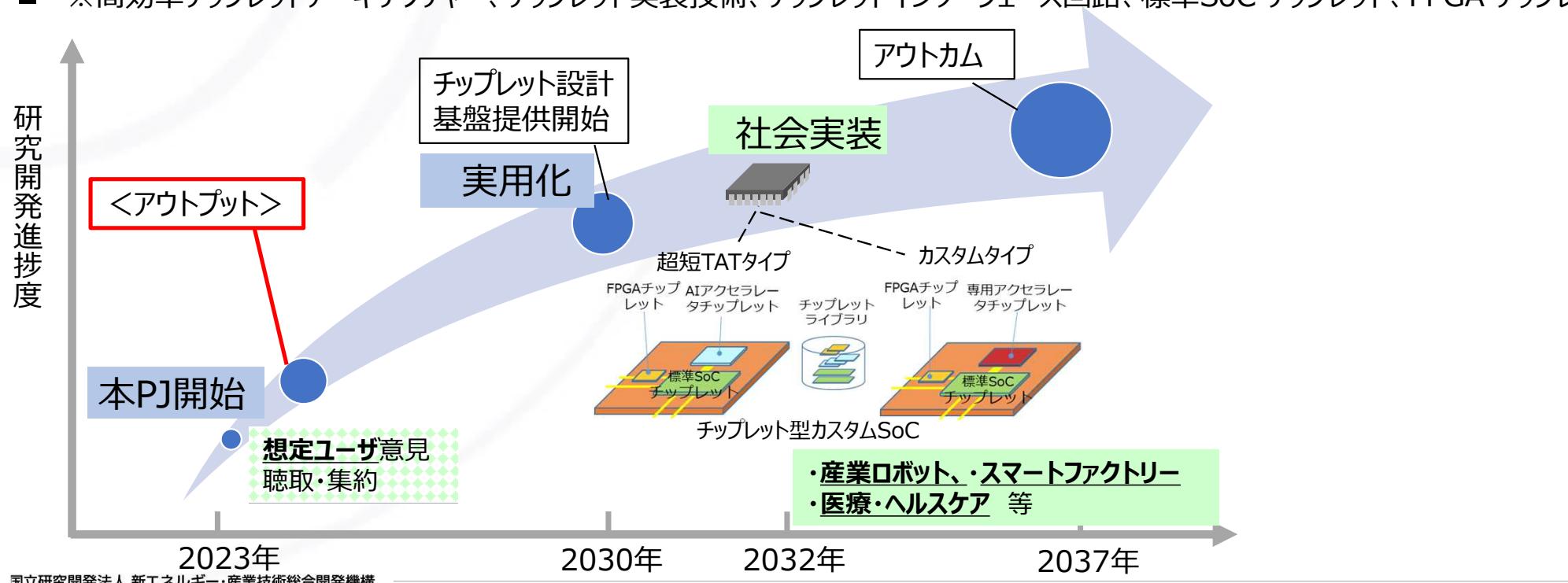

# 実用化の考え方とアウトカム目標の設定及び根拠

| アウトカム目標                                                              | 根拠                                                               |

|----------------------------------------------------------------------|------------------------------------------------------------------|

| 2037年の産業ロボット向け・健<br>康機器等を中心としたエッジコン<br>ピューティング向けチップレットで約<br>1,214 億円 | 社会実装開始～2037年の世<br>界市場規模23.48兆円※1×本<br>プロジェクトが寄与するシェア<br>0.517%※2 |

※1 出所： Transparency Market Research社 チップレット市場-調査報告書(2021/8) の[Industrial Automation],[Healthcare],[Others]の2031年市場予測値および同年までのCAGRを参考に2032～2037年CAGR30%で外挿し、為替レート135JP¥/US\$で算出

※2 国内半導体市場占有率（10%）×当該ノード半導体の世界大手の売上比率（11%）※※

×日本企業のオープンイノベーションの実施率（47%）※※※から算出

※※※出所：TSMC社資料

※※※出所：米山(2017)「日米欧企業におけるオープン・イノベーション活動の比較研究」

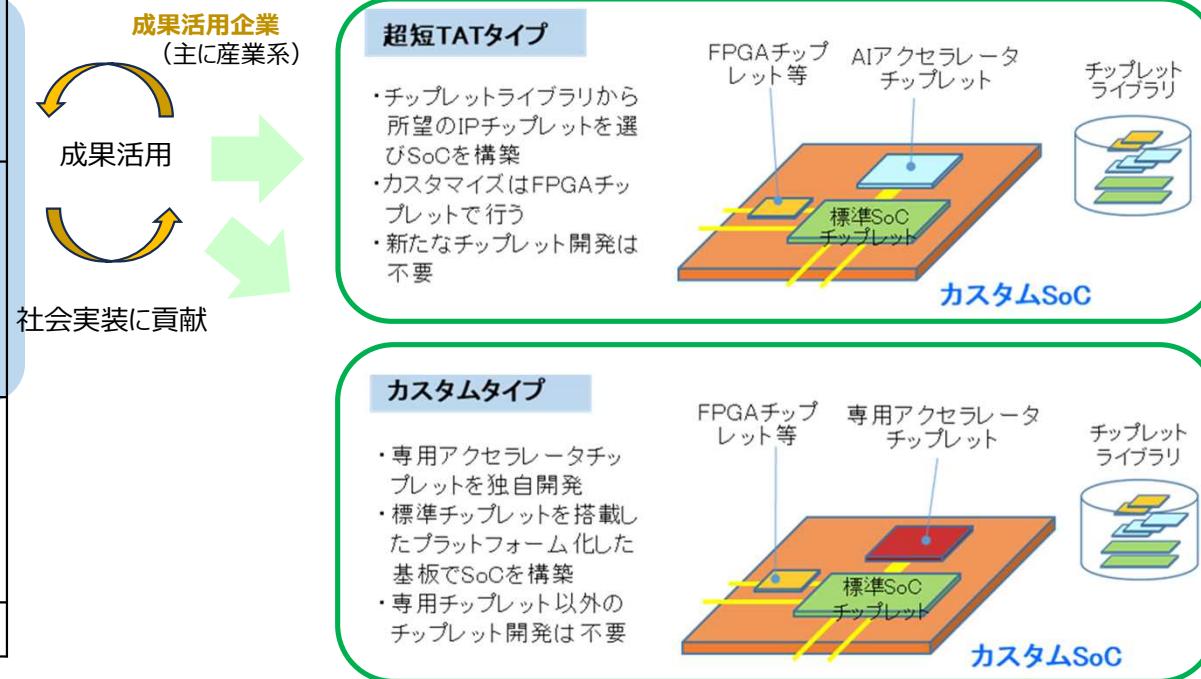

## 社会実装（実用化から数年後）

### 民間企業等によるチップレット設計環境の活用

産業系用途等に向けたチップレット設計→有効性実証→量産・市場投入

AIチップ設計拠点が構築したエコシステム（EDA・IPベンダ、設計ターンキー、ファ

ウンダリ、OSAT等）やマッチングも活用

### 実用化

#### チップレット設計環境の民間企業等への提供（2030年～）

IP、インターポーラ設計・実装技術、インターフェース技術、標準SoC設計・評価

技術、FPGA評価技術、シミュレーション・エミュレーション技術

# アウトカム目標の達成見込み

- 本プロジェクトの成果である、想定ユーザの意見や有用性等を考慮した共通基盤技術※を発展させ、エコシステム構築を含めた開発基盤を確立し、我が国の中小企業等にチップレット設計環境を提供することにより、2037年の産業ロボット向け・健康機器等を中心としたエッジコンピューティング向けチップレットの世界市場で約1,214 億円の市場獲得を見込む

- ※高効率チップレットアーキテクチャー、チップレット実装技術、チップレットインターフェース回路、標準SoC チップレット、FPGA チップレット

# 費用対効果

## ● 本プロジェクト費用の総額

4.76億円（2023～2024※年度）※2023年度繰越予算分

## ● 経済効果

産業ロボット向け・健康機器等を中心としたエッジコンピューティング向けチップレットで

約1,214 億円の売上予測※※（2032年～2037年の累積）

|       | (2032年) | (2033年) | (2034年) | (2035年) | (2036年) | (2037年) |

|-------|---------|---------|---------|---------|---------|---------|

| 年間売上額 | 95億円    | 124億円   | 161億円   | 209億円   | 272億円   | 353億円   |

| 累積売上額 | 95億円    | 219億円   | 380億円   | 589億円   | 861億円   | 1214億円  |

※※売上予測に関するイメージ

2030年：本研究開発成果を基にチップレット設計開発基盤確立。開発環境の提供開始、民間企業等の活用開始。

2032年：本事業を活用した民間企業のチップレット量産（売上）開始

売上額はチップレット世界市場規模※1×本プロジェクトが寄与するシェア※2から予測

（※1および※2の出所はスライド17に記載）

# 本プロジェクトにおける研究開発項目の位置づけ

## アウトプット（終了時）目標の設定及び根拠

| 研究開発項目                  | 最終目標（2024年6月）                                                                                                                                                | 根拠                                  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| チップレット型カスタムSoC 設計基盤技術開発 | 産業系領域において民間企業等が利活用できるチップレット型カスタムSoC設計基盤技術として、想定ユーザの意見を聴取・集約すると共に、共通基盤技術となる高効率チップレットアーキテクチャー、チップレット実装技術、チップレットインターフェース回路、標準SoCチップレット、FPGAチップレット等の各仕様を検討し策定する。 | 産業界の具体的ニーズをとらえ、共通基盤技術に係る仕様を明確にするため。 |

研究開発期間の変更による

アウトプット目標の見直し（2024年2月）

| 研究開発項目                  | 最終目標（2027年度末）                                                           | 根拠                              |

|-------------------------|-------------------------------------------------------------------------|---------------------------------|

| チップレット型カスタムSoC 設計基盤技術開発 | エッジコンピューティング向けチップレット型カスタムSoC の設計基盤技術を開発し、基盤技術を活用したチップレット開発件数8件以上を目標とする。 | 共通基盤技術として整備し、我が国の民間企業等が利活用するため。 |

## アウトプット目標の達成状況

| 研究開発項目                   | 目標<br>(2024年6月末頃)                                                                                                                                              | 成果(実績)<br>(2024年6月末)                                                                                                                                           | 達成度<br>(*) | 達成の根拠     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| チップレット型カスタム SoC 設計基盤技術開発 | 産業系領域において民間企業等が利活用できるチップレット型カスタムSoC設計基盤技術として、想定ユーザの意見を聴取・集約すると共に、共通基盤技術となる高効率チップレットアーキテクチャー、チップレット実装技術、チップレットインターフェース回路、標準SoC チップレット、FPGA チップレット等の各仕様を検討し策定する。 | 産業系領域において民間企業等が利活用できるチップレット型カスタムSoC設計基盤技術として、想定ユーザの意見を聴取・集約すると共に、共通基盤技術となる高効率チップレットアーキテクチャー、チップレット実装技術、チップレットインターフェース回路、標準SoC チップレット、FPGA チップレット等の各仕様を検討し策定した。 | ○          | 目標通り達成のため |

◎ 大きく上回って達成、○達成、△一部未達、×未達

成果の詳細は資料 6 で報告いたします。

## 各実施項目ごとの目標と根拠

| 実施項目                    | プロジェクト中の最終目標                                                                                                                                                                                                                                             | 根拠                                                                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. 高効率チップレットアーキテクチャーの開発 | <ul style="list-style-type: none"> <li>想定ユーザや有識者から意見聴取を行い、標準SoCのアーキテクチャー、チップレットピン数、インターポーラメタライズ位置、バンプ位置のドラフト版を策定する。</li> <li>UCIeにおける作業部会での活動を行い、情報収集・技術提案の活動に努める。</li> </ul>                                                                            | <ul style="list-style-type: none"> <li>多数の想定ユーザのニーズを包含する仕様とし、エコシステムをより汎用性の高いものに仕上げるため。</li> <li>UCIeとの互換性を確保し、多数の接続選択肢を担保するため。</li> </ul>                                                                           |

| 2. チップレット実装技術の開発        | 5μm級微細配線、100~130μmの微細バンプ接続、およびUCIe標準インターフェースとLVDS準拠インターフェースを有するチップレット実装可能なインターポーラの設計仕様を検討する。                                                                                                                                                             | エッジ用途のマルチチップ実装技術開発を目的に、UCIeやLVDSでのチップレット接続を前提とした、より微細な配線やバンプ構造を持つ次世代インターポーラ基板設計仕様策定の必要があるため。                                                                                                                        |

| 3. チップレットインターフェース回路の開発  | <ul style="list-style-type: none"> <li>UCIe 標準パッケージ準拠のインターフェース回路（物理層）のアナログの基本設計を行い、アーキテクチャーを検討する。</li> <li>UCIe標準パッケージ準拠のインターフェース回路（物理層）のデジタル部のアーキテクチャーを検討する。</li> <li>ESD保護セルを使用したインターフェース回路の設計環境を整備し、評価用回路設計とレイアウトを進め初期検討を完了させる。</li> </ul>            | <ul style="list-style-type: none"> <li>エッジ用途に適したコスト・性能を両立する、アナログおよびデジタル部のUCIe準拠のチップレットインターフェースを提供するため。特に、プロジェクト開始時に選定した28nmテクノロジーにおいては、独自のIPを作成する必要があるため。</li> <li>また、UCIe規格に準拠するESD保護セルを独自に開発する必要があるため。</li> </ul> |

| 4. 標準SoCチップレットの開発       | <ul style="list-style-type: none"> <li>実施項目 3 の成果を標準SoC チップレットにインテグレーションするにあたり、ガイドラインを策定する。</li> <li>標準SoC チップレットの仕様案を検討する。</li> </ul>                                                                                                                   | <ul style="list-style-type: none"> <li>実施項目 3 における成果物を各チップレットに搭載するに際し、仕様の適合性を設計当初から確保する必要があるため。</li> <li>実施項目 1 と連携し、多数の想定ユーザのニーズを包含する標準SoCチップレットの構築が必要となるため。</li> </ul>                                            |

| 5. FPGAチップレットの開発        | <ul style="list-style-type: none"> <li>テクノロジーノード28nmで差動I/OであるLVDSの回路設計および物理設計を実施する。各I/Oを搭載したテストチップを評価回路の回路設計および物理設計を実施する。物理設計にあたり、電源線でのノイズや信号間のクロストークを低減するよう配慮する。伝送速度の設計目標値は差動I/Oが600Mbps、シングルエンドI/Oは125MHzである。</li> <li>FPGAチップレットの有用性を確認する。</li> </ul> | <ul style="list-style-type: none"> <li>標準SoCとFPGAチップレットの接続界面において、実際に低レイテンシなI/Fが実施項目 2 のインターポーラ上で実現できることを検証するため。</li> <li>FPGAの市場性をしっかりと勘案し、実際の社会実装を確かなものとするため。</li> </ul>                                           |

# 各実施項目ごとの目標達成状況

◎ 大きく上回って達成、○達成、△一部未達、×未達

| 実施項目                     | プロジェクト中の成果                                                                                                                                                                                                                                                         | 達成度 | 根拠                                                                                                                                                                 |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. 高効率チッププレットアーキテクチャーの開発 | <ul style="list-style-type: none"> <li>想定ユーザや有識者から意見聴取を行い、標準SoCのアーキテクチャー、チップレットピン数、インターポーラメタライズ位置、バンプ位置のドラフト版を策定した。</li> <li>UCIeにおける作業部会での情報収集・技術提案の活動に努めた。</li> </ul>                                                                                            | ○   | <ul style="list-style-type: none"> <li>通算23社分の聞き取り結果から数値仕様・定性的仕様を抽出し、実施項目2～5とともに仕様を決定できた。</li> <li>仕様内容は実施項目4で具体化した。</li> </ul>                                    |

| 2. チップレット実装技術の開発         | <ul style="list-style-type: none"> <li>5μm級微細配線、110μmの微細バンプ接続、UCIe標準IFとLVDS準拠IFを有するチップレット実装可能なインターポーラの設計仕様の検討を完了し、実現可能な見通しを得た。</li> </ul>                                                                                                                          | ○   | <ul style="list-style-type: none"> <li>インターポーラ基板の構造パラメータの仕様策定を行い、数値解析によるチップ間通信の実現性を得た。</li> </ul>                                                                  |

| 3. チップレットインターフェース回路の開発   | <ul style="list-style-type: none"> <li>標準パッケージ準拠UCIeの物理層のアナログ部の基本設計を実施しTSMC28nmプロセスに適したアーキテクチャー検討を終了した。</li> <li>標準パッケージ準拠UCIeの物理層のデジタル部の必要機能を列挙してブロック仕様を検討した。</li> <li>産総研におけるアナログ設計の環境を立ち上げるとともに、評価用回路設計とレイアウトを進め、初期検討（ESDダイオード容量やレイアウトサイズの見積り）を終了した。</li> </ul> | ○   | <ul style="list-style-type: none"> <li>標準パッケージ準拠UCIeの物理層のアナログ部の基本設計を実施しTSMC28nmプロセスに適したアーキテクチャー検討を終了した。物理層デジタルの必要機能を列挙してブロック仕様を策定した。</li> </ul>                    |

| 4. 標準SoCチップレットの開発        | <ul style="list-style-type: none"> <li>実施項目3の成果をインテグレーションするにあたり、そのガイドラインを策定した。</li> <li>標準SoCチップレットの仕様案を策定した。</li> </ul>                                                                                                                                           | ○   | <ul style="list-style-type: none"> <li>各チップレットにIPを搭載するのに十分なガイドラインが得られた。</li> <li>ピン数、メタライズ位置、インターフェースリスト・各仕様、CPU性能等の決定を終了した。</li> <li>実施項目1の検討内容と齟齬はない。</li> </ul> |

| 5. FPGAチップレットの開発         | <ul style="list-style-type: none"> <li>テクノロジーノード28nmで差動I/OであるLVDSの回路設計および物理設計を行うとともに、各I/Oを搭載したテスト回路設計および物理設計を行った。物理設計後に抽出した寄生成分を考慮したシミュレーションを実施し、LVDS：600Mbps、GPIO：125MHzの伝送が問題なく行えることが分かった。</li> <li>ナノブリッジFPGAチップレットの有用性を確認し、LVDSおよびGPIOの仕様の策定を行った。</li> </ul>   | ○   | <ul style="list-style-type: none"> <li>目標記載の各種設計を完了するとともに、レイアウト後の寄生容量抽出・シミュレーションにおいて目標性能を達成した。</li> <li>実施項目1とともに検討し、ユーザ聞き取り結果等からFPGAチップレットの有用性を確認した。</li> </ul>   |

## 研究開発活動の副次的成果

- 半導体設計者向けに月次でフォーラムを開催

平均200名以上の参加

- ・チップレット含め、LSI設計やAIチップに関する最新情報※を共有・参加者によるオープンな議論

- ・関係する研究者・技術者の交流を深化

※ベースは公開情報

### AIチップ設計拠点フォーラム（第50回、2023/8/25）

13:30-13:35 AIチップ設計拠点フォーラムについて

(産総研・内山邦男)

13:35-14:35 半導体パッケージの3D化とシステム化

(産総研／高橋健司氏)

14:35-15:35 ケイデンスの先端プロセスへ向けた戦略と技術のご紹介

(日本ケイデンス・デザイン・システムズ社／牧井徹氏)

15:35-15:40 休憩

15:40-16:40 新次元への架け橋：チップレット技術による半導体革命

(Rapidus株式会社／折井靖光氏)

### HotChips 2023における 最新のチップ開発動向

2023/09/29

東京大学 工学系研究科 d.Lab

長谷川 淳

東京大学

産総研

第51回AIチップ設計拠点フォーラム講演資料より

# 特許出願及び論文発表

|            | 2023年度 | 2024年度 | 計  |

|------------|--------|--------|----|

| 研究発表・講演    | 2      | 4*     | 6* |

| フォーラム開催    | 9      | 3      | 11 |

| 展示会への出展    | 0      | 0      | 0  |

| 論文         | 0      | 0      | 0  |

| 受賞実績       | 0      | 0      | 0  |

| 新聞・雑誌等への掲載 | 0      | 0      | 0  |

| 特許出願       | 0      | 0      | 0  |

※投稿中の1件含む

2024年6月15日現在

## ＜評価項目3＞マネジメント

### (1) 実施体制

※ 受益者負担の考え方

### (2) 研究開発計画

# 報告内容

ページ構成

## 1. 意義・アウトカム（社会実装）達成までの道筋

※本事業の位置づけ・意義

(1)アウトカム達成までの道筋

(2)知的財産・標準化戦略

## 2. 目標及び達成状況

(1)アウトカム目標及び達成見込み

(2)アウトプット目標及び達成状況

## 3. マネジメント

(1)実施体制

※受益者負担の考え方

(2)研究開発計画

- NEDOが実施する意義

- 実施体制

- 個別事業の採択プロセス

- 研究データの管理・利活用

- 予算及び受益者負担

- 目標達成に必要な要素技術

- 研究開発のスケジュール

- 進捗管理

- 進捗管理：事前/中間評価結果への対応

- 進捗管理：動向・情勢変化への対応

- 進捗管理：成果普及への取り組み

- 進捗管理：開発促進財源投入実績（非該当）

- モティベーションを高める仕組み（非該当）

## NEDOが実施する意義

- ◆ デジタル社会Society5.0実現には、高度な情報処理に対応可能な半導体を開発し、革新的な製品やサービスを生み出す公益性の高い国家的な取り組みが必要。

- ◆ 市場の拡大が予想されるAI 半導体において、チップレット設計基盤は、今後の半導体産業の中核的な機能になりうるポテンシャルを秘めており、我が国の産業競争力強化および産業裾野拡大として国が主導して取り組む意義。

- ◆ 開発を支援するチップレットの設計基盤技術開発は、世界標準に準拠した横断的な取り組みが必要であり民間企業単独では難しく、市場原理のみで推進を図ることは困難。

**NEDOが関与し推進することが重要**

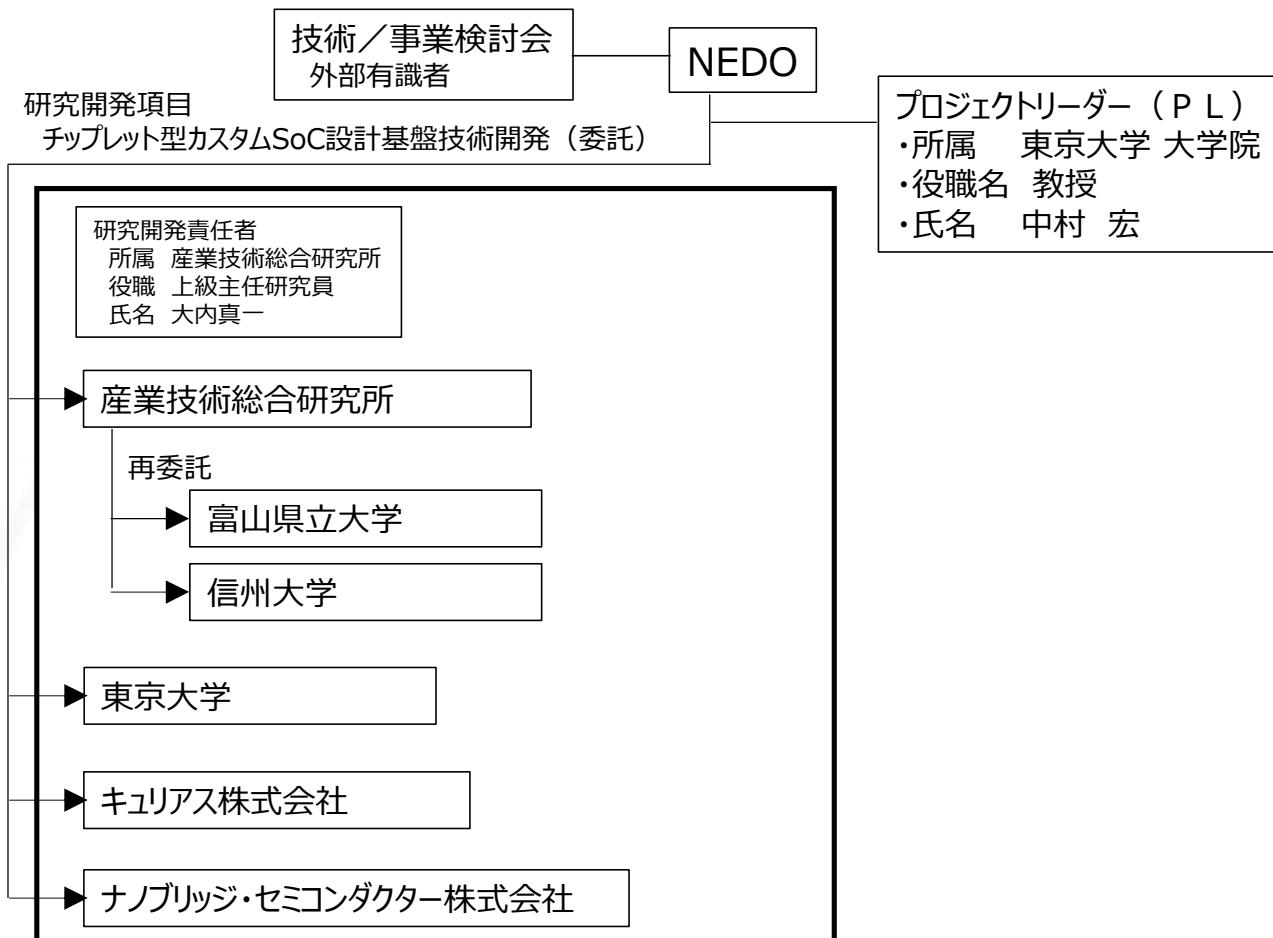

# 実施体制

・公募により研究開発実施者を選定

・各実施者の研究開発能力を最大限に活用し、効率的かつ効果的に研究開発を推進する観点から、NEDOが選定した**プロジェクトリーダー（PL）**の下で研究開発を実施

・NEDO・PL・実施者間で、**月次定例会で進捗を確認**。抽出課題に対し対処方法を適宜協議し対応

・研究開発において、委託先内で打合せを定期的に**週1回以上実施**（再委託先含む）

・**技術/事業検討会**を設置・開催し、研究開発期間変更に伴うプロジェクトの方向性について、有識者に検討いただいた

# 事業者の採択プロセス

## 【公募】

公募予告（1月20日）⇒ 公募（2月27日）⇒ 公募〆切（3月29日）（2023年）

## 【採択】

採択審査委員会（4月25日）

### ▶採択審査項目

NEDOの標準的採択審査項目の他、以下項目を加え重み付けを行なった。

- ①国際動向との連動、外部の協力者との連携

- ②民間企業等で利活用できる仕組み構築の可能性

### ▶採択条件

採択審査委員会では、改善要望として「実施計画書において、チップレットエコシステムの構築に係る具体的なターゲット領域やスケジュールを記載して取り組むこと。」を付して採択が行われた。

### ▶留意事項

研究の健全性・公平性の確保に係る取組；公募の際にその他の研究費の応募・受入状況を確認し、不合理な重複及び過度の集中がないか確認した。（参考：公募要領の留意事項(18)）

## 研究データの管理・利活用

- ◆ 事業開始に際し、NEDOの方針に沿って、知的財産及び研究開発データの取扱いについて事業者間で合意書を定め、知財運営委員会を設置。

- ◆ 本プロジェクトにおける知的財産及び研究開発データの取扱いは、知財運営委員会にて審議決定。

- ◆ 秘密情報の取扱いは、合意書に沿って、適切に管理。

## 予算及び受益者負担

### ◆ 予算

(単位：百万円)

| 研究開発項目                 |            | 2023年度 | 2024年度※ | 合計  |

|------------------------|------------|--------|---------|-----|

| チップレット設計基盤構築に向けた技術開発事業 | 委託<br>100% | 469    | 7※      | 476 |

※2023年度繰越予算分

### ◆ 委託事業の理由

国民経済的には大きな便益がありながらも、研究開発成果が直接的に市場性と結び付かない公共性の高い事業のため。

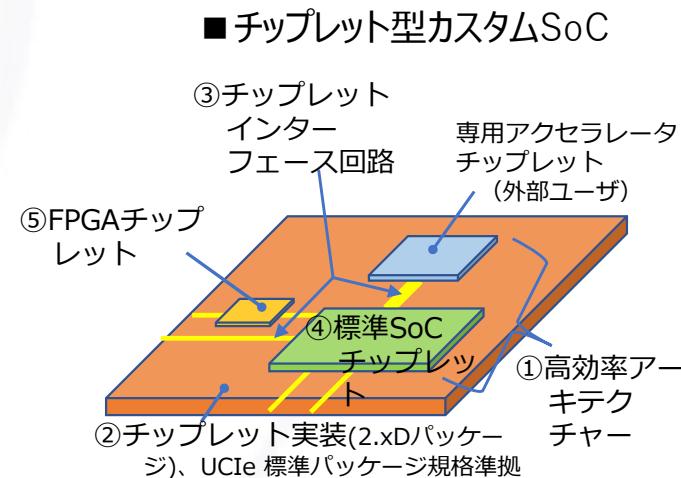

# 目標達成に必要な要素技術

## 研究開発項目：チップレット型カスタムSoC設計基盤技術開発

### 実施項目1～5を設定

チップレットライブラリ

### 実施項目5：FPGAチップレットの開発

#### 内容

エッジコンピューティング向けチップレット型カスタムSoCの構築に即したプログラム可能な汎用ロジックチップ（FPGA）を開発。実装評価は実施項目2および4と連携。また、ポテンシャルユーザーの要求仕様を精密に調査し、より広いユーザーに利用されるようFPGAの有用性も確認。

・専用アクセラレータチップレットの接続は、外部ユーザとの連携を想定

### 実施項目4：標準SoCチップレットの開発

#### 内容

実施項目1で策定されるSoCチップ分割面を再接続するための複数のチップレットインターフェースを有する標準SoCチップレットを開発。実装評価は実施項目2と連携、実施項目3のインターフェース仕様や実施項目5のFPGA設計情報も取り込む。

### 実施項目1：高効率チップレットアーキテクチャーの開発

#### 内容

チップレット化の分割面を検討し、複数のアプリケーションを許容可能な汎用性を持ち、かつ分割前のSoCと等価な機能を効率的に実現可能で、かつ、PCIe等の国際動向を考慮した、高効率なチップレットのアーキテクチャーを策定。実施項目2～5と連携。

### 実施項目2：チップレット実装技術の開発

#### 内容

PCIe等の標準規格に準拠したパッケージへの適用が可能でチップレットライブラリからの実装に対応した技術を開発。実装評価は実施項目3、4および5と連携。

### 実施項目3：チップレットインターフェース回路の開発

#### 内容

ヘテロジニアスなテクノロジーを許容するチップレットインターフェース技術の提供の解決策として、PCIe標準パッケージ仕様に準拠した物理層およびESD保護回路を開発。実施項目1および4と連携。

# 目標達成に必要な要素技術／各実施項目の目標

| 実施項目                    | プロジェクト中の最終目標                                                                                                                                                                                                                                             | 根拠                                                                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. 高効率チップレットアーキテクチャーの開発 | <ul style="list-style-type: none"> <li>想定ユーザや有識者から意見聴取を行い、標準SoCのアーキテクチャー、チップレットピン数、インターポーラメタライズ位置、バンプ位置のドラフト版を策定する。</li> <li>UCIEにおける作業部会での活動を行い、情報収集・技術提案の活動に努める。</li> </ul>                                                                            | <ul style="list-style-type: none"> <li>多数の想定ユーザのニーズを包含する仕様とし、エコシステムをより汎用性の高いものに仕上げるため。</li> <li>UCIEとの互換性を確保し、多数の接続選択肢を担保するため。</li> </ul>                                                                           |

| 2. チップレット実装技術の開発        | 5μm級微細配線、100~130μmの微細バンプ接続、およびUCIE標準インターフェースとLVDS準拠インターフェースを有するチップレット実装可能なインターポーラの設計仕様を検討する。                                                                                                                                                             | エッジ用途のマルチチップ実装技術開発を目的に、UCIEやLVDSでのチップレット接続を前提とした、より微細な配線やバンプ構造を持つ次世代インターポーラ基板設計仕様策定の必要があるため。                                                                                                                        |

| 3. チップレットインターフェース回路の開発  | <ul style="list-style-type: none"> <li>UCIE 標準パッケージ準拠のインターフェース回路（物理層）のアナログの基本設計を行い、アーキテクチャーを検討する。</li> <li>UCIE標準パッケージ準拠のインターフェース回路（物理層）のデジタル部のアーキテクチャーを検討する。</li> <li>ESD保護セルを使用したインターフェース回路の設計環境を整備し、評価用回路設計とレイアウトを進め初期検討を完了させる。</li> </ul>            | <ul style="list-style-type: none"> <li>エッジ用途に適したコスト・性能を両立する、アナログおよびデジタル部のUCIE準拠のチップレットインターフェースを提供するため。特に、プロジェクト開始時に選定した28nmテクノロジーにおいては、独自のIPを作成する必要があるため。</li> <li>また、UCIE規格に準拠するESD保護セルを独自に開発する必要があるため。</li> </ul> |

| 4. 標準SoCチップレットの開発       | <ul style="list-style-type: none"> <li>実施項目3の成果を標準SoCチップレットにインテグレーションするにあたり、ガイドラインを策定する。</li> <li>標準SoCチップレットの仕様案を検討する。</li> </ul>                                                                                                                       | <ul style="list-style-type: none"> <li>実施項目3における成果物を各チップレットに搭載するに際し、仕様の適合性を設計当初から確保する必要があるため。</li> <li>実施項目1と連携し、多数の想定ユーザのニーズを包含する標準SoCチップレットの構築が必要となるため。</li> </ul>                                                |

| 5. FPGAチップレットの開発        | <ul style="list-style-type: none"> <li>テクノロジーノード28nmで差動I/OであるLVDSの回路設計および物理設計を実施する。各I/Oを搭載したテストチップを評価回路の回路設計および物理設計を実施する。物理設計にあたり、電源線でのノイズや信号間のクロストークを低減するよう配慮する。伝送速度の設計目標値は差動I/Oが600Mbps、シングルエンドI/Oは125MHzである。</li> <li>FPGAチップレットの有用性を確認する。</li> </ul> | <ul style="list-style-type: none"> <li>標準SoCとFPGAチップレットの接続界面において、実際に低レイテンシなI/Fが実施項目2のインターポーラ上で実現できることを検証するため。</li> <li>FPGAの市場性をしっかりと勘案し、実際の社会実装を確かなものとするため。</li> </ul>                                             |

## 研究開発のスケジュール

| 実施項目                    | 2023年度                                                   | 2024年度            |

|-------------------------|----------------------------------------------------------|-------------------|

| 1: 高効率チップレットアーキテクチャーの開発 | 仕様案ドラフト版検討・作成                                            |                   |

| 2: チップレット実装技術の開発        | PCIe/LVDS対応インターポーラ仕様検討                                   |                   |

| 3: チップレットインターフェース回路の開発  | 物理層アナログ仕様案/基本設計<br>物理層デジタルアーキテクチャー検討<br>ESDセル設計情報整理、設計検討 | 最終目標              |

| 4: 標準SoCチップレットの開発       | 設計データ<br>要件の特定<br>仕様策定                                   |                   |

| 5: FPGAチップレットの開発        | 高速I/O設計<br>電源線評価                                         |                   |

| 評価時期                    |                                                          | 終了時評価             |

| 予算 (億円)                 | 委託                                                       | 4.69              |

|                         |                                                          | 0.07 ※2023年度繰越予算分 |

## 進捗管理

| 会議名          | 主なメンバー                                                                    | 対象・目的                                                                                                                                 | 頻度                                                       | 主催   |

|--------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|

| 進捗確認         | <ul style="list-style-type: none"> <li>実施者</li> <li>PL、PMgr、PT</li> </ul> | <ul style="list-style-type: none"> <li>実施者からの定期的な報告を受け、研究開発の状況を確認するとともに、今後の進め方について議論。</li> </ul>                                      | <ul style="list-style-type: none"> <li>毎月</li> </ul>     | 実施者  |

| 進捗管理         | <ul style="list-style-type: none"> <li>PMgr、PT</li> <li>実施者</li> </ul>    | <ul style="list-style-type: none"> <li>登録研究員の従事日誌・月報を確認し、研究開発に遅滞がないことをNEDOが確認</li> <li>実施者に対し予算執行状況の報告を求めて、研究開発に遅滞がないことを確認</li> </ul> | <ul style="list-style-type: none"> <li>毎月</li> </ul>     | NEDO |

| 予算措置を受けた検討会  | <ul style="list-style-type: none"> <li>PMgr、PT</li> <li>実施者</li> </ul>    | <ul style="list-style-type: none"> <li>2023年12月の予算措置を受け、今後の方向性についてPMgr等で議論するとともに関係者で対応を協議</li> </ul>                                  | <ul style="list-style-type: none"> <li>週に1回以上</li> </ul> | NEDO |

| NEDO技術/事業検討会 | <ul style="list-style-type: none"> <li>外部有識者</li> <li>PMgr、PT</li> </ul>  | <ul style="list-style-type: none"> <li>事業期間短縮に伴うプロジェクトの方向性について外部有識者が確認・検討</li> </ul>                                                  | <ul style="list-style-type: none"> <li>年1回</li> </ul>    | NEDO |

## 進捗管理：事前評価結果への対応

|   | 問題点・改善すべき点※                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 対応                                                                                                                                                                                                                                                                                                                      |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | <p>・本事業では、チップレットインターフェース設計技術開発が特に重要な項目である。UCIe (Universal Chiplet Interconnect Express) 等の<u>世界の技術動向を踏まえながら、迅速に仕様策定と技術開発を進める</u>ように十分な配慮が必要である。</p> <p>・プロセスとチップテストを含めてのトータルコストを考えると、平面（モノリシック）でのチップ作製に強みがある可能性も指摘されている。<u>これまでのSystem-in-Packaging (SiP)などの課題（Known Good Die(KGD)問題）などを改めて分析し、そこに立脚した提案</u>に期待したい。例えば、高性能半導体デバイスにターゲットを絞ることや、我が国が強みを有するマテリアル、パワー半導体など新たな視点を運動させることを期待する。とりわけ<u>産業界の具体的ニーズをとらえ、ターゲットを明確</u>にしておくことは重要である。</p> <p>・世界的に見れば大手10企業がUCIe という団体を組織して規格の策定を開始しており、この<u>規格との関係を明確</u>にする必要がある。計画の中のチップレット実装手法開発についてUCIeに合わせるのかどうか早期に決めるべきであり、またその他の標準SoC やAI半導体部分についてはどのようなものを作成するのか慎重に検討する必要がある。特に後者については、単純に安価なプロセスノードを用いるなどの方法では差別化が難しく、チップレットIP の提供方法やそもそも何を開発するのかについて工夫が必要である。</p> | <p>世界標準となり得るUCIe（2022年3月に業界を代表する10社で設立された業界団体、「チップレット」と呼ばれる半導体のダイ上のモジュールを相互接続するための標準仕様の策定を推進）の活動の最新動向を継続的に調査し、UCIeで策定されたチップレット実装に必要な半導体ダイ間の相互接続のための仕様等を取り込むことで、<u>国際動向に連動した研究開発を実施</u>する。また、<u>トータルコストに</u>関わる複数の半導体ダイ接続時の問題等を踏まえた取り組みや、<u>ターゲット分野の絞り込み</u>、標準SoCやAI半導体などの開発内容等は、有識者の意見を参考にし、<u>基本計画や実施方針に反映</u>した。</p> |

※出所：[https://www.meti.go.jp/policy/tech\\_evaluation/e00/03/r04/J127.pdf](https://www.meti.go.jp/policy/tech_evaluation/e00/03/r04/J127.pdf)

## 進捗管理：動向・情勢変化への対応

- ◆ 令和6年能登半島地震の影響により、事業者努力とは無関係に発注品の納入遅れが予見されたため、実施項目5の該当予算分を2024年度に繰り越して遅延を挽回する支援を行った。

- ◆ 2024年度の予算措置を受け、今後の対応について実施者やPLと意見交換を行うと共に、研究開発期間変更に向けた手続等の支援を行った。

## 進捗管理：成果普及への取り組み

事業者の主な発表

- ◆ 大内真一、「先端システムオンチップ（SoC）設計技術」、産業技術総合研究所先端半導体研究センター(SFRC)第一回公開シンポジウム、2024年5月

- ◆ 上口光ほか、「チップレット技術に向けた高速I/Oセル用ESD保護セルの検討」、LSIとシステムのワークショップ2024、2024年5月

- ◆ S. Shimomura, et. al., Single-Layer Wiring Design in UCIe to Realize Low-Cost Interposer Substrate, submitted to international conference