## 10 ピジネスマッチング

# "RISC-V"で革新的システム開発を実現

### 東京科学大学 RISC-Vデザインセンター

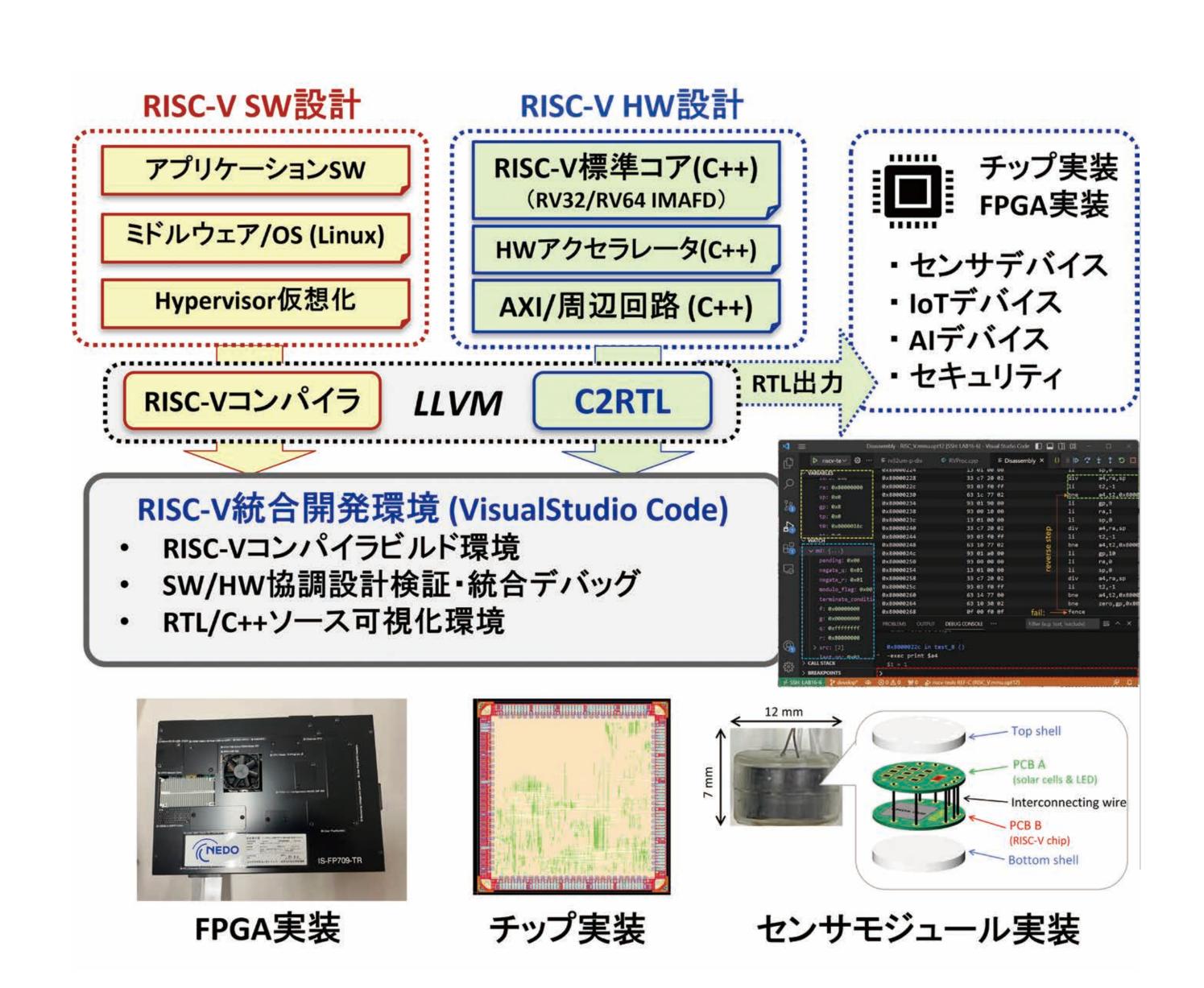

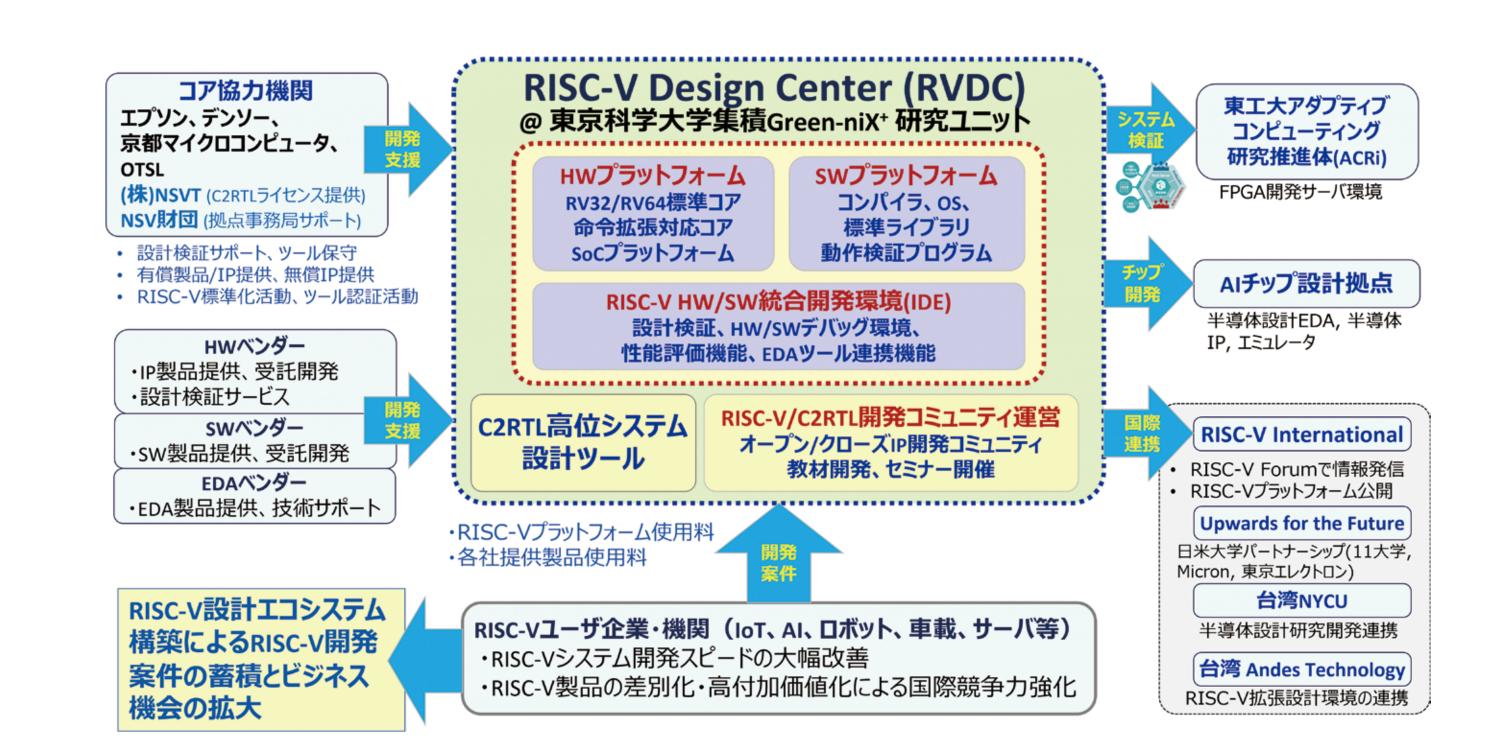

ライセンスフリー命令セット仕様であるRISC-VアーキテクチャとHWアクセラレータのシステム構成により、SW定義 の機能柔軟性と高い処理効率を両立する優れたSoCソリューションを、NEDOプロジェクト「RISC-Vシステム設計プ ラットフォームの研究開発」において技術構築し、IoT・AI領域向け専用チップ開発において従来技術に比べ数十倍~ 数百倍の処理電力効率を実現しました。この高効率 RISC-V SoC ソリューションを RISC-V デザインセンターで提供し ます。

## 製品・サービス紹介

RISC-Vを用いたAIエッジデバイス向け高性能・省電力 システムを、システム機能のSW記述(C/C++言語)か ら直接チップ開発までを早期に完成できる画期的な C2RTL高位設計フローによって、今後急拡大するAI市 場へ様々な新規AIエッジソリューションのSW/HW協調 設計検証環境を提供するとともに、RISC-Vデザインセン ターと提携するHW・SW・EDA各ベンダー企業ととも にRISC-V開発エコシステムを構築して参ります。

## 希望するマッチング先

IoT・AI・ロボット・車載・航空・宇宙・次世代通信など の最先端分野で、新規マーケット開拓のための国際競争 力のある製品開発を目指す企業・団体に対して、RISC-V コアとC2RTL高位設計環境による早期開発と国内企業 の総力による設計支援体制でサポートします。

プロジェクト実施期間

2022年度~2024年度

NEDOプロジェクト名

省エネAI半導体及びシステムに関する技術開発事業/AIエッジコンピューティングの産業応用加速のための設計技術開発/ RISC-Vシステム設計プラットフォームの研究開発

国立大学法人東京科学大学 工学院 一色 剛 Email: isshiki@ict.e.titech.ac.jp

お問い合わせ先