# ①ポスト5G情報通信システムの開発

## (d) MEC

(d1) MEC向け大規模先端ロジックチップ設計技術の開発

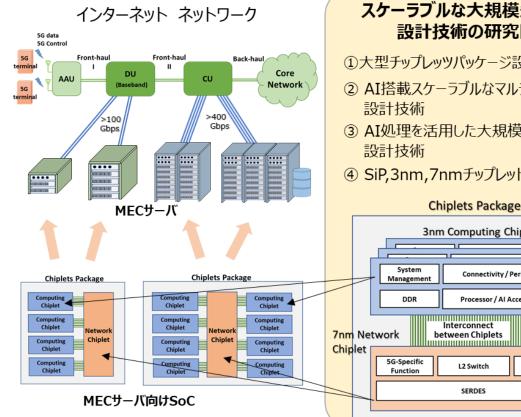

スケーラブルな大規模先端SoC設計技術の研究開発

(d2) MECサーバー向け広帯域・大容量メモリモジュール設計技術の開発

広帯域大容量フラッシュメモリモジュールの研究開発

# スケーラブルな大規模先端SoC設計技術の研究開発

## 実施者

#### 株式会社ソシオネクスト

#### 概要

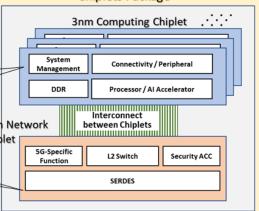

MEC向け大規模先端ロジックチップ開発の設計技術として、マルチチップ搭載可能な「大型チップレッツパッ ケージ設計技術」、AI処理システム構築可能な「AI搭載スケーラブルなマルチチップ設計技術」、短期間で 効率的に開発する「AI処理を使った大規模先端SoC設計技術」および、上記技術と先端プロセスを使った 「SiP、3nm、7nmチップレット実証チップ Iの開発を行う。

## スケーラブルな大規模先端SoC 設計技術の研究開発

- ①大型チップレッツパッケージ設計技術

- ② AI搭載スケーラブルなマルチチップ

- ③ AI処理を活用した大規模先端SoC

- ④ SiP,3nm,7nmチップレット実証チップ

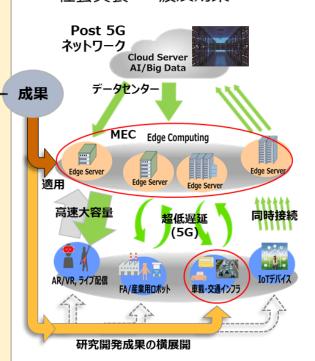

### 社会実装 ~波及効果~

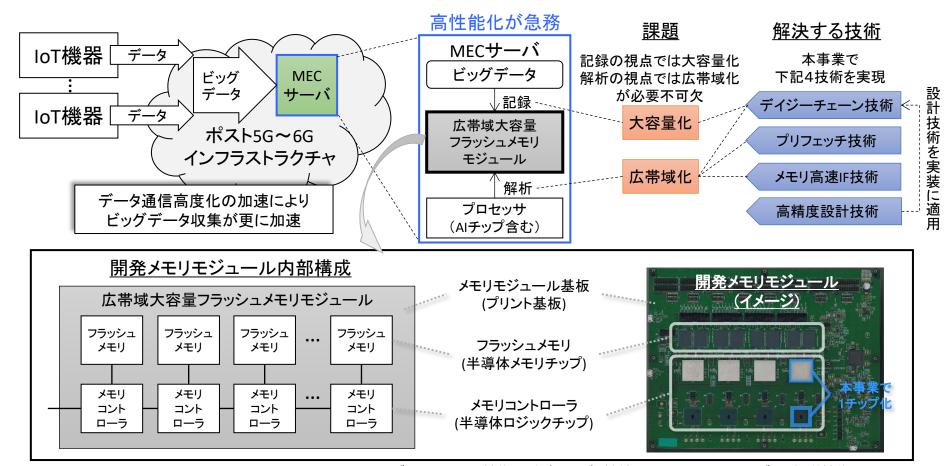

# 広帯域大容量フラッシュメモリモジュールの研究開発

実施者キオクシ

キオクシア株式会社

概要

ビッグデータ増大に耐えうる高性能なMECサーバには、メモリの大容量化と広帯域化が必要不可欠である。 デイジーチェーン技術※ 1・プリフェッチ技術※ 2・メモリ高速IF技術・高精度設計技術を用いた、広帯域大容量フラッシュメモリモジュールの研究開発を行う。

※1 デイジーチェーン技術:数珠つなぎに接続したコントローラ間でのデータ転送技術 ※2 プリフェッチ技術:必要性を予測して事前にフラッシュメモリからコントローラにデータを移送する技術