# ②先端半導体製造技術の開発

## (b) 先端半導体の後工程技術 (More than Moore技術) の開発

## (b1) 高性能コンピューティング向け実装技術

3DIC技術の研究開発

高性能大面積3.xDチップレット技術の研究開発

## (b2) エッジコンピューティング向け実装技術

ダイレクト接合3D積層技術開発(WoWおよびCoW向け装置・プロセス開発)

ポスト5Gエッジコンピューティング向け半導体の3D積層要素技術研究開発

## (b3) 実装共通基盤技術

最先端パッケージ評価プラットフォーム創成

次世代情報通信向け先端パッケージの材料開発

次世代半導体パッケージ開発

ハイブリッド接合技術開発

ポスト5G向けチップオンウェハダイレクト接合3D積層統合技術開発

先端半導体実装のためのレーザ転写技術の開発

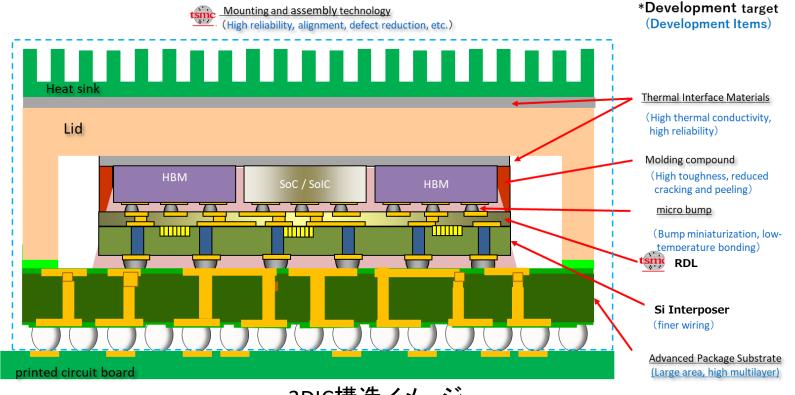

# 3DIC技術の研究開発

実施者

TSMCジャパン3DIC研究開発センター株式会社

概要

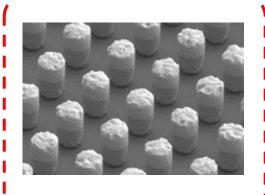

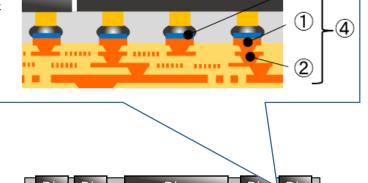

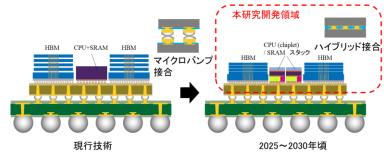

ポスト5G社会において、<u>情報通信システ高性能コンピューティング</u>、<u>広帯域5Gネットワークスイッチング</u>、<u>自動運転</u>の人工知能や統合センシング・診断等を実現するためには、半導体デバイスのさらなる集積化・高性能化が不可欠である。 本研究開発では、半導体デバイスのさらなる集積化・高性能化を可能とする 3Dパッケージ技術(ロジック、メモリー、周辺デバイスを1つのパッケージに高密度に実装する技術)の開発を行う。

3DIC構造イメージ

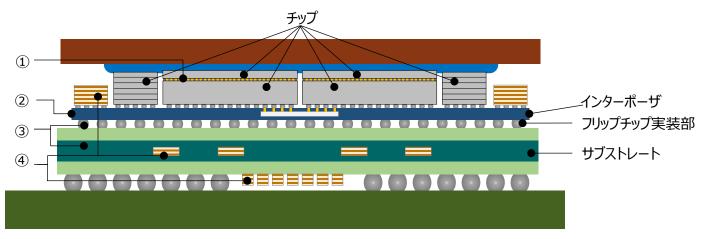

# 高性能大面積3.xDチップレット技術の研究開発

実施者

日本サムスン株式会社

概要

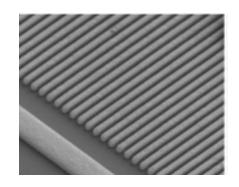

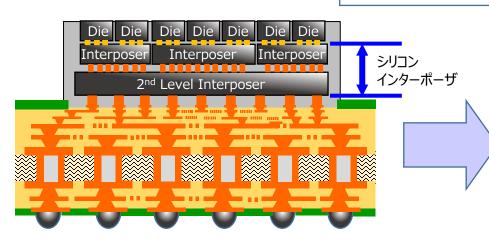

本事業ではポスト5G情報通信システムを支えるHPC/AI用プロセッサ向けチップレットモジュールに関し、 処理性能向上のための<u>一層の高集積化とチップ間データ転送帯域の向上、大面積化と製造性の向上</u> によるコストダウン、および電源の安定供給の実現を目的に、2.xD/3Dを組合わせた3.xDチップレット技 術を開発する。

## ■開発内容

上記の開発目的を達成するために、専用のパイロットラインを構築し以下の4項目の研究開発を行う。

①ファインピッチChip to Waferボンディング技術 : チップを効率良く3Dに実装する技術の開発

②高機能大面積樹脂インターポーザ技術 : より多くのチップを集積させるための大型化技術の開発

③大面積サブストレートの微細フリップチップ実装技術:大型化しても反りを抑えて製造性を維持するための技術

④雷源特性向上技術

: 異種多チップモジュール内でも安定した電源を供給する技術の研究開発

全項目において国内の材料/装置メーカと緊密に連携を図り、共に3.xDチップレット関連技術の一層の競争力強化を推進する。

3.xDチップレットモジュールの構造例

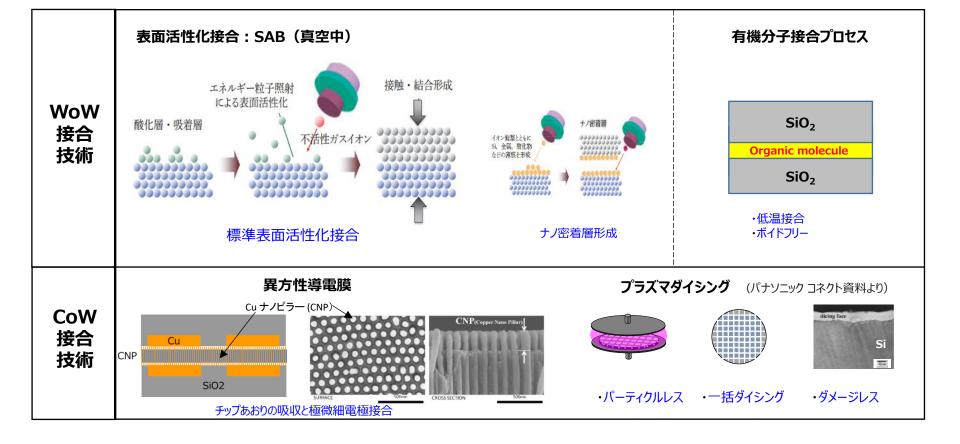

# ダイレクト接合3D積層技術開発 (WoWおよびCoW向け装置・プロセス開発)

## 実施者

先端システム技術研究組合

概要

ウェハ、チップレベルの<u>Cu-Cu低温ハイブリッドダイレクト接合</u>による3D集積実現に向けて、1)<u>表面活性化による低温化接合を用いたWoW(Wafer on Wafer)接合技術</u>を開発し、さらに<u>有機分子接合によるボイドフリー化やアライメントの高精度化とパーティクル低減化</u>を行い、これらの技術を統合した<u>接合装置の実用化</u>を行う。2)無機異方性導電膜を用いた低温接合および、プラズマを用いた低ダスト小片化ダイシングによるCoW(Chip on Wafer)接合技術を開発し、その装置化に取り組む。

# ポスト5Gエッジコンピューティング向け半導体の3D積層要素技術研究開発

# 実施者 ソニーセミコンダクタソリューションズ株式会社 世イバー空間とフィジカル空間を高度に融合させたシステムを実現するためには、必要なときに必要な情報が得られる、サイバーとフィジカルのリアルタイムな融合が肝となるが、その基幹技術であるポスト5G技術として、さらに高度なエッジコンピューティングの実現は欠かすことができない。特に、ネットワークを維持するための電力消費量の低減、瞬時の反応を実現するための高レスポンスや並行処理、より正しい状況認識を実現する3D積層技術が注目されている。そこで、弊社が進めている3D積層技術のプロセスモジュール開発を加速させ、ロバストな半導体製造プロセス技術の早期確立を目指す。

## 本研究のポイント

目標とする3 D積層半導体デバイスのイメージ図を示す。イメージセンサ及びイメージセンサと同一サイズのロジック、イメージセンサと異なるサイズのAIロジックとメモリが3 D積層されている。

Logic CMOS Image Sensor

AI-Logic Memory

接合素子A:同一サイズの半導体チップをWoW (Wafer on Wafer) によりファインピッチで"Cell to Cell接続"するモジュール要素技術の開発を行う。

接合素子®: 異なるサイズの半導体チップをCoW (Chip on Wafer) によりファインピッチで"ヘテロジニアス接続"するモジュール要素技術の開発を行う。

コア技術

弊社は、積層技術とイメージセンサにおいて世界最先端の技術を保有し、当該領域にてスマートフォン向けカメラでのデファクトスタンダート技術を世に送り出した実績を有する。特にそれぞれの積層面に形成したCu(銅)接続端子を用いて、物理的な積層と電気的な接続を同時に行うCu-Cu接合技術は、弊社が世界で初めて実用化している。

成果 Society5.0における自動運転自動車やスマートファクトリーなどのフィジカル空間で、エッジコンピューティングを担う 半導体素子として社会実装される。

# 最先端パッケージ評価プラットフォーム創成

実施者

株式会社レゾナック

概要

レゾナックを含む、<u>基板、装置、材料メーカが、コンソーシアム(JOINT2)を設立</u>し、評価プラットフォームを活用して、次世代半導体パッケージの技術変化に応じた評価技術、基板、材料および装置の開発を行い、日本国内の基板、装置、および材料メーカの事業拡大に寄与する。21~22年度は、連携企業とともに保有する材料・装置およびプロセス技術を活用して事業を開始するとともに、必要な装置を導入する。23~26年度は、一貫した評価を実施して、量産に繋がる評価を進める。

微細バンプ接合技術

平坦基板技術

微細配線技術 新規インターポーザ技術

基板の大型化による パッケージレベル 信頼性

放熱技術

# 次世代情報通信向け先端パッケージの材料開発

実施者

住友ベークライト株式会社

概要

3次元実装の鍵となる実装密度向上において、特に重要となるWLP (Wafer Level PKG) 向け封止材、アンテナ向け封止材 (樹脂コンパウンド)、再配線(RDL)用感光材のファインピッチ対応技術を開発する

## (1) High performance computing(HPC) 向けWafer level package(WLP)

## 封止材(固形)

- ・µBump部充填を可能にするMold under fill(MUF)技術開発

- ・大型Panel level package(PLP)を実現する反り制御技術開発

- ・チップの性能向上を促す放熱技術開発

- ・耐リフロー性向上、密着向上技術開発

|            | 生産性 | 信頼性 | コスト |

|------------|-----|-----|-----|

| 現行技術(液状樹脂) | STD | STD | STD |

| 当社技術(固形樹脂) | 改善  | 改善  | 改善  |

\*STD:液状樹脂での量産レベル

## 感光材

- ・高速伝送を実現する低誘電損失(Df)技術開発

- ・光伝送を見据えた光導波路用感光材開発

- ・環状オレフィン樹脂(PCO)を中心とした当社独自技術の展開

- ・優れた誘電特性

- •诱明性

- ·高Tg

# (2) RF module向けAntenna in/on package (AiP/AoP)

## 誘電樹脂 封止材 感光材

## 誘電樹脂 (アンテナ向け)

- ・アンテナの小型化及び帯域向上を可能にする誘電樹脂開発

- ・半導体組立技術+誘電樹脂を適用したアンテナ工作精度の向上及びセラミック代替技術開発

|             | 生産性 | 加工精度 | アンテナ特性 | コスト |

|-------------|-----|------|--------|-----|

| 現行技術(セラミック) | STD | STD  | STD    | STD |

| 当社技術(誘電樹脂)  | 改善  | 改善   | 改善     | 改善  |

#### 封止材

\*STD:セラミックでの量産レベル

- ・多数の受動部品やFlip chip下を充填するMUF技術開発

- ·System in package(SiP)の放熱技術開発

#### 感光材

・将来的なWLPへの移行に向けた技術開発(左記)

# 次世代半導体パッケージ開発

実施者新光電気工業株式会社

概要

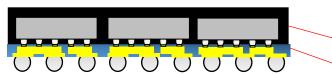

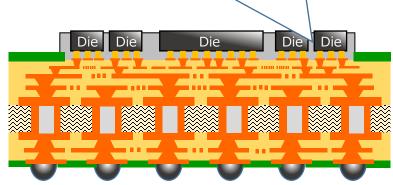

ポスト5G情報通信システムにおいては、より高性能な半導体が要求される。データ処理を担うプロセッサ周辺では、シリコンインターポーザを用いたマルチチップ化・3次元集積化が主流になることが想定されている。しかしながら、シリコンインターポーザには、パッケージ基板の大型化に伴うコスト上昇と、多層化・微細化に伴うチップ間信号伝送(電源品質)の安定性低下という課題がある。この課題を解決するために、シリコンインターポーザを用いずに狭ピッチパッドのチップを直接実装し、大面積実装と電源安定供給を実現するための半導体パッケージを開発する。

|      | 現行          | 次世代 |

|------|-------------|-----|

| コスト  | $\triangle$ | 0   |

| 電源品質 | $\circ$     | 0   |

## ●開発要素

- ①狭ピッチパッド形成技術

- ②小径ビア加工技術

- ③接続端子形成技術

- ④組み立て実装技術

現行主流の半導体パッケージ

次世代半導体パッケージ

# ハイブリッド接合技術開発

## 実施者 東レエンジニアリング株式会社 概要 半導体の進化において、今後

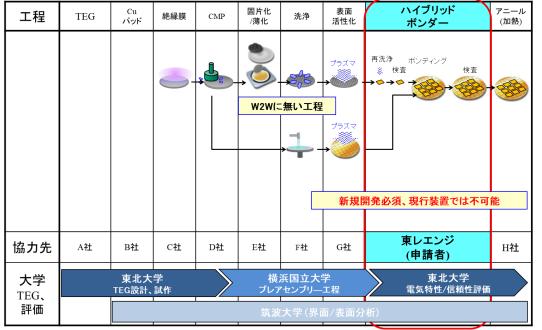

半導体の進化において、今後更に求められる高度な最終アプリケーションの実現は単一デバイスの微細化による高集積化や高性能化のみでは達成できず、メモリー、ロジック、パワー、光等の様々なデバイスを高度に並行運用可能な「3D異種融合(ヘテロジニアス)デバイス」が必要とされている。その究極の接合方法がはんだを使用しないハイブリッド接合であるが、現時点で量産化されているのは、ウエハ同士の貼合わせであり、ウエハに個片のチップを接合する方法は実用化されていない。本提案事業では、当該接合用ボンダーの開発を行う。

本開発は、D2W(Die To Wafer)ハイブリッド接合技術開発を、申請者の東レエンジニアリングと、その共同研究先の東北大学、横浜国立大学、筑波大学で実施する。

#### <D2W工程と開発スキーム>

## <本研究開発テーマ領域>

#### <本研究開発テーマの特長>

|               | W2W(Wafer to Wafer)                    | D2W(Die to Wafer)    |  |

|---------------|----------------------------------------|----------------------|--|

| 歩留まり          | 積層数が増えると<br>不良ポイントが<br>累積されて<br>歩留まり低下 | 良品だけを<br>選択して実装可能    |  |

| 異サイズ<br>チップ実装 | 異サイズチップの<br>接合ができない                    | 様々なサイズのチップの<br>接合が可能 |  |

# ポスト5G向けチップオンウェハダイレクト接合3D積層統合技術開発

実施者 ヤマハロボティクスホールディングス株式会社

概要

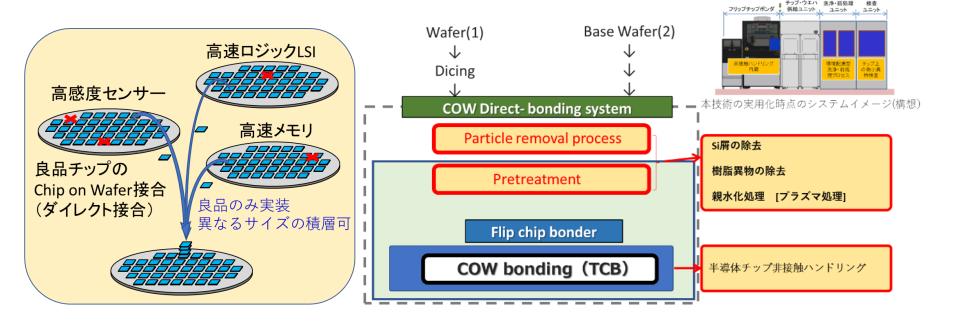

ポスト5G社会に必要な先端デバイスを実現するためには、複数の半導体チップをダイレクト接合技術により、チップオンウェハで3次元実装していくことが要求される。しかし従来技術では、ダイシング後の半導体チップ表面に異物や汚れが残留し、接合品質に影響を与え、実用化の深刻な障害となっている。本事業では、2022~2023年度に、個片化した薄LSIチップ表面を清浄に洗浄・前処理し、それを非接触でハンドリングする技術などの要素開発を行い、2024年度にチップオンウェハダイレクト接合システム技術を確立する。

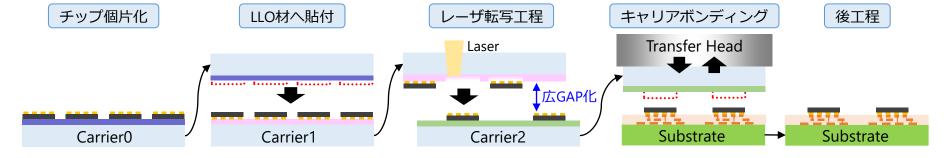

## 先端半導体実装のためのレーザ転写技術の開発

## 実施者

## 東レエンジニアリング株式会社

## 概要

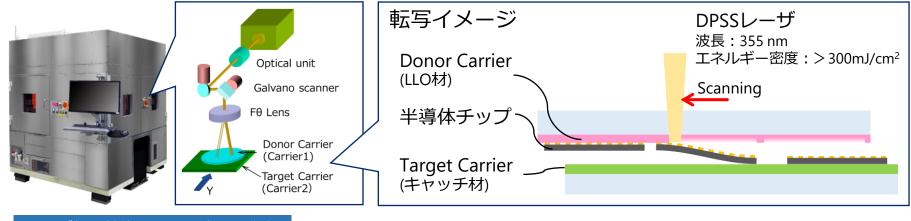

先端半導体では、高機能化・高性能化を実現するために、半導体チップを更に薄くすることが求められている。 しかしながら、フリップチップボンダーなどで用いられるニードルピックアップなどの従来技術では、大型で薄く脆弱なチップのハンドリングは困難で、今後の先端半導体の量産には、新しいチップハンドリング技術が必要とされている。本事業では、µLEDの超小型チップのハンドリングに使用されているレーザ転写技術を応用し、大型で薄く脆弱なチップのハンドリングを、高スループットで実現する技術を開発する。

## レーザ転写技術を用いた実装工程例