## ②先端半導体製造技術の開発

- (d) 国際連携による次世代半導体製造技術開発

- (d1) 高集積最先端ロジック半導体の製造技術開発

日米連携に基づく2nm世代半導体の集積化技術と短TAT製造技術の研究開発

- (d2) 光電融合に係る実装技術および確定遅延コンピューティング基盤技術開発

- (d2-1) 光チップレット実装技術

光チップレット実装技術の研究開発

(d2-2) 光電融合インターフェイスメモリモジュール技術

光電融合インタフェースメモリコントローラの研究開発

(d2-3) 確定遅延コンピューティング基盤技術

高効率な確定遅延コンピューティング基盤技術の研究開発

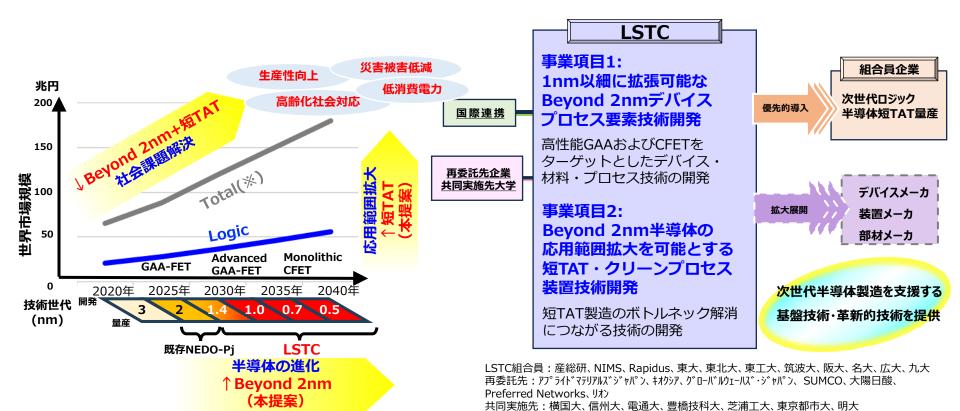

(d3) Beyond 2nm世代向け半導体技術開発

Beyond 2nm及び短TAT半導体製造に向けた技術開発

(d4) 2nm世代半導体のチップレット・パッケージング設計・製造技術開発

2nm世代半導体のチップレットパッケージ設計・製造技術開発

(d5) 先端パッケージング等を含む後工程高度化プラットフォームの構築

半導体後工程自動化・標準化の開発・実証に関する研究開発

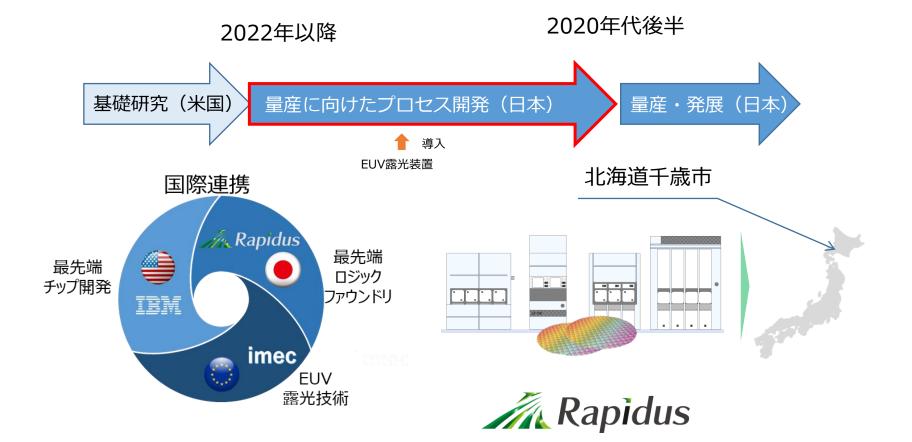

## 日米連携に基づく2nm世代半導体の集積化技術と短TAT製造技術の研究開発

# 実施者 Rapidus株式会社 概要 ・ 米国IBM社他と連携して2nm世代のロジック半導体の技術開発を行い、国内短TATパイロットラインの構築と、テストチップによる実証を行っていく。 ・ ベルギーimecとも連携し、EUV露光技術を用いた2nm世代パターニング技術の開発を行う。 ・ 研究期間終了後は、その成果をもとに先端ロジックファウンドリとして事業化を目指す。

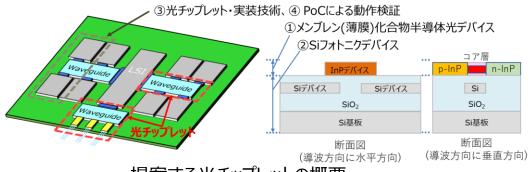

## 光チップレット実装技術の研究開発

### 実施者

日本電信電話株式会社、古河電気工業株式会社、NTTイノベーティブデバイス株式会社、NTTデバイスクロステクノロジ株式会社、新光電気工業株式会社

#### 概要

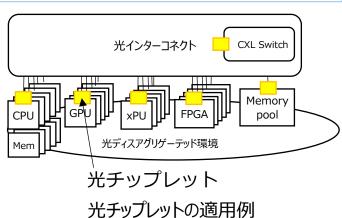

- ポスト5Gで必要となる次世代情報通信システムを支えるため、ゲームチェンジにつながる先端半導体将来技術の研究開発として、**光電融合技術**を用いた**パッケージ内光配線技術**の開発に取り組む。

- これを実現するために光集積回路(PIC)と電子集積回路(EIC)を高密度パッケージング技術を用い<u>八イブリッド実装した光電融合デバイス(光チップレット)</u>の開発を行う。当該技術をロジックIC等を含む パッケージ内光配線に適用することで光ディスアグリゲーテッドコンピューティング等を実現し、システム全体のリソース削減により、低消費電力化を実現する。

#### LSI間を下記の性能で接続する光チップレットを開発する

・帯域密度 ≧ 1 Tbps/mm、・エネルギー効率 ≦ 2pJ/bit

#### 提案する光チップレットの概要

### パッケージ内光接続を実現するための開発項目

- ① メンブレン化合物半導体光デバイスの開発(担当:日本電信電話(株)、古河電気工業(株)、再委託:東京大学、慶應義塾大学)

- ② Siフォトニクス技術の開発(担当: NTTイノベーティブデバイス(株)、日本電信電話(株), 再委託: 千歳科学技術大学, Aloe Semiconductor Inc.)

- ③ 光チップレット・実装技術の開発(担当:NTTデバイスクロステクノロジ(株)、新光電気工業(株))

- ④ PoCによる動作検証(担当:日本電信電話(株))

#### 本提案の特徴

メンブレン化合物半導体光デバイスのSiフォトニクスへの集積、光デバイスに最適化した電子回路を設計、デバイス内蔵パッケージ技術による光チップレット化、LSI近傍に電気実装とともに光実装などの製造技術から開発をすることで帯域密度:1 Tbps/mm、エネルギー効率:2 pJ/bitの性能優位性を確保します。

## 光電融合インタフェースメモリコントローラの研究開発

#### 実施者

キオクシア株式会社、日本電信電話株式会社

概要

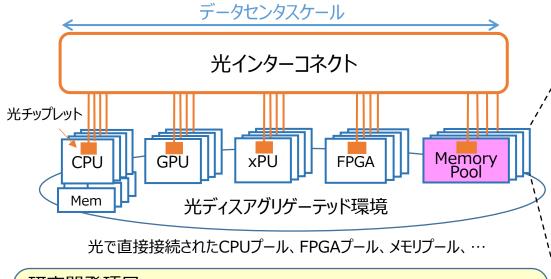

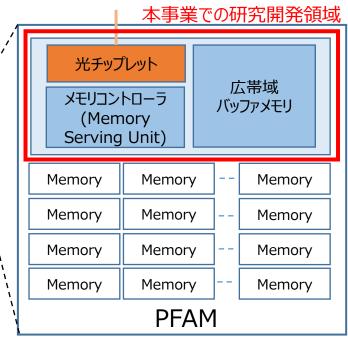

- ポスト5G世代の光ディスアグリゲーテッドコンピューティングを実現するために、データセンタスケールの光インターコネクトに光で直結できる広帯域メモリモジュールに向けて、「メモリコントローラ」と「広帯域バッファメモリ」を開発し、大容量のメモリ、光電融合デバイス(光チップレット)と共に「フォトニックファブリックアタッチトメモリモジュール(PRAM)」として実装する。

- PFAMにより、複数の演算リソースから広帯域の光により確定遅延でアクセスできるメモリプールを実現する。本開発の一部を国立大学法人東北大学に再委託する。

#### 研究開発項目

- ・広帯域化対応メモリコントローラ(Memory Serving Unit)開発

- ・広帯域バッファメモリ開発

- ·実装技術開発

## 本開発の特徴

- ・512Gbps以上の光通信帯域

- ・従来比30%の低消費電力化

光インターコネクトに光で直結できるメモリモジュール

## 高効率な確定遅延コンピューティング基盤技術の研究開発

実施者

日本電信電話株式会社、日本電気株式会社、富士通株式会社

概要

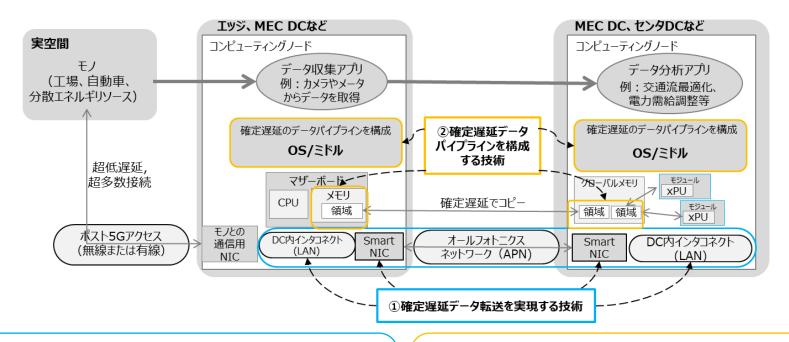

本事業では、ポスト5G通信インフラ(光電融合技術および光ネットワーク技術を含む)の高速性・低遅延性を活用した、データ転送から分析までの一連の処理を確定遅延で、かつ優れた電力効率で実行するコンピューティング基盤の実現を目的とし、プロセッサ間のデータ転送・データ処理の不確定性を低減した、高効率な確定遅延コンピューティング基盤技術の研究開発を行う。

#### ① 確定遅延データ転送を実現する技術

- デバイス間のPCIe-DMA(直接メモリアクセス)をデータセンタ (DC)規模で利用可能とするDCスケールPCIe-DMA技術

- DC内で利用されている遠隔DMA(RDMA)を、DC間で適用を可能とするDC間RDMA技術

#### ② 確定遅延データパイプラインを構成する技術

- データストリームを多重化し、プロセッサの利用効率を高めるデータ パイプライン最適化技術

- 共有メモリ領域を活用したメモリハンドオーバによる、低遅延なデータ受け渡しを行うデータパイプライン設計制御技術

# Beyond 2nm及び短TAT半導体製造に向けた技術開発

実施者 技術研究組合最先端半導体技術センター (LSTC)

(※) ロジック、メモリ、アナログ、製造装置などを含む

概要

2nm世代よりもさらに高性能な半導体(Beyond 2nm)実現に向けた革新的技術として、Beyond 2nm向けデバイス・材料・プロセス要素技術および短TAT・クリーンプロセス装置技術を開発する。当該技術の開発により、半導体の高性能化のみならず、長期化する半導体製造期間の短縮および早期な製品の市場投入を可能とし、我が国の半導体製造の競争力強化および半導体市場シェア挽回に大きく寄与する。半導体の更なる進化によるAI性能の飛躍的な向上と、短TAT化で、より多くの社会的ニーズへの対応を可能にし、社会課題解決とDX化推進に貢献する。

国際連携: CEA-Leti、imec

# 2nm世代半導体のチップレットパッケージ設計・製造技術開発

実施者

Rapidus株式会社

(共同実施先: Rapidus US, LLC、国立研究開発法人産業総合研究所、国立大学法人東京大学)

概要

本事業ではポスト5G情報通信システムを支える高性能半導体に必要なチップレットパッケージに関し、 2nm世代の半導体を用いたパッケージの大型化及び低消費電力化を実現する実装量産技術、設計に 必要なデザインキット、チップレットのテスト技術の確立を目的に、チップレットパッケージの設計・製造技術を 開発する。

2nm世代半導体の最先端チップレットパッケージ(2.xD, 3D)の設計・製造技術を確立するため、パイロットラインを国内に構築し、 量産・実用化を見据えて以下の開発項目を実施する。

開発項目① 2nm世代半導体を含む3次元(2.xD, 3D)パッケージ製造技術開発

特徴: 600mm角パネルでの有機絶縁膜RDLインターポーザの開発、3Dパッケージ技術、量産化技術の検証

開発項目② アプリケーション毎に最適な高効率/高性能チップレットパッケージの設計およびテスト技術開発

顧客向けデザインキット(Assembly Design Kit)の構築、KGD選別テスト(ウェハレベル/ダイレベル)の開発

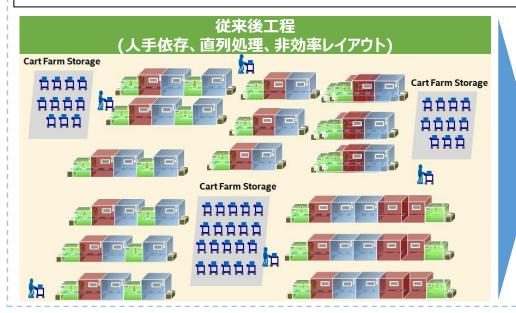

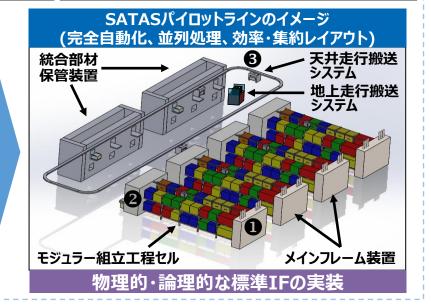

## 半導体後工程自動化・標準化の開発・実証に関する研究開発

#### 実施者

半導体後工程自動化·標準化技術研究組合 (SATAS)

概要

半導体企業は、地政学リスクを踏まえ強靭なサプライチェーンを柔軟に構築する事、またAI時代に向けより高度なパッケージング技術に対応する事が求められている。これらをより持続可能な方法で実現するため、本研究開発では、半導体製造工程の中でも人手への依存度が高く、経済安全保障に大きな影響を及ぼす後工程のうち、特に組立・検査に着目し、完全自動化に必要な装置・システム間の標準インタフェース(IF)開発に取り組み、プロトタイプや商用モデルへの実装検証、パイロットライン構築による実証を行う。なお、本研究開発は、関連する日本企業と当該分野の取り組みで先行するIntel Corporationとの日米連携体制により推進する。

## 【組合員(\*50音順)】

アオイ電子(株)、Intel Corporation、インテル(株)、オムロン(株)、化研テック(株)、国立研究開発法人産業技術総合研究所、シャープ(株)、信越ポリマー(株)、シンフォニアテクノロジー(株)、有限会社セミ・ジャパン、(株)ダイフク、TDK(株)、伯東(株)、平田機工(株)、(株)FUJI、(株)三菱総合研究所、ミナミ(株)、ミライアル(株)、村田機械(株)、ヤマハ発動機(株)、(株)レゾナック・ホールディングス、ローツェ(株)

#### 【研究開発項目】

- ①半導体後工程自動化に係る標準IF検討と プロトタイプ開発

- ②標準IFを実装した商用(市場投入)モデルシ ステム開発・検証

- ③標準IFを実装したパイロットライン開発・実証