# ②先端半導体製造技術の開発

- (e) 次世代メモリ技術開発

- (e1) 次世代広帯域・低消費電力HBMの製造技術開発

次々世代大容量・広帯域メモリHBM4Eの研究開発

(e2) 革新メモリの製造技術開発

CXL 3Dメモリ向けメモリアレイ技術の研究開発

(e3)エッジ向け AI メモリ設計・製造技術開発

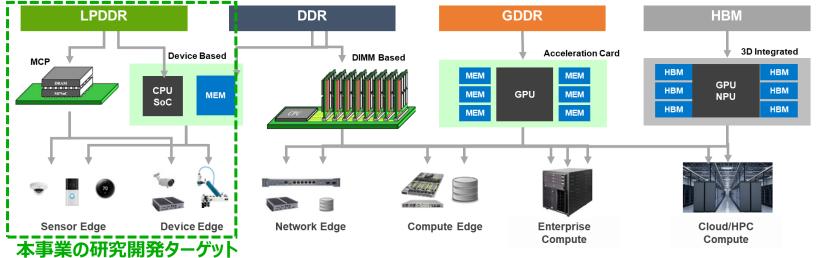

エッジ端末AI向けDRAMの革新的エネルギー効率改善を実現する製造技術の開発

# 次々世代大容量・広帯域メモリHBM4Eの研究開発

実施者 マイクロンメモリ ジャパン株式会社

概要

ポスト5G社会に向けたデータセントリックな高度コンピューティングシステム構築において、高速・低消費電 カ・大容量化に対応する広帯域メモリ (HBM) が必要不可欠となっている。特に、生成AIの利活用が進 むポスト5G社会では、重要基盤技術の一つとして注目されている。本事業では、HBM開発の基盤となる 先端DRAMの開発を遂行しながら、並行して先端CMOSデバイスの開発、及びTSV微細化技術の開発を 実行する。これらにより、次々世代のHBM4Eの研究開発を推進し、世界最高性能のHBM製造技術の開 発を行う。

### HBM4E

当社HBM3E比

: 32Gb (per DRAM die) 容量

帯域幅 : x 2倍 2.4TB/s

パワー :30%削減

: 12H以上 積層数

先端DRAM技術

先端TSV技術 TSV x2倍|12H

### HBMの高性能化の必要性

生成AI

**| ディープラーニング**

ハイパフォーマンス ハンハンハ コンピューティング

- 世界最高性能のHBMを開発し、デジタル化社会の 成長に貢献

- ビッグデータ・AIを活用したサイバー空間技術、次世 代モビリティの社会実装に向けた取り組みにも貢献

## CXL 3Dメモリ向けメモリアレイ技術の研究開発

### 実施者

#### キオクシア株式会社

#### 概要

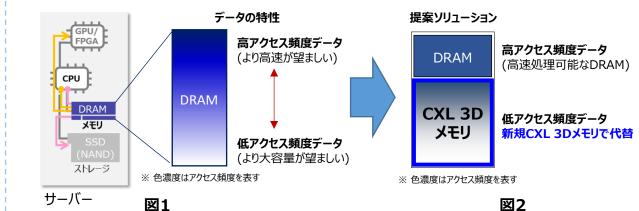

ポスト5G時代では生成されるデータが極めて大量となるため、データセンターでは処理データ量が増加し、電力消費量が増大してしまう。一方、データセンターで処理データの格納に主に使われているのはデータアクセス頻度に依らず高速なDRAMであり、ビット密度が低く、リフレッシュサイクルが短いため消費電力が大きいという課題がある。

本プロジェクトでは、これらの課題を解決する可能性のある「CXL 3Dメモリ」の実現に向けて必要なメモリアレイ技術の開発を行う。「CXL 3Dメモリ」は、CXL メモリ向けの、DRAMの課題を解決する低消費電力化、高ビット密度化が実現できるメモリであり、活用されることでデータセンターのメモリ利用効率の改善と消費電力の抑制を進めることが可能な革新的なメモリである。

#### 現在のデータセンターと課題

#### 課題解決に向けた技術開発

#### CXL 3Dメモリの狙う領域

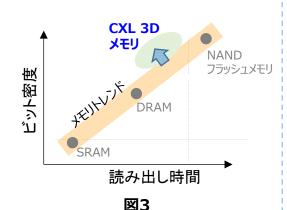

データセンターのメモリはアクセス頻度に差があるが、 低アクセス頻度のデータに対しても高速なDRAMを 使っており、ビット密度が低いため効率が悪く消費電 力が大きくなる。データ量が激増する将来はさらに大 きな問題となる。 DRAMよりも低消費電力・高ビット密度で、 NANDよりも読み出し速度の速いメモリを開発 することで、データセンターでのアクセス頻度に応 じたメモリを供給可能となり、メモリ利用効率の 改善と消費電力の抑制が実現できる。 従来のメモリではビット密度と読み出し時間に普遍的なトレンドが示されるが、このトレンドを超えて、かつ低消費電力性を兼ね備える革新的なメモリである。

## エッジ端末AI向けDRAMの革新的エネルギー効率改善を実現する製造技術の開発

#### 実施者

マイクロンメモリ ジャパン株式会社

概要

AIの需要拡大にともない大量のデータを処理可能な高性能なメモリが必要不可欠になる。AIはハイエンドのAIサーバーに限らず、今後はエッジ端末へも急速に普及が拡大し、バッテリー寿命と機器の発熱を考慮して、SoCを含めた半導体の超低消費電力、高性能化、低コスト、大容量化を可能にする製造技術を開発することが重要となる。本事業では、DRAMのメモリ製造技術のパラダイムシフトを可能とし、革新的なDRAMの開発を行い、社会に必要なエコシステムの構築と拡大に貢献することを目的とする。具体的には、データ伝送のエネルギー効率を改善するLPDRAM(1)を開発する。並行して、エッジ端末の幅広いニーズに対応するためにメモリのエネルギー効率を改善する広帯域LPDRAM(2)を開発する。

|                                    | 本事業で開発するLPDRAM(1)<br>(最大ピーク時の帯域を重視) | 本事業で開発するLPDRAM(2)<br>(常時の帯域を重視) |

|------------------------------------|-------------------------------------|---------------------------------|

| プロセッサーメモリ間のデータ伝送時のエネルギー効率 (pJ/bit) | 15倍以上改善                             | 同等以上改善                          |

| メモリのエネルギー効率 (pJ/Byte)              | 同等以上改善                              | 40%改善                           |

| 帯域 (GB/s)                          | >500 (ピーク時、室温)                      | >200 (フルタイム、高温含む)               |

| メモリ密度 (Gbit/mm²)                   | 0.75Gbit/mm2以上                      |                                 |

| メモリ用CMOS性能                         | 伝搬遅延時間35%改善                         |                                 |

|                                    |                                     |                                 |

※ 比較対象はいずれも本事業提案時点の最新製品