# ②先端半導体製造技術の開発

- (f) 次世代半導体設計技術開発

- (f1) 2nm世代半導体チップ設計技術開発

2nm世代半導体技術によるエッジAIアクセラレータの開発

(f2) 自動車用高性能コンピュータ向け最先端SoC技術開発

先端SoCチップレットの研究開発

(f3) 通信用AI半導体設計技術開発

チップレットを活用した次世代通信のためのエネルギー効率の高いAI半導体開発

(f4)チップレット設計プラットフォーム構築に向けた技術開発

チップレット型カスタムSoC設計基盤技術開発

# 2nm世代半導体技術によるエッジAIアクセラレータの開発

### 実施者

技術研究組合最先端半導体技術センター (LSTC)

概要

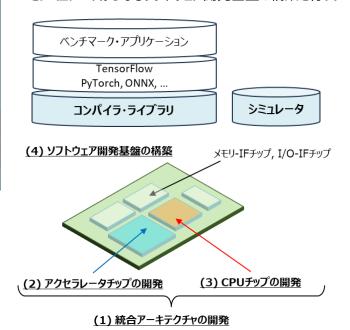

2nm以細を狙う次世代半導体設計技術として、生成AIを含むエッジ推論処理用途に専用化したエッジ AIアクセラレータの開発を国際連携により進める。具体的には、(1) 業界標準に対応したAIアクセラレータ 向け統合アーキテクチャの開発、(2) 2nm技術によるアクセラレータチップの開発、(3) 2nm技術を用いエッジAIに最適化されたCPUチップの開発、(4) 業界標準のAIフレームワークを利用可能なソフトウェア開発基盤の構築を行う。

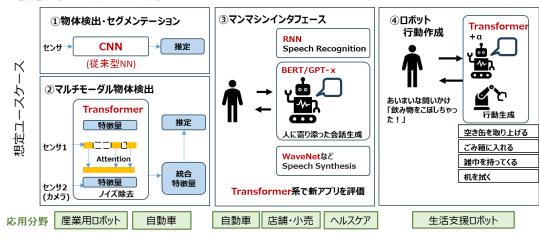

### 【想定するユースケース】

生成AIを含むエッジ推論用途に専用化したエッジAIアクセラレータによる、産業用ロボット、自動車、店舗・小売り、ヘルスケア、生活支援ロボットでのインターフェース高性能化、制御等を想定するユースケースとする。

# 【本プロジェクトの強み】

- これからの需要が見込まれる生成AIを含むエッジ推論処理用途に専用化することにより、 ニーズに即した回路技術を開発する。

- テクノロジー・回路設計の協調により、2nmデバイス技術の有効性を最大限に活用する。

- RISC-VエコシステムによるCPUチップ技術を活用するとともに、業界標準であるオープンソースソフトウェア環境をシームレスに利用できるソフトウェアスタックを提供する。

# 【実施内容】

アクセラレータチップとCPUチップからなるアクセラレータの 統合アーキテクチャの開発、並びに2nm技術によるアク セラレータチップ・CPUチップの開発、コンパイラ・ライブラリ とシミュレータからなるソフトウェア開発基盤の構築を行う。

LSTC組合員:産業技術総合研究所、Rapidus、東京大学国際連携:Tenstorrent Inc.

# 先端SoCチップレットの研究開発

実施者

自動車用先端SoC技術研究組合(ASRA)

概要

自動車のさらなる知能化・電動化を支える車載ハイパフォーマンス・コンピュータ実現のためには、データセンタなど 民生半導体で実績ある『チップレット技術』を車載応用する研究開発が必須である。車載固有の安全・信頼 性確保のため、機能安全対応や熱・ノイズ・振動、リアルタイム処理などの課題解決を行う必要がある。自動車 メーカからECU・EDA・SoCベンダまで縦連携の共同研究体制により、車載課題を解決するチップレットの要素 技術を確立する。これらの技術をベースとするSoCを2030年以降の自動車に量産適用することを目指す。

■開発内容 車載SoCにおける嬉しさ(左表)を、技術(右表)の研究開発により実現する。 ECU: Electronics Control Unit

EDA: Electronic Design Automation

TTM: Time To Market PCB: Printed Circuit Board

#### ■ チップレットをベースとする車載Socの嬉しさ

#### 嬉しさ 概要 同一チップレットの複数配置や、最先端AIチップの 接続により、バリエーション対応や高性能化が可能 【バリエーション対応の例】 ハイエンド パッケージ ローエンド ミッドレンジ ①多数の レット バリエーション パッケージ パッケージ への対応 や高性能化 【高性能化の例】 (開発コスト・ ベースSoC 高性能SoC TTMの低減) 最先端AI ベース演算SoC ベース演算SoC アクセラレータ (チップレット) (チップレット) (チップレット) SoCダイを小さく分割することで、 歩留まりを向上させ、コスト低減が可能 ② チップコスト 分割 の低減 SoC チップ

### ■ チップレットをベースとする車載SoCに必要な技術開発

| 技術                                        | 概要                                                          |            |                |

|-------------------------------------------|-------------------------------------------------------------|------------|----------------|

| ①複数のダイ<br>(チップレット)<br>の境目を隠蔽する<br>HW/SW技術 | アプリケーションからダイの境界を隠蔽する<br>HWレベルコヒーレンシ、OS/Driver層、ミドルウェア/開発ツール |            |                |

| ②機能安全・<br>リアルタイムを<br>実現する<br>HW/SW技術      |                                                             | 従来技術(PCle) | チップレット技術(UCle) |

|                                           | 接続箇所                                                        | PCB上       | パッケージ内         |

|                                           | レイテンシー                                                      | 150ns程度    | 20ns程度         |

|                                           | キャッシュコヒーレント対応                                               | 不可         | 可              |

|                                           | モノリシックと変わらないリアルタイム性能を<br>実現する高速・高信頼データ転送技術                  |            |                |

| ③ 車載信頼性<br>技術                             | ままれて ままれて ままれて ままれて ままれて ままれて ままれて ままれて                     |            |                |

# チップレットを活用した次世代通信のためのエネルギー効率の高いAI半導体開発

### 実施者

### EDGECORTIX株式会社

【プロジェクト2:SAKURA-X 完全DU (High PHY) アクセラレーターの開発】

#### 概要

5Gおよび5G Advancedネットワークは、超高速通信、低遅延、大量のデバイス接続を提供することで、産業や社会全体にわたるデジタルトランスフォーメーションを推進している。しかし、エッジコンピューティングとクラウド環境の展開および運用においては、依然として課題が残っている。これらの問題に対処するために、AI-RAN (AI統合無線アクセスネットワーク)が有望なソリューションとして注目されつつあるが、現在のAI-RANシステムは依然として高消費電力と高コストの課題に直面している。本プロジェクトは、AI処理とRANアクセラレーションを統合するSAKURA-Xと呼ぶチップレットベースのアーキテクチャを採用することで、これらの課題に取り組む。既存のソリューションと比較して、消費電力を大幅に削減し、計算効率を5倍以上向上させることを目指している。EdgeCortixの実績のあるAIプロセッサ技術とRANアクセラレータIPを基に、パフォーマンスの最適化とエネルギー使用量の最小化を、高度な電力管理と協調設計戦略により実現する。最終的なシステムは、次世代5Gの仮想O-RAN環境に展開され、生成AIアプリケーションと低消費電力の分散型ユニット(DU)アクセラレーションの両方を同一ハードウェア上でサポートし、最高水準の電力効率とインフラコストの削減を実現する。

#### 【プロジェクト1:SAKURA-X AIおよび部分DUアクセラレーター開発】 【プロジェクト3: O-RANシステム内のSAKURA-X AI-DU 統合アクセラレータの実証 】 最大1600 TOPS (Int8)のAIパフォーマンス プロジェクト1、2開発成果をつなげて、 EdgeCortix DNA-X 統合アクセラレーションを30W以内で実現 最終的なSAKURA-X AI処理およびDUチップレ RISC-V NPU プロジェクト1 プロジェクト1 クラスタ ットは、1つのパッケージに複数のダイとして統合さ 開発 開発 SRAM 低性能・低消費電力 高性能・低消費電力 れ、エネルギー効率の高いAI-RANアプリケーショ ネットワークオンチップ ンを実現します。 EDGECORTIX 5G LDPC **CTRL** プロジェクト1 プロジェクト1 ェ UCle PCle Serdes ネ コアネットワーク 性 能 CU - 集中型ユニット → Die-to-Die接続 現在の 現在の AI-RAN AI-RAN 低性能・高消費電力 高性能・高消費電力 UCle Subsystem 低 プロジェクト1 パフォーマンス RISC-V 無線ユニット フル DU CPU 🔳 アクセラレーション 開発 完全インラインDU クラスタ NIC PMU **(レイヤ−1)** 独自のプログラム可能なアーキテクチャを備えたシリコン 高 PHY ((x)) SAKURA-X アクセラレーション スタック 実証済みのDNA-Xにより、SAKURA-Xは競合するAI-Accelerator ネットワークオンチップ プロジェクト2 RANソリューションよりも5倍以上の電力効率を実現できる。 開発 メモリ DU - 分散型ユニット

# チップレット型カスタムSoC設計基盤技術開発

#### 実施者

技術研究組合最先端半導体技術センター(LSTC)

### 概要

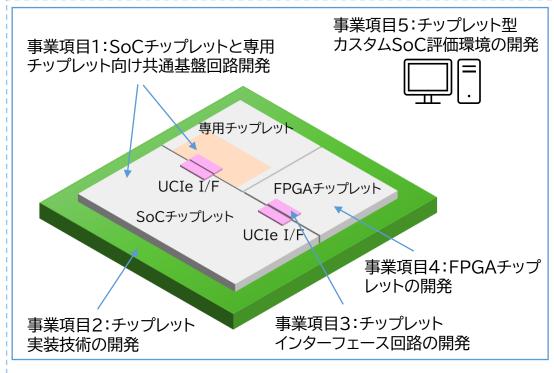

近年、カスタムSoCは、エンターテインメント、モビリティ、IoT、工場、ロボット、医療など、さまざまな産業分野を支える不可欠な電子部品となっている。しかし、半導体製造技術の微細化が進むなか、工業用ロボット、産業機械、医療機器といった出荷数量の限られた製品セクターでは、初期コストの増大や開発期間の長期化が課題となり、カスタムSoCの導入が困難になりつつある。本プロジェクトでは、我が国の産業系システムメーカー、サービスプロバイダ、ファブレスメーカーにおけるカスタムSoCの自主開発の促進を目指し、チップレット技術を活用したカスタムSoC設計基盤の構築に取り組む。

LSTC組合員:產業技術総合研究所、東京大学

再委託先:キュリアス株式会社、ナノブリッジ・セミコンダクター株式会社、 ミラクシア エッジテクノロジー株式会社、富山県立大学、信州大学

# 【開発内容】

産業系システムメーカーやサービスプロバイダ、ファブレスメーカーにおけるカスタムSoCの自主開発を活発化するために、SoCチップレット、専用チップレット向け共通基盤回路、チップレット実装技術、チップレットインターフェース回路、FPGAチップレット、基盤ソフトウェア等の要素技術開発を実施し、これらの成果を統合することによってチップレット技術を応用したカスタムSoC設計基盤技術を開発する。

### 【期待される効果】

従来の設計 手法

チップレット 技術活用の 設計手法 チップ全体設計が必要

自社チップレット のみ設計 購入