Development of Technology for Building a Chiplet Design Platform

Project overview

It is essential to process information at the network edge in order to advance digitization technology toward the realization of Society 5.0. For AI semiconductors to be used in information processing, there has been an acceleration of efforts, including standardization mainly in the United States, to develop a technology called a chiplet* in order to suppress the increase of design and manufacturing costs with maintaining high performance as one of the post-Moore technologies. It has become necessary for Japan to take immediate action as well.

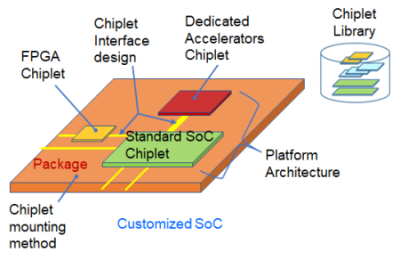

As this project closely monitors the standardization trend of chiplet technology in the world, it promotes technological development for the establishment of chiplet design platform to easily realize semiconductors that achieve both performance and low-cost and aims to make it a fundamental technology that can be widely used by private enterprises and other entities. In addition, the project develops AI semiconductor chips that can be mounted on the customized SoCs of chiplet-type, and pursues reliable applications in society.

Platform of chiplet-type and R&D elements of the Project

*Chiplet technology is a technology that packages together as a single chip by dividing the CPU, GPU, accelerator, and other components, composing an integrated circuit into multiple chips, manufacturing each chip using an optimized process, and combining them. Compared to the conventional manufacturing method, where integrated circuits are manufactured on a single chip using the same process, it is expected to result in both cost reduction and high-performance.

Research and Development

(1) Development of Fundamental Technology for the Customized SoC Design of Chiplet-type

NEDO will select an implementer to develop fundamental technology for the customized SoC design of chiplet-type, and launch into the research process. At the start of the research, this project will investigate the latest trends in domestic and international technologies and standards related to chiplet technology.

Basic information

| Technical field | Networks and computing |

|---|---|

| Project code | P23009 |

| Department in charge | Internet of Things Promotion Department (TEL: +81-44-520-5211) |

Last Updated : December 26, 2023