チップレット設計基盤構築に向けた技術開発事業

事業・プロジェクト概要

Society5.0の実現に向けてデジタル化技術を進展させるためには、エッジでの情報処理が不可欠です。情報処理に活用するAI半導体として、高い性能を維持しつつ設計・製造コストの増加を抑制する、ポストムーア技術の一つとしてチップレット※と呼ばれる技術への取組が標準化を含め米国を中心に加速しており、日本としても早急な対応が必要になってきています。

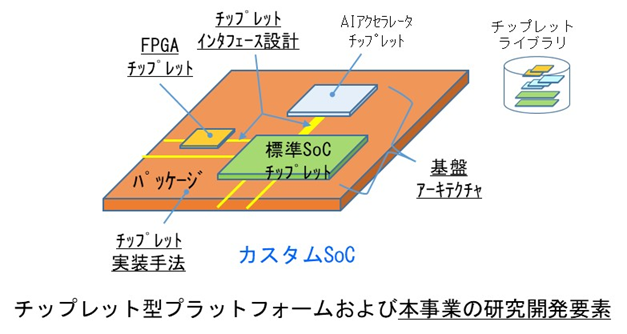

本事業では、世界のチップレット技術の標準化動向を注視しつつ、性能とコストを両立する半導体を容易に実現するためのチップレット設計基盤構築に向けた技術開発を進め、民間企業等が広く活用できる基盤技術となることを目指します。加えて、チップレット型カスタムSoCにも搭載可能なAI半導体チップを開発し、確実な社会実装を目指します。

- チップレット技術とは、集積回路を構成するCPUやGPU、アクセラレータ等について、機能ごとの複数のチップに分割、それらチップをそれぞれ最適なプロセスを使って製造しそれらを組み合わせて一つのチップとしてパッケージ化する技術で、集積回路を同一プロセスで一つのチップ上で製造する従来製法と比較して、コスト低減と高性能動作の両立が可能とみられている。

研究開発内容

(1)チップレット型カスタムSoC設計基盤技術開発

チップレット型カスタムSoC設計基盤技術を開発する実施者を選定し、研究を開始します。研究開始に際し、チップレット技術に関する国内外の技術や規格の最新動向を調査します。

基本情報

| 事業期間・予算額 | 2023年度~2027年度、予算額:5億円(2023年度) |

|---|---|

| 技術・事業分野 | 情報インフラ |

| プロジェクトコード | P23009 |

| 担当部署 | IoT推進部 (TEL:044-520-5211) |

詳細資料

最終更新日:2024年3月8日

関連ページ

- 情報インフラ

- 同分野のニュースリリースを探す

- 同分野の公募を探す

- 同分野のイベントを探す