複数のAIアクセラレータを搭載した評価チップの設計を完了、試作を開始

―短期間で低コストのAIチップ設計・評価手法の確立へ―

2021年5月10日

NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)

国立研究開発法人産業技術総合研究所

国立大学法人東京大学

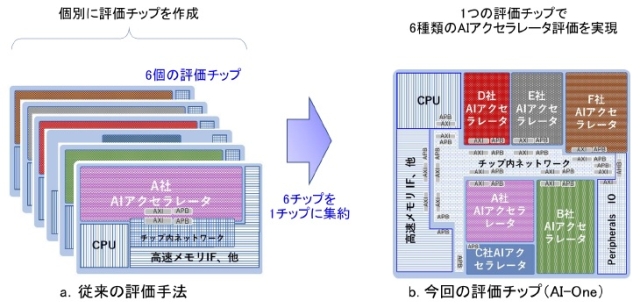

NEDOはAIチップ開発加速のためのイノベーション推進事業に取り組んでおり、産業技術総合研究所、東京大学と共同で、ネットワークの端末などに使われるエッジ向けAIチップの設計を容易にするために、AIチップに使用されるAIアクセラレータ開発のための評価プラットフォームの構築を進めています。このたび、本評価プラットフォームの実証のため、仕様が異なる6種類のAIアクセラレータを同一チップに搭載した評価チップの設計を完了し、外部の製造会社で試作を開始しました。

本評価プラットフォームを使うことにより、AIチップを開発する中小・ベンチャー企業などは、東京大学浅野キャンパス(東京都文京区)内に整備を進めている「AIチップ設計拠点」で、各企業が設計したAIアクセラレータ搭載の独自なAIチップを擬似的に作成できるため、短期間(従来比45%以下)に低コストでAIチップの設計と評価が可能になります。

1.概要

目覚ましく進展するIoT社会において、実世界のビッグデータから人々の生活に新たな価値を創造する鍵として人工知能(AI)技術が注目されています。一方、AI技術の根幹をなす半導体集積回路では、微細化が物理的な限界に近づいていること、エネルギー消費が増大し続けることが極めて大きな課題となっています。この課題を解決するためには、省エネルギーで効率的にAIを動作させる半導体集積回路・デバイス(AIチップ)の開発が必要不可欠であり、世界的にもAIチップの開発競争が激化しています。

日本国内においては、多くの中小・ベンチャー企業などが台頭し、AIチップの開発に名乗りを上げています。しかし、AIチップの開発には、半導体を設計するための高度な技術が求められると共に、高額な回路設計ツールや検証装置などをそろえる必要があり、中小・ベンチャー企業などが自らのアイデアをチップ化に結びつける大きな壁になっています。

このような背景のもと、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)は、AIチップ開発加速のためのイノベーション推進事業※1において、国立研究開発法人産業技術総合研究所(産総研)、国立大学法人東京大学(東京大学)と共同で、東京大学浅野キャンパス(東京都文京区)内の武田先端知ビルに AIチップ設計拠点として、半導体設計に必要な共通基盤技術の開発や回路設計ツール用のEDAツール※2や標準IPコア※3などからなる設計環境の整備を進めています。

AIチップ設計拠点として、半導体設計に必要な共通基盤技術の開発や回路設計ツール用のEDAツール※2や標準IPコア※3などからなる設計環境の整備を進めています。

この一環として、本AIチップ設計拠点ではアルゴリズムを実行するエンジンとして中小・ベンチャー企業などが開発する独自のAIアクセラレータ※4向け評価プラットフォーム※5の構築を進めています。開発されるAIアクセラレータを実環境で評価するには、そのAIアクセラレータと標準システム回路を有するSoC※6、いわゆるAIチップを開発し、それを用いてシステムレベルでの評価を行う必要があります。本評価プラットフォームは、共通基盤技術として標準システム回路、検証回路、テスト回路、および評価ボードなどを開発し、中小・ベンチャー企業などにこれら共通技術をAIアクセラレータ向け評価プラットフォームとして提供することで、各企業独自のAIアクセラレータ搭載チップの開発とそれを用いたシステムレベルでの評価を短期間に実現することを目指します。

このたび、本評価プラットフォームの実証として中小・ベンチャー企業の協力※7を得て、6種類の独自AIアクセラレータを搭載したCMOS※828nmプロセスを用いる評価チップ(AI-One)の設計を完了し、外部の製造会社にて試作を開始しました。

なお産総研は、2021年5月10日から11日まで開催されるLSIとシステムのワークショップ2021(主催:電子情報通信学会集積回路研究専門委員会)において、AIチップ設計拠点についての講演の中で本評価プラットフォームと評価用チップ(AI-One)について紹介します。LSIとシステムのワークショップ2021の詳細については、下記をご参照ください。

2.評価プラットフォームの概要

【1】評価プラットフォームの利点

AIアクセラレータ向け本評価プラットフォームを利用することで、以下の利点があります。

- (1)

- AIアクセラレータ開発者は、拠点の設計クラウド上で、自身のAIアクセラレータを本評価プラットフォームに組み込むことで、AIアクセラレータをチップに実装した時の動作周波数・消費電力・性能を、設計段階で見積もることができます。また、AIアクセラレータ以外の部品などは共通部分として提供されるため、チップ全体の設計や時間が短縮できます。それにより、AIチップを短期間(従来比45%以下)で開発することができます。

- (2)

- AIアクセラレータ開発者は、評価プラットフォームが規定するRTLガイドライン※9に沿うことで、AIアクセラレータのシステムレベルでのコンピュータプログラムに潜む欠陥を探し出して取り除くことができます。また、標準システム回路とのインタフェース接続も容易に行えます。

- (3)

- 複数のAIアクセラレータを同一チップ上に集積し、一度に試作することができ、試作コストの大幅な削減が可能です。

- (4)

- AIアクセラレータの設計情報の秘匿性を担保するために、AIアクセラレータのRTL記述を暗号化したままで設計・検証作業を進めることが可能です。

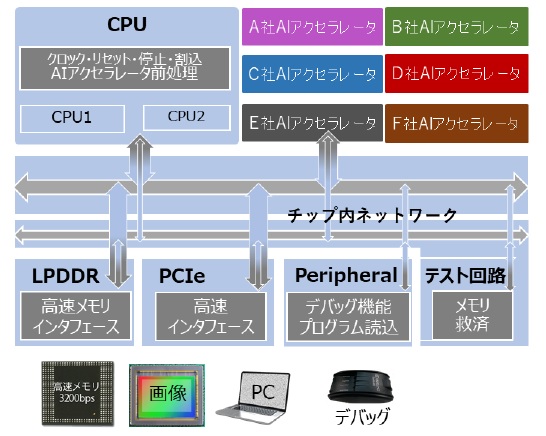

【2】評価プラットフォームに装備した標準システム回路

本評価プラットフォームでは、以下の回路を標準装備しています。

- (1)CPU:

- デュアルコア構成でシステムレベルの評価に必要なLinux※10などのOSやさまざまな応用ソフトを実行します。

- (2)チップ内ネットワーク:

- AIアクセラレータのさまざまなインタフェース要求に対して、チップ内のネットワーク機能を提供します。

- (3)テスト回路:

- チップ内部の論理回路の故障検出や内蔵メモリの故障検出機能を提供します。

- (4)LPDDR:

- 低消費電力DDR(Double Data Rate)型ダイナミックメモリをチップに接続するための高速メモリインタフェース回路です。

- (5)PCIe※11:

- PCなどの標準的な周辺インタフェースPCI Express※113.0に接続するための高速インタフェース回路です。

- (6)Peripheral:

- チップのデバッグ機能やプログラムを読み込むインタフェースです。

-

図2 エッジAI向け評価プラットフォームの基本パーツ

図2 エッジAI向け評価プラットフォームの基本パーツ

3.今後の予定

本事業では今回設計した評価チップ(AI-One)を用いて、設計段階で見積もった各アクセラレータの消費電力や動作周波数などをもとに、2021年9月頃に実チップを搭載したボードで比較評価を行い、アクセラレータの実環境での評価を進めます。そのフィードバックを活用してさらに使いやすいエッジ向けAIチップの評価プラットフォームとして確立していきます。

また本拠点では、AIチップ設計に関する共通基盤技術などの開発を進め、さらに使いやすいAIチップ設計環境を構築していきます。これらの取り組みにより、AIチップ設計拠点の確立と、日本の中小・ベンチャー企業などのAIチップ開発を後押しします。

【注釈】

- ※1 AIチップ開発加速のためのイノベーション推進事業

- 事業名:AIチップ開発加速のためのイノベーション推進事業/AIチップ開発を加速する共通基盤技術の開発

実施期間:2018年度~2022年度 - ※2 EDAツール

- EDAはElectronic Design Automationの略です。半導体集積回路などの電気系回路設計を自動化・支援・補助するソフトウエアのことです。

- ※3 IPコア

- IPは、Intellectual Propertyの略です。半導体集積回路を構成する部分的な回路情報で、特に機能単位でまとめられているものを指します。

- ※4 AIアクセラレータ

- AIアプリケーション、特にニューラルネットワーク、機械学習をおこなうために開発されたアルゴリズムを実行するエンジン(機能単位)です。

- ※5 評価プラットフォーム

- (1)半導体チップを設計する手法、(2)チップの利用目的に合わせた標準システム回路、(3)仕様で定められた半導体製造条件に合った設計ツールの使用方法、の組み合せです。今回は、エッジAI向けの半導体チップを28nmプロセスでの製造条件で設計する手法や標準システム回路などを組み合わせています。

- ※6 SoC

- System on Chipの略です。一個の半導体チップ上にシステムの動作に必要な機能の多く、あるいは全てを実装する設計手法を使って作られた半導体チップです。

- ※7 中小・ベンチャー企業の協力

- 本活動では以下の5社より協力を得ています。

株式会社アクセル、株式会社ディジタルメディアプロフェッショナル、株式会社プリバテック、LeapMind株式会社、株式会社ロジック・リサーチ。 - ※8 CMOS

- 相補型金属酸化膜半導体(Complementary Metal Oxide Semiconductor)とは、pチャネルとnチャネルのMOSトランジスタを相互に補うように接続した基本回路素子です。

- ※9 RTLガイドライン

- AIアクセラレータのインタフェース仕様とAIアクセラレータの回路記述であるRTL記述に構造違反がないか検証するEDAツールの使い方を記載したものです。なおRTLとは、レジスタ転送レベル(Register Transfer Level)の略で、論理回路をハードウェア記述言語で記述する際の手法です。

- ※10 Linux

- 世界で最も普及している、オープンソースのオペレーティングシステム(OS)。いわゆるUNIX系OSの一種で、プログラムが公開されており誰でも自由に入手や使用、改変、再配布することができる。(出典:株式会社インセプト

IT用語辞典より、なおLinuxはLinus Torvaldsの登録商標です)

IT用語辞典より、なおLinuxはLinus Torvaldsの登録商標です) - ※11 PCIeおよびPCI Express

- PCIeおよびPCI ExpressはPCI-SIGの登録商標です。

4.問い合わせ先

(本ニュースリリースの内容についての問い合わせ先)

NEDO IoT推進部 担当:芹澤、久保田、波佐 TEL:044-520-5211

産総研 エレクトロニクス・製造領域 担当:内山 TEL:03-5841-8460

東京大学大学院工学系研究科附属システムデザイン研究センター(東京大学 d.lab)

基盤設計研究部門長:池田 TEL:03-5841-6561

(AIチップ設計拠点についての問い合わせ先)

AIチップ設計拠点 TEL:03-5841-8460 E-mail:aidc-ml@aist.go.jp

(産総研 広報に関する一般的な問い合わせ先)

産総研 広報部 報道室 TEL:029-862-6216 E-mail:hodo-ml@aist.go.jp

(その他NEDO事業についての一般的な問い合わせ先)

NEDO 広報部 担当:坂本、橋本(就) TEL:044-520-5151 E-mail:nedo_press@ml.nedo.go.jp

関連ページ

- ネットワーク/コンピューティング

- 同分野のニュースリリースを探す

- 同分野の公募を探す

- 同分野のイベントを探す